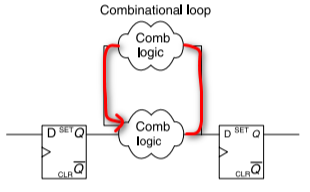

什么是组合逻辑环路?

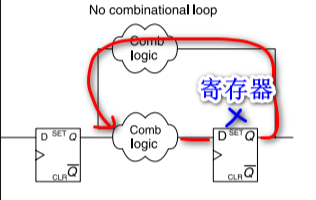

组合逻辑环路(Combinational Loops):指组合逻辑的输出信号不经过任何时序逻辑电路(FF等),而直接反馈到输入节点,从而构成的电路环路。

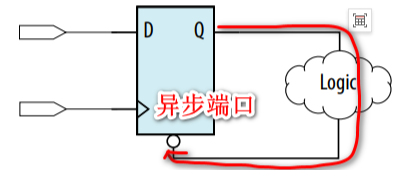

此外,如果直接将寄存器的输出端通过组合逻辑反馈到该寄存器的异步端口(异步复位或异步置位),也会形成组合逻辑环路。

为什么要避免组合逻辑环路?

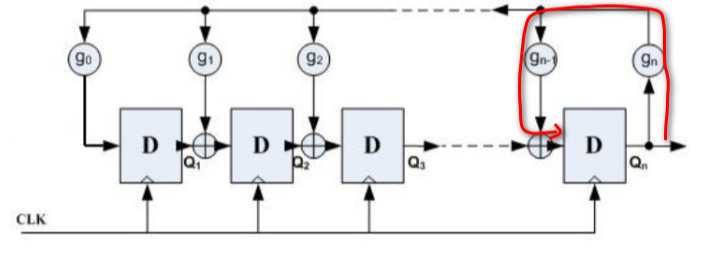

在FPGA设计中,绝大多数的应用场景都不需要使用组合逻辑环路,我暂时能想到的例外只有随机数发生器(评论区可以补充一下)。

在实践中,避免使用组合逻辑环路主要是因为它的特性所导致的危害:

1. 组合逻辑环路违反了同步设计原则,容易振荡,从而导致整个设计不稳定和不可靠。

2. 组合逻辑环路的行为功能取决于该环路上的延迟(逻辑延迟和布线延迟),一旦延迟发生变化,整个设计的行为功能将变得无法预测。

3. 组合逻辑环路的振荡将导致EDA软件做无穷无尽的计算。为了完成这种计算,EDA软件将会切割环路。不同的EDA软件的切割方式不尽相同,这可能会与设计者的设计目的相违背,从而导致逻辑功能错误。

4. 组合逻辑环路无法进行静态时序分析(STA),可能会出现时序违例,或者导致STA过程时间过长。

什么情况会导致组合逻辑环路?

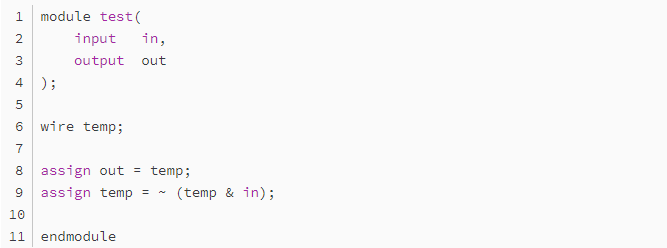

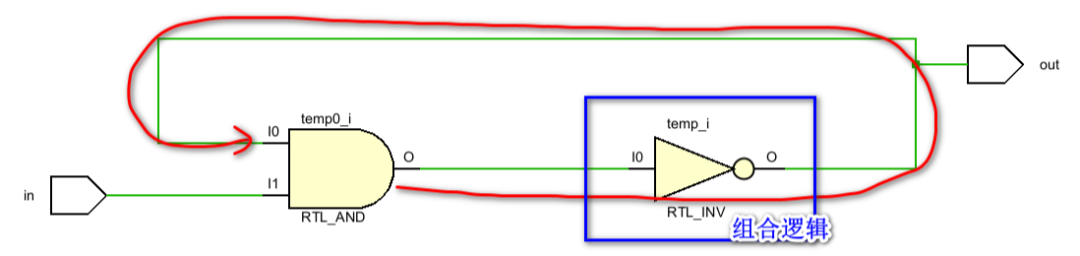

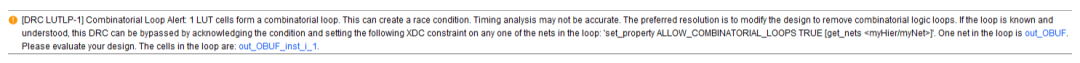

情况1:组合逻辑的输出信号仅经过组合逻辑电路后又反馈到了输入节点。比如下面的代码:

这样的设计在Vivado中不会报错,但会报严重警告(Critical warning)。

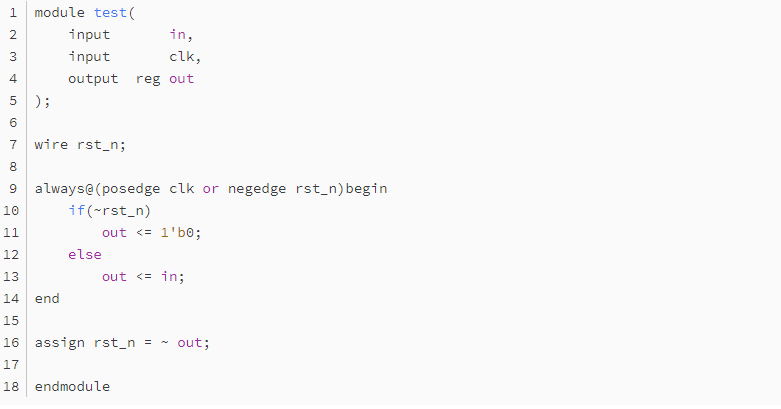

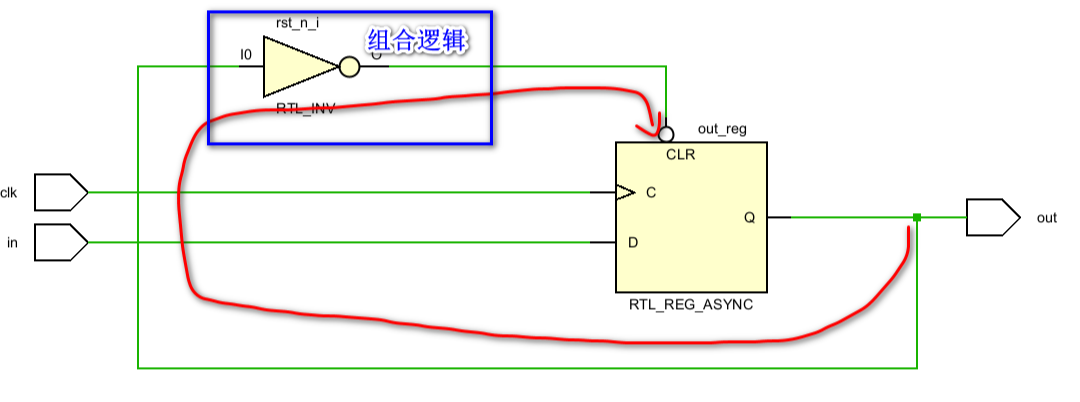

情况2:寄存器的输出端通过组合逻辑直接反馈到该寄存器的异步端口(异步复位或异步置位)。 比如下面的代码:

这种情况所导致的组合逻辑环路在实践中还是比较少出现的,因为一般情况下,寄存器的异步端口都是直接由模块外部连接的信号所驱动。

如何处理组合逻辑环路?

最重要的一点:一定要坚决避免组合逻辑环路!现在的EDA工具基本上都可以把组合逻辑环路识别出来,并报错或者报警告。写完RTL代码后请一定要记得看EDA工具的报告的错误和警告信息Message!

组合逻辑环路的避免首先应该通过良好的编码习惯来避免。上述的两种示例代码就是典型的错误,请不要在设计中使用类似的代码。

如果出现了组合逻辑环路且当前设计修改困难,那么请修改你的RTL代码--通过添加寄存器的方式来切断反馈回路。就像这样:

如果组合逻辑环路的出现是符合预期设计目的的(比如随机数发生器),想将其保留该如何操作? 只要在XDC约束文件中添加这一句即可:

表示反馈回路上的一个节点,一般EDA工具都会指出这个节点,设计者只要复制替换就好了。

什么是语言模板?

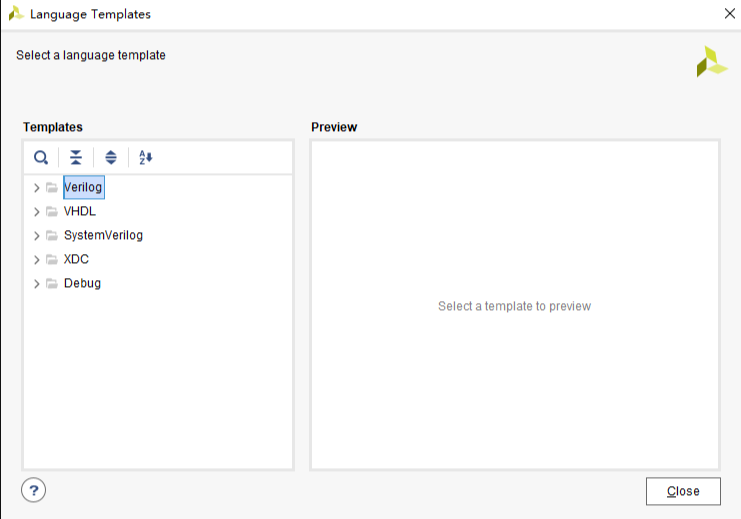

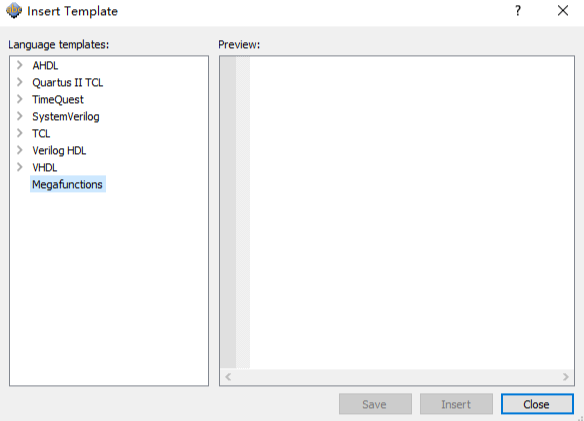

不论是Xilinx的Vivado,还是Altera的Quartus II,都为开发者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原语、XDC约束等相关的语言模板(Language Templates)。

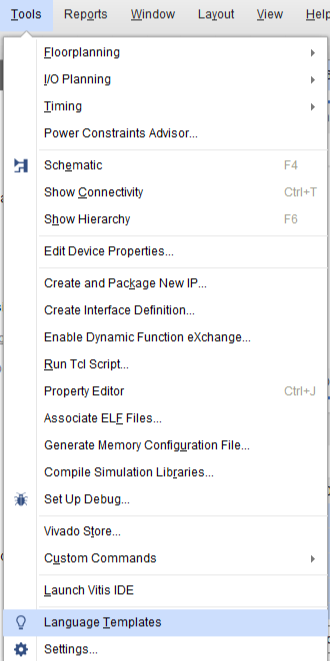

在Vivado软件中,按顺序点击Tools----Language Templates,即可打开设计模板界面。

在Quartus II软件中,需要设计文件(.v文件等)的需要处点击右键,然后点击Inset Templates,即可打开模板界面。

设计模板有什么用?

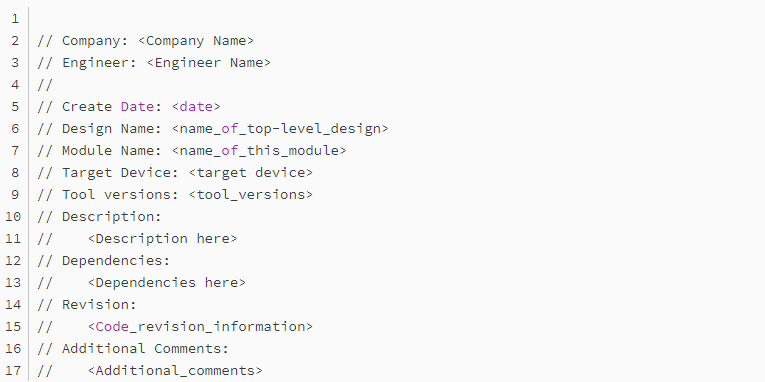

语言模板的内容还是非常丰富的,比如你可以看看xilinx推荐的文件头是什么样的:

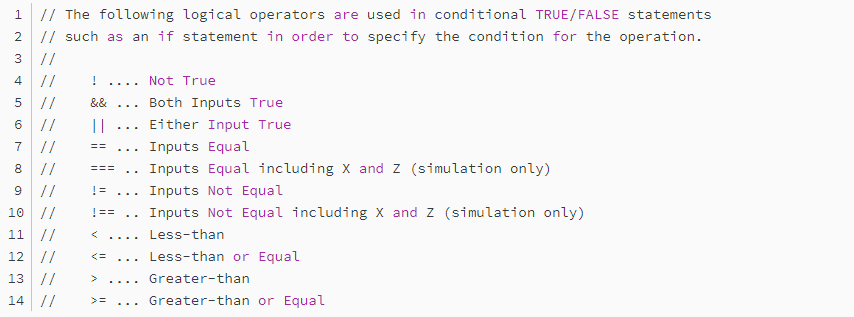

Verilog语法(逻辑运算符):

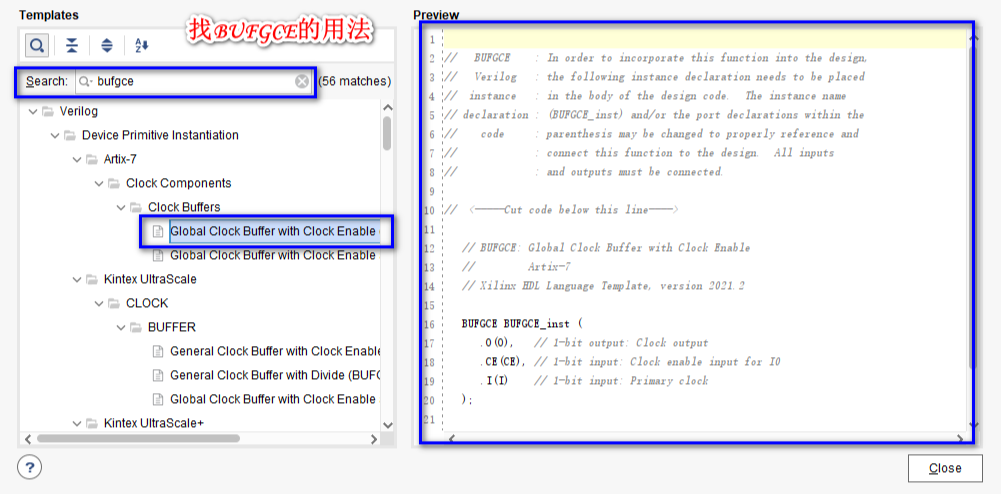

找不到原语使用方式的时候,也可以来这里查找(当然你也可以查xilinx的官方文档):

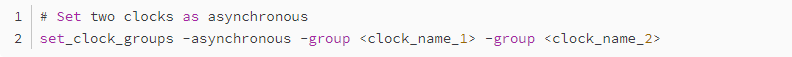

有些时序约束语法不太好记,你可以用这个工具查找,比如:

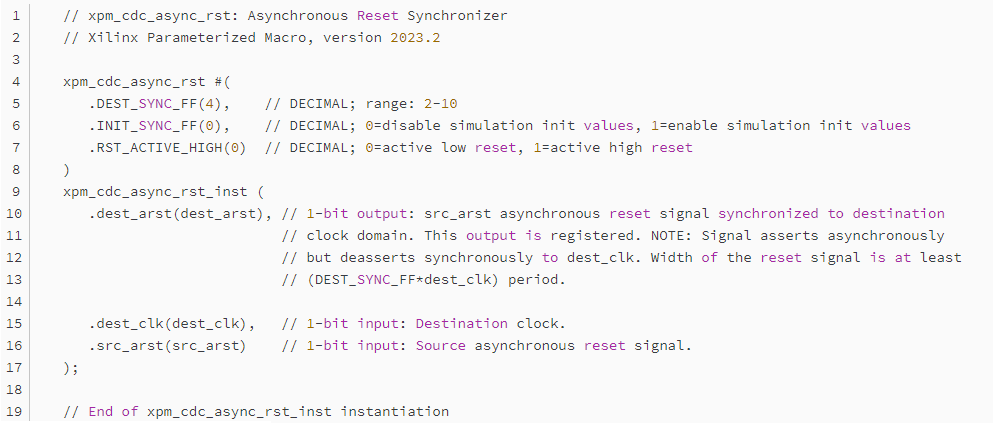

看看xililnx提供的宏XPM(Xilinx Parameterized Macro)是怎么用的,比如CDC这部分的:

最最重要的一点是,它提供了很多典型电路的设计方法。

由于各家FPGA的结构差异,可能相同的代码在不同的器件上生成的结构会存在很大差异。比如有时候,可能你想设计的是一个分布式DRAM,但是由于你的代码风格和综合工具的原因,它给你生成的事BRAM,那这样就和你的设计初衷相违背了(当然随着综合工具的发展,这类情况是越来越少了)。所以在设计相关电路时,请尽量参考xilinx提供的代码,以确保vivado能正确生成你想要的电路(Altera 的FPGA类似)。

总 结

● 语言模板可以学习HDL语言语法、综合属性等;

● 语言模板可以快速查找设计内容、模板;

● 语言模板提供的电路设计模板可以保证综合工具能正确推断出对应的电路。

1

1