其代码如下:

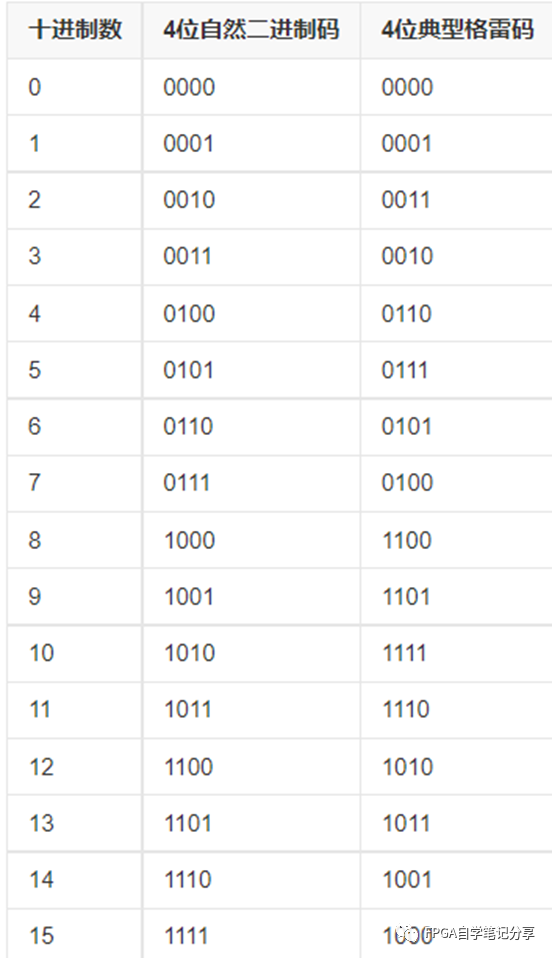

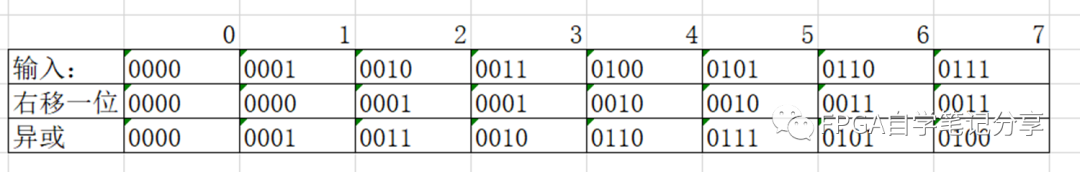

//============================================================// File Name: cm_bin2gray// VERSION : V1.0// DATA : 2022/10/2// Author : FPGA干货分享// ============================================================// 功能:二级制编码转格雷码// // 原码:b[0~n];格雷码:g[0~n](n∈N);编码:g=G(b);解码:b=F(g);// 编码:g=b XOR b[i+1](i∈N,0≤i≤n-1),g[n]=b[n];// 解码:b[n]=g[n],b=g XOR b[i+1](i∈N,0≤i≤n-1).// // ============================================================`timescale 1ns/1psmodule cm_bin2gray #( parameter C_DATA_WIDTH = 4 ) ( input wire I_sys_clk , ///输入时钟 input wire [C_DATA_WIDTH-1:0] I_data_bin , ///输入二进制数据 output reg [C_DATA_WIDTH-1:0] O_data_gray ///输出二进制数据 ); // ============================================================// main code// ============================================================ always @(posedge I_sys_clk) O_data_gray <= I_data_bin ^ (I_data_bin >> 1); endmodule

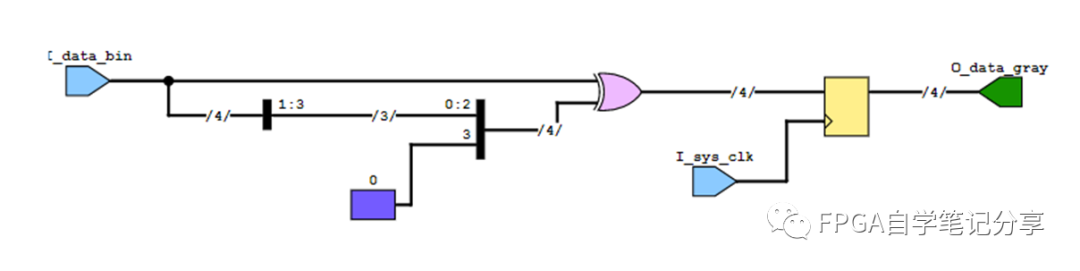

代码综合结果如下:

0

0