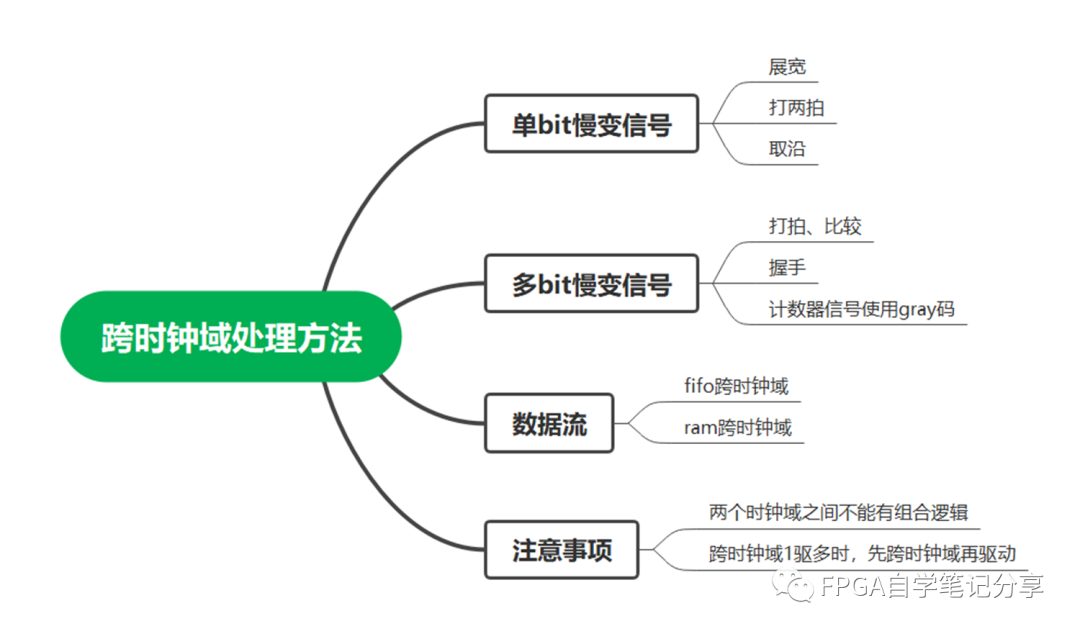

上一篇文章已经讲过了单bit跨时钟域的处理方法,这次解说一下多bit的跨时钟域方法:

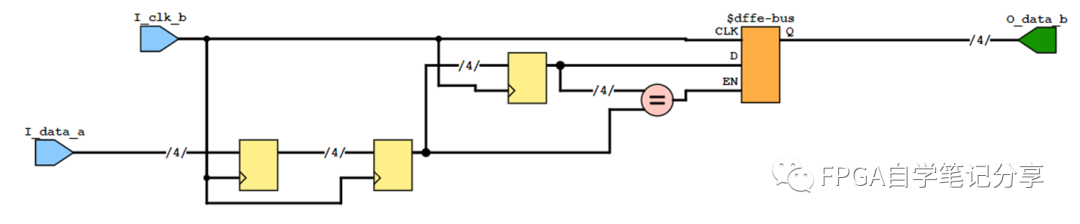

1、打两拍,比较,具体代码如下所示。

// ============================================================// File Name: cm_cdc_4bit// VERSION : V1.0// DATA : 2022/9/28// Author : FPGA干货分享// ============================================================// 功能:4bit慢变信号跨时钟域模块// ============================================================ `timescale 1ns/1psmodule cm_cdc_4bit ( input wire I_clk_a , ///输入时钟a input wire I_clk_b , ///输入时钟b input wire [3:0] I_data_a , ///a时钟输入信号 output reg [3:0] O_data_b ///b时钟输出信号 ); // ============================================================// wire reg// ============================================================ reg [3:0] S_data_b_d0 ;reg [3:0] S_data_b_d1 ;reg [3:0] S_data_b_d2 ; // ============================================================// a时钟域// ============================================================ // ============================================================// b时钟域// ============================================================///使用第二个时钟进行打拍always @(posedge I_clk_b) begin S_data_b_d0 <= I_data_a ; S_data_b_d1 <= S_data_b_d0 ; S_data_b_d2 <= S_data_b_d1 ; end //打两拍之后的信号进行处理always @(posedge I_clk_b) if(S_data_b_d2 == S_data_b_d1) O_data_b <= S_data_b_d2; else O_data_b <= O_data_b ; endmodule

0

0