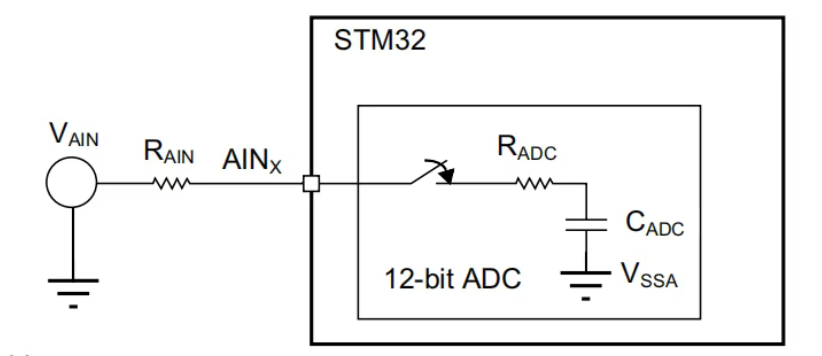

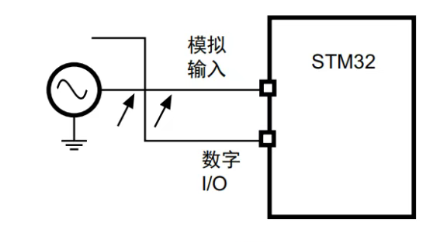

前面分享了ADC自身因素带来的误差,现在再分享一波由于外部因素导致的ADC采样误差。 一、模拟信号源输入减少带来的误差看一个STM32的ADC转换器的示意图:

从图中可以看到,输入源与采样引脚之间存在阻抗RAIN,流入引脚的电压可能因为阻抗的存在产生一定的压降,导致最终输入采样引脚的电压变小。CADC采样电容通过RADC电阻为其充电,如果RAIN的阻抗选取不合理的话,会导致保持电容充满电所需要的时间变长。一般而言,RC的充电的时间常量为:

从图中可以看到,输入源与采样引脚之间存在阻抗RAIN,流入引脚的电压可能因为阻抗的存在产生一定的压降,导致最终输入采样引脚的电压变小。CADC采样电容通过RADC电阻为其充电,如果RAIN的阻抗选取不合理的话,会导致保持电容充满电所需要的时间变长。一般而言,RC的充电的时间常量为:

tc =(RADC+RAIN)× CADC

当采样时间 < 通过RADC + RAIN将CADC充满电所需的时间(ts < tc),则ADC转换的数字值会小于实际值。二、ADC参考电压噪声我们到知道,ADC输出的数字量转换由模拟信号电压与参考电压之比,再根据ADC转换器的位数换算出来的。因此模拟参考的参考电压上的任何噪声都会导致转换后数字输出值的变化。在某些芯片中,VDDA模拟电源会直接用作参考电压(VREF+),因此VDDA电源的质量会直接影响ADC采样转换的误差。例如:当模拟参考电压为3.3 V(VREF+ = VDDA)且采样信号输入为1 V时,转换后的结果为:

(4095/3.3)× 1 = 1240.9 = 0x4D9

然而,如果模拟的参考电压有波动时,采样输出也会被影响。假如参考电压的波动为 40mv时,此时的转换值为:

(4095/3.34)× 1 = 1226 = 0x4CA(VREF+在峰值处)

由此,两者的误差:

误差 = 0x4D9 – 0x4CA = 15

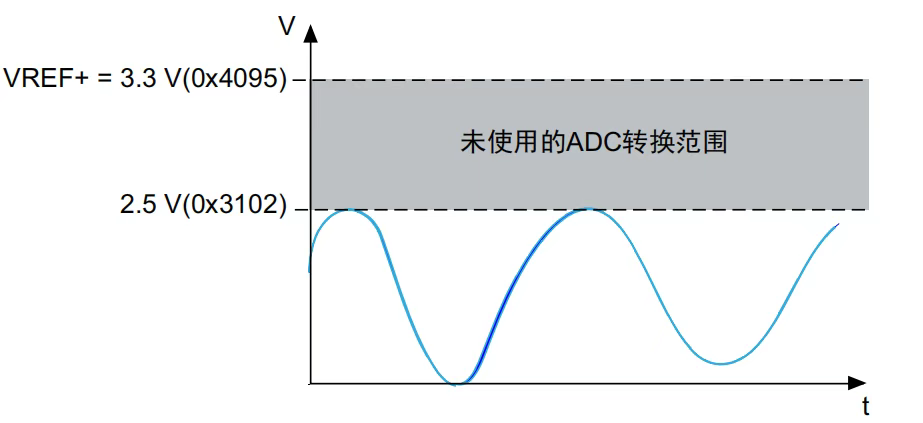

可见,参考电压对ADC采样转换的影响是很大的,稳定的参考电压源很必要。三、采样信号的最大输入值与ADC动态范围匹配不合理正常情况下,为了可以获得最高的 ADC 转换精度,选取的 ADC 动态范围要与待转换的信号最大幅度相匹配。假设待转换信号在 0 ~ 2.5 V之间变化,最大值不会超过2.5V,并且VREF+ 等于3.3 V。ADC转换的最大信号值为 3102 (2.5 V),如下图:

从上图中可以看到,有 993 个未被使用的转换(4095 – 3102 = 993)。这意味着浪费了很多的转换范围(简单而言就是影响了分辨率),转换后信号精度下降。深入分析如下:(1)如果选取的参考电压为 3.3V,则分辨率为:

从上图中可以看到,有 993 个未被使用的转换(4095 – 3102 = 993)。这意味着浪费了很多的转换范围(简单而言就是影响了分辨率),转换后信号精度下降。深入分析如下:(1)如果选取的参考电压为 3.3V,则分辨率为:

3.3/4095 = 0.806mV

(2)如果选取的参考电压为 2.6V,则分辨率为:

2.6/4095 = 0.635mV

两者分辨率之差为:

0.806 - 0.635 = 0.171mV

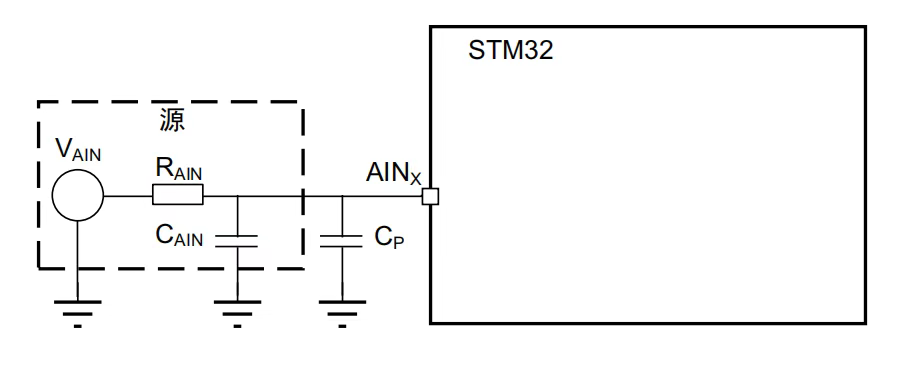

四、ADC采样电路的设计问题正常使用过程中,ADC采样电路中往往会伴随高频/低频干扰信号,所以设计时一般会增加滤波电路以增加输入采样信号的干净度。如下示意:

从上图中可以看到,电阻 RAIN 和 电容 CAIN 组成了RC网络。这部分器件的取值对输入信号是有不同的影响的,如果取值不合理,也是可能会导致ADC转换的结果不准确的。

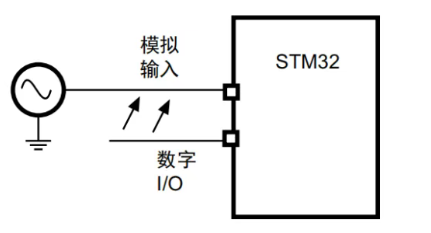

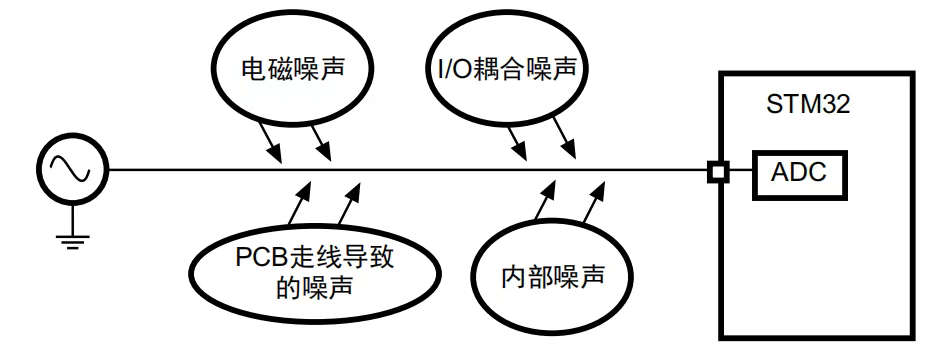

从上图中可以看到,电阻 RAIN 和 电容 CAIN 组成了RC网络。这部分器件的取值对输入信号是有不同的影响的,如果取值不合理,也是可能会导致ADC转换的结果不准确的。五、I/O引脚受外部干扰信号的影响采样电路在设计时就要考虑这个IO附近是否存在高频的信号源存在,如果有高频信号源存在的话,信号变化也会影响采样IO,导致ADC转换结果出现误差。常见的案例如下:(1)内部输出高速的数字信号,IO信号的高速变化会产生高频噪声。比如输出PWM信号的频率高达100KHz以上。

(2)高频信号 IO 与采样 IO 距离很近或者PCB的走线出现交叉,这种情况会出现串扰。

(2)高频信号 IO 与采样 IO 距离很近或者PCB的走线出现交叉,这种情况会出现串扰。

六、PCB板走线设计问题PCB走线是非常重要的,并不是简单的连线接通即可。如果采样电路附近会产生较高的电磁辐射,那就有可能将电磁辐射引入采样,从而产生高频干扰。还有一种现象,就是高速信号与GND两者很近,走线平行,那就很有可能会形成电磁场,从而造成干扰。

0

0