本周的半导体工艺分享计划focus在DRAM这块。为了使得学习更加轻松,文章将尽量简洁,以便大家更容易记忆吸收。阿瞒将花3~5篇文章讲清楚DRAM的工艺流程。在这个过程中,如果大家有什么特别需要了解的知识点也可以评论区留言或者后台私信与阿瞒交流。

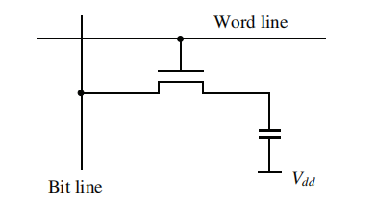

我们知道,DRAM单元包含两个器件:一个n沟道MOSFET(NMOS)作为访问晶体管,一个电容器用于数据存储。

为了克服这些问题,DRAM访问晶体管从平面结构转变为三维结构,并引入了凹槽栅极(Recess Gate)晶体管,以及后来的Buried Word-Line(BWL)技术。

如下图就是三种经典的DRAM array cell NMOS: 其中(a) 是planar DRAM ,(b)是RG DRAM,(c)是BWL DRAM。下文将重点展示三种结构的区别。

Planar DRAM

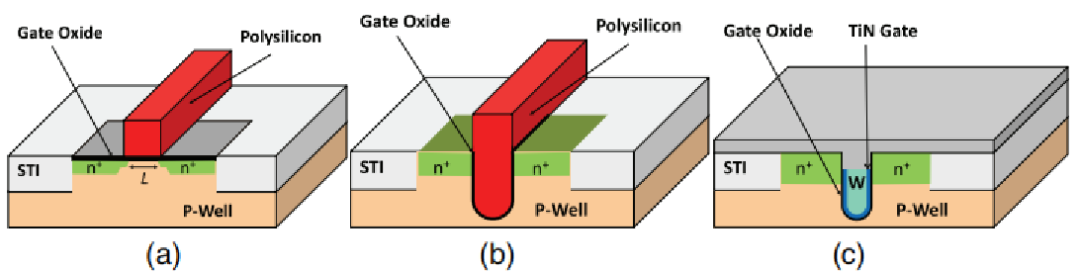

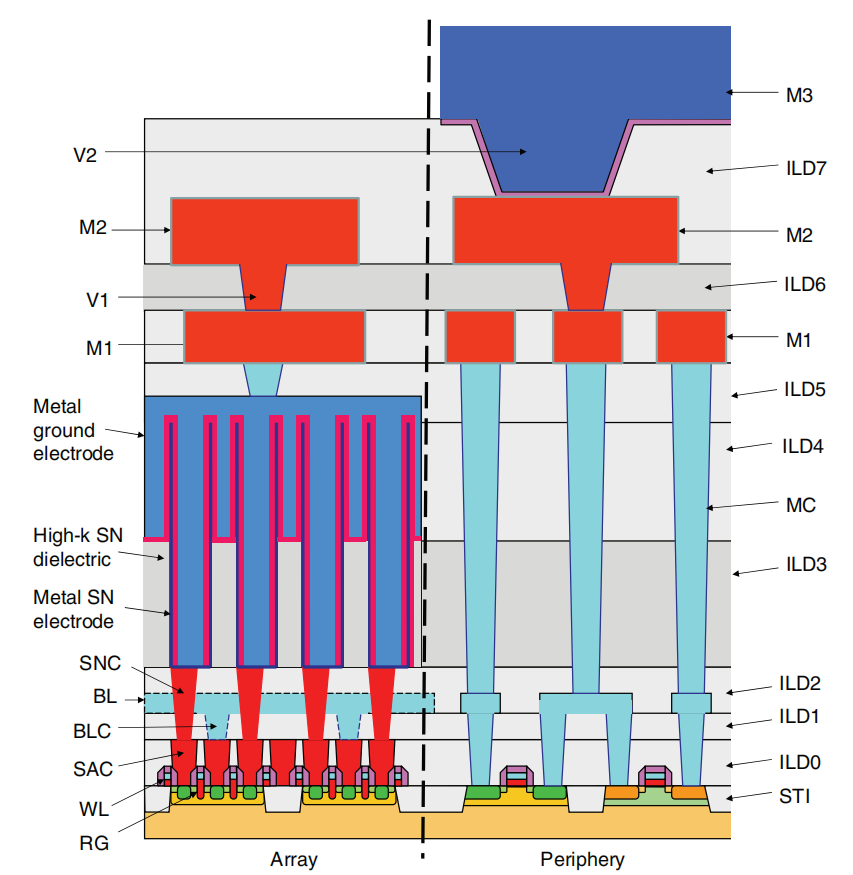

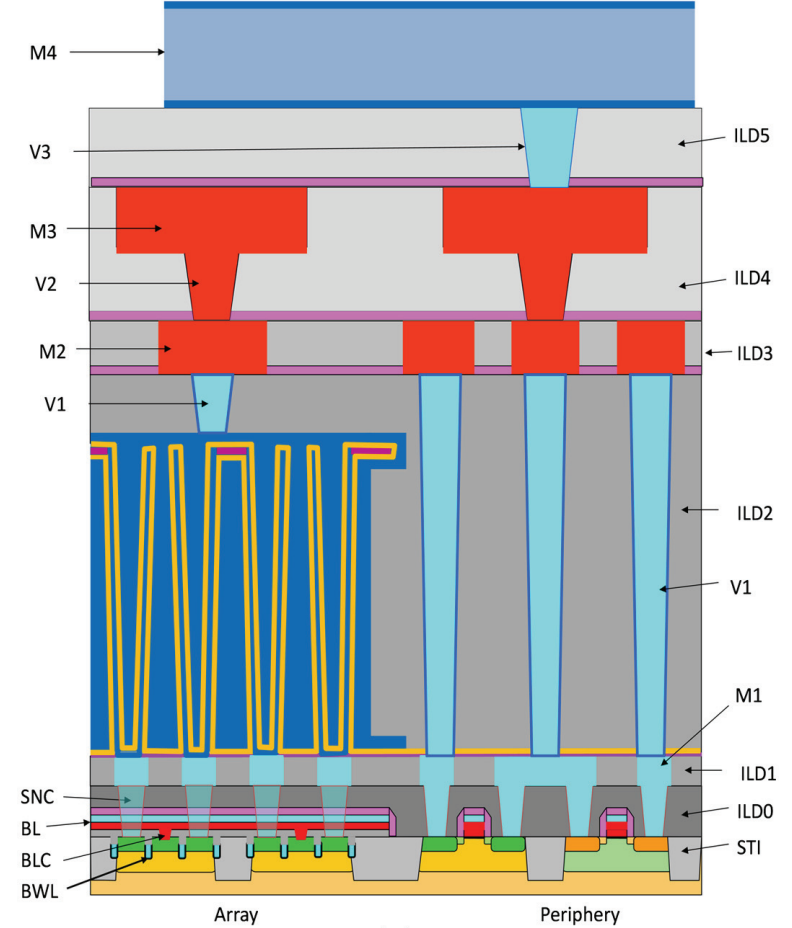

如下图为平面晶体管式的DRAM截面示意图:

BL:bit line

BLC: bit-line contact, ILD: inter-layer dielectrics

MC: metal contact

SAC: self-aligned contact

SN: storage node SNC: storage_node contact

STI: shallow-trench isolation

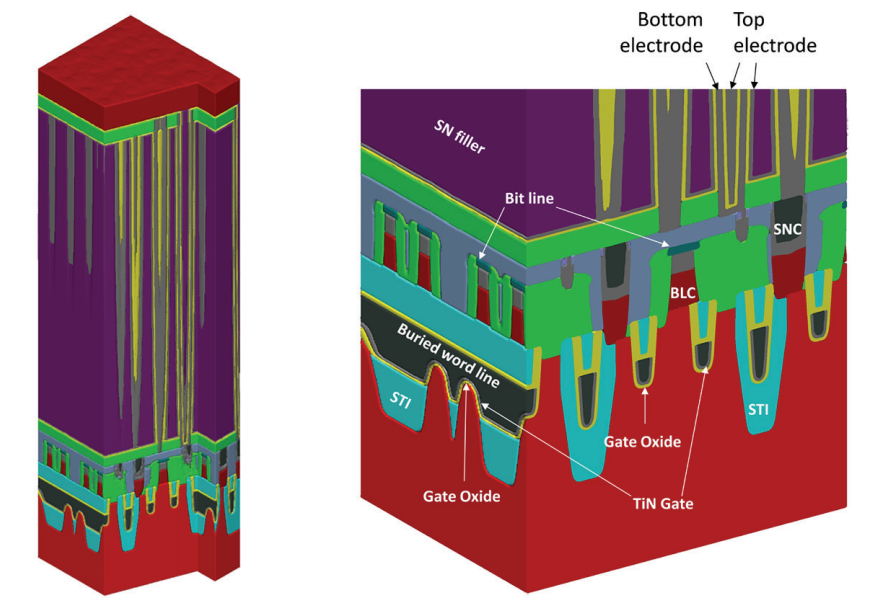

如下为3D结构示意图:

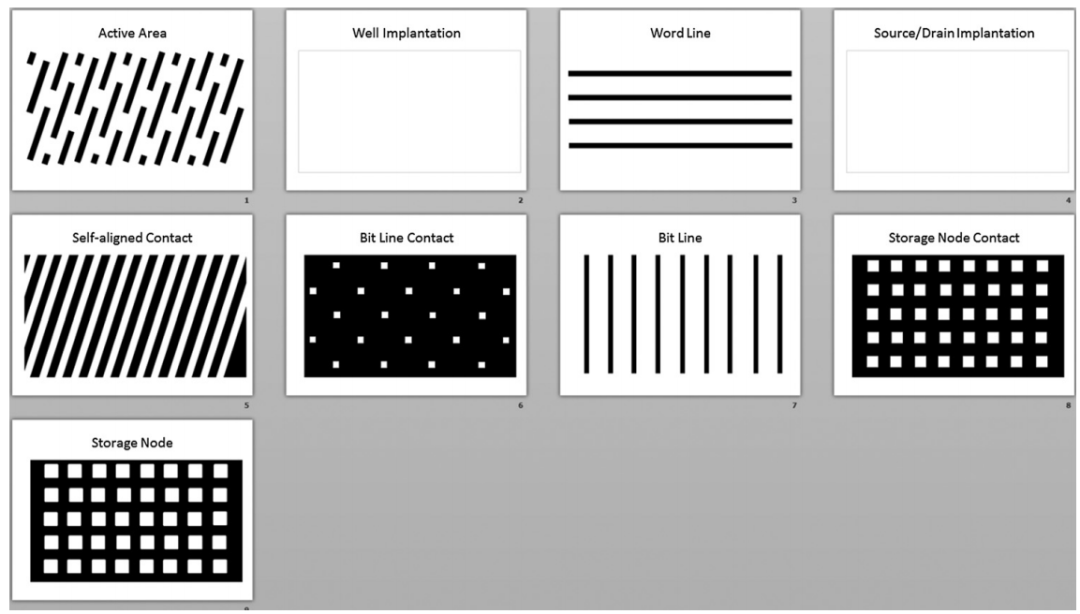

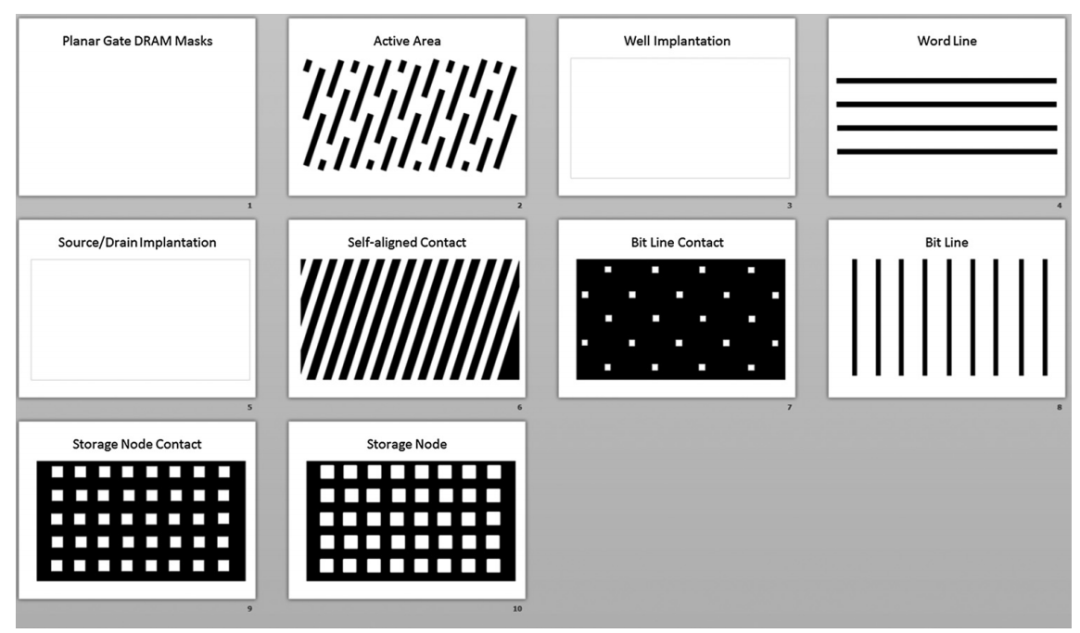

制造planar晶体管式的DRAM共需要9块光罩(array区)

RG DRAM

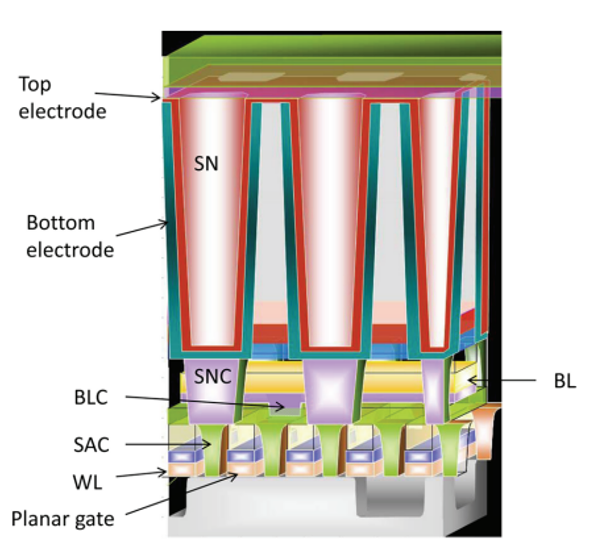

如下图为凹槽栅极(Recess Gate)晶体管式的DRAM截面示意图:

如下为3D结构示意图:

制造RG晶体管式的DRAM共需要10块光罩(array区)

BWL DRAM

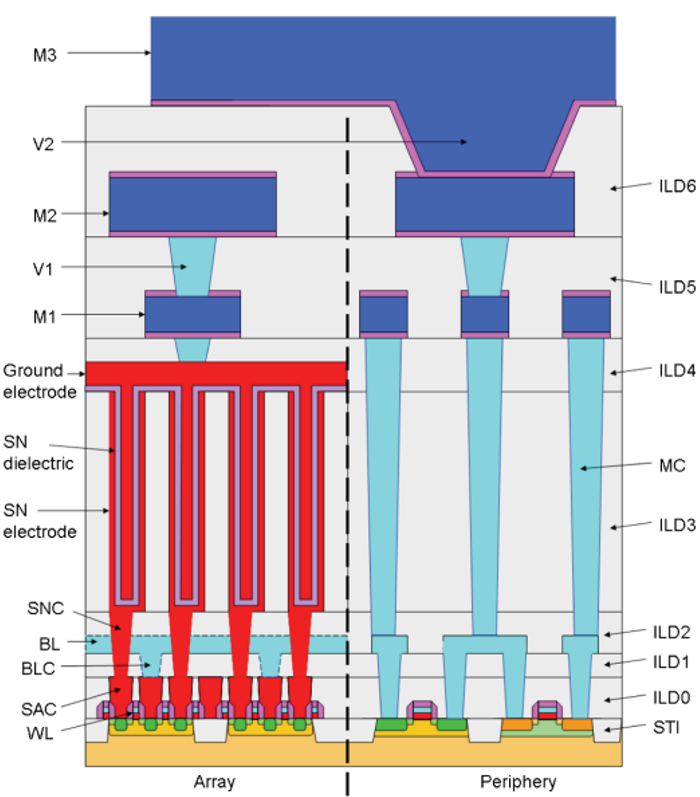

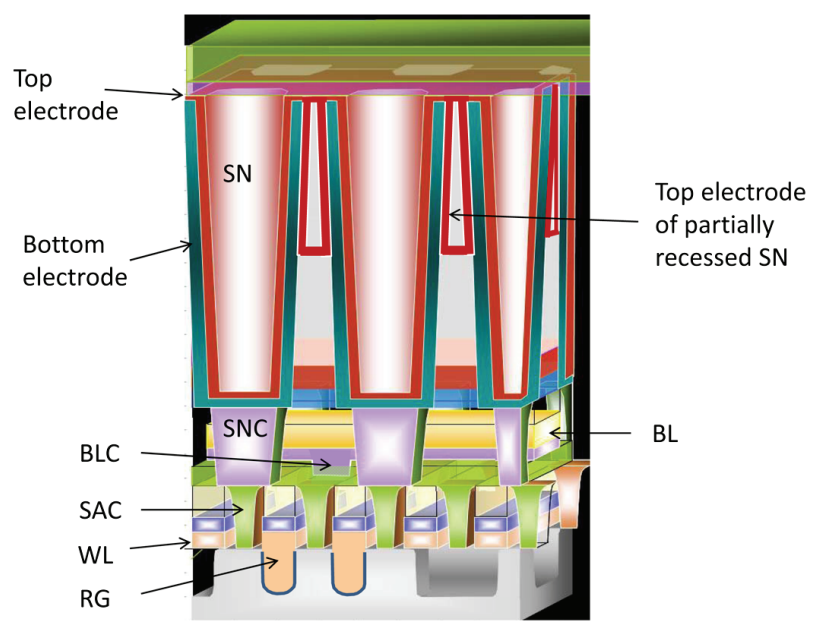

如下图为BWL(Buried Word-Line)晶体管式的DRAM截面示意图:

如下为3D结构示意图:

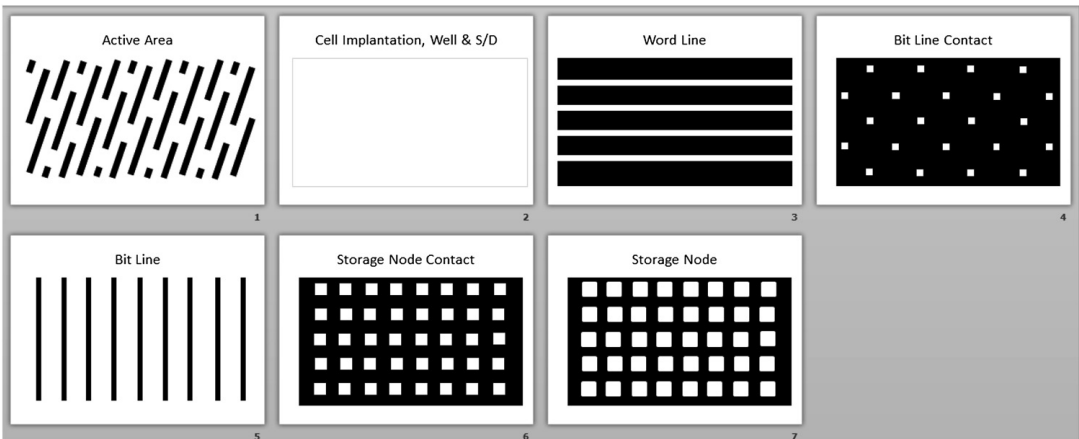

制造BWL晶体管式的DRAM只需要7块光罩(array区)

在以上三种结构中,BWL是目前主流应用,从光罩的使用上我们已经可以看出其具有明显的成本优势。所以在后续的章节中,我们将详细地以BWL DRAM为例,展开讲讲其工艺上的制造过程。

0

0