今天要讨论的几个问题如下:

1.IBIS输出端口的阻抗为什么大小不一样?

2.IBIS模型端口输出阻抗到底体现在哪里?为什么没有写在IBIS模型中?

3.为什么大多数情况下都是低速信号关心端口输出阻抗而高速信号不关心呢?

下面我们来一一看一下这几个问题。

问题一:为什么IBIS端口输出阻抗大小不一样

简而言之就是:这和设计以及工艺相关。具体涉及到的几个参数为:晶体管的沟道长度L,晶体管的宽度W,半导体工艺相关的参数:粒子迁移率 (电子为 ,空穴为 )和氧化层电容 .具体的内容我们看第二个问题。

问题二:IBIS模型端口输出阻抗到底体现在哪里?为什么没有写在IBIS模型中?

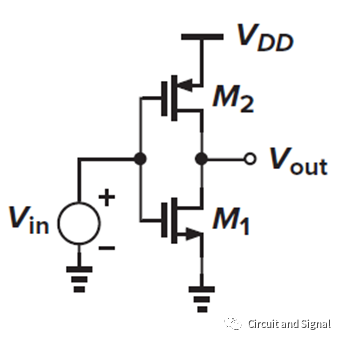

首先我们看看在SI领域使用的IBIS模型的通用电路结构。

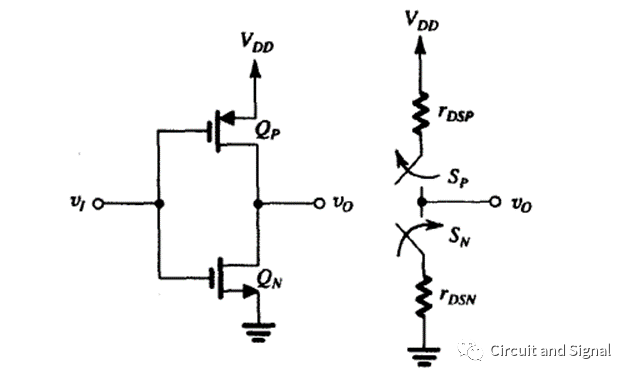

这是数字应用电路常见的IBIS模型简化的结构,M1是NMOS。M2是PMOS。当输入Vin为低时,输出Vout为高,也就是逻辑1;当输入Vin为高时,输出Vout为低,也就是逻辑0,可以看出输出和输入的状态刚好相反,这是电路设计相关的内容,大家可以参考任何IC设计书籍(我们后边讲)。为了更好地理解第一个问题,我们先拿出NMOS管,看看它的输出特性。

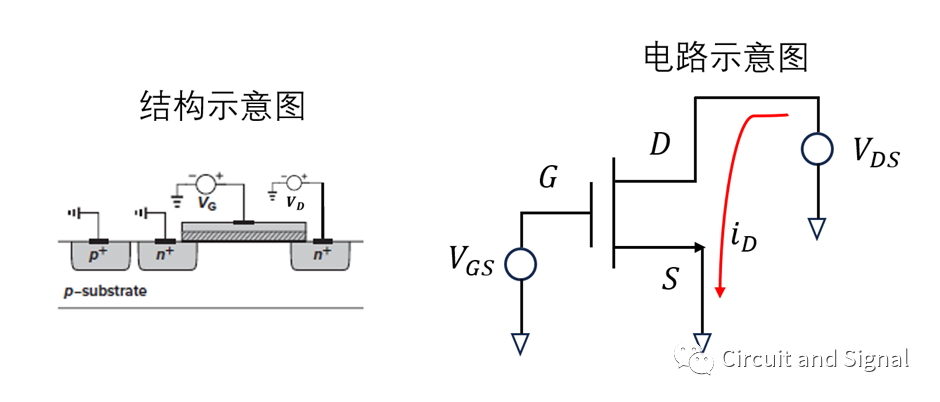

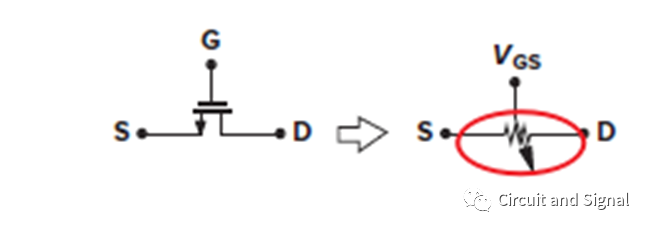

对于NMOS而言,其结构和电路示意图如下:

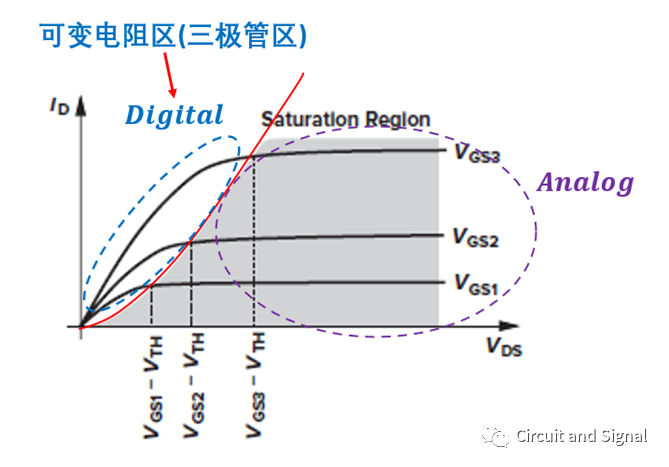

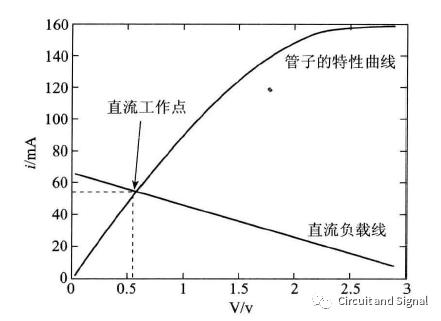

如果我们给Vgs和Vds不断地加电压,得到id和Vds的特性曲线如下图所示:

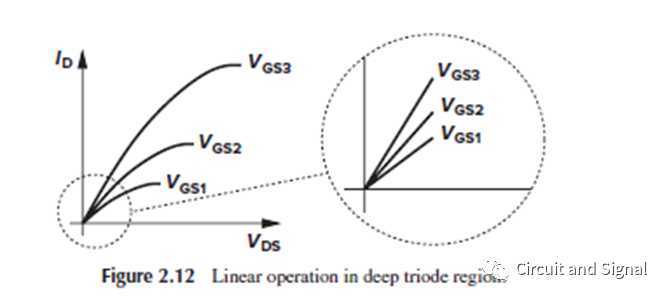

模拟电路主要应用在饱和区,而数字电路就应用在三极管区。在三极管区域(尤其是深三极管区,即Vds非常小的部分),我们就可以将MOS管看成一个电阻,如下图所示:

这个电阻的大小为:

根据工艺以及设计不同,分母这几个参数也不一样,该电阻的值大致范围在几十欧姆左右,比较小。这个值的计算需要知道比较多的参数,做系统设计的工程师不容易获取相关参数。但是,如果MOS管接了外部电路,我们就可以利用负载曲线法很容易计算这个直流阻抗,如下图所示:

此时得到的这个直流工作点的阻抗,我们就可以认为是NMOS的端口输出阻抗。当然,这里我们忽略了交流阻抗,交流阻抗主要影响噪声,我们后边电路设计部分再讲。因此,在这种状态下,第一张图就可以简化为如下的电路图:

以上内容可以参考IC集成电路设计书籍(拉扎维书籍第二章)。实际的端口输出阻抗其实已经包含在曲线中,我们需要手动计算,或是借助相关软件计算(参考前面的链接文章)。

问题三:为什么大多数情况下都是低速信号关心端口输出阻抗而高速信号不关心呢?

NO! 高速信号更关心端口输出阻抗,正因为如此,所以高速信号的端口输出阻抗在设计时就必须按照相关要求去设计。如单端常是50欧姆,差分常是100欧姆,它的设计优先级高!但是低速电路端口输出阻抗(一般)就不会特意去管控(任何良好的设计都是需要代价的,天下没有免费的午餐,电路设计也是如此),当然在要求很严格的产品设计中仍然会约束。因此,低速电路的IBIS模型输出端口阻抗很多时候就需要外部电路去做一些匹配,保证信号质量,我们常见的是在SOC输出端口会串一个小电阻,或者是负载端串一个小电阻,甚至在负载端并一个小电容等。以上这些措施都是为了保证信号完整性。

至于怎么理解在低速信号的IBIS模型中输出端口的驱动能力是以不同的电流大小来表示的,这个问题我们下次讲。实际上我们可以推测,电流就是电压除以电阻,电阻可变,电流也就可以变。具体内容我们下节讲。

输入端口阻抗类似,略过。

0

0