不是所有DDR3都可以用FLY_BY拓扑

前不久小A设计了一块单板,单板很简单,上面有一个主控芯片拖着2片DDR3颗粒,客户也没有任何要求,就说按照常规布线即可。小A也觉得这个设计很简单,凭着自己好几年的设计经验那还不是小菜一碟、信手拈来之事,所以也没有太多顾虑,三下五除二就完工了,DDR3布线,常规还不就是用拓扑,走线简单又省空间,哈哈,等着拿奖金吧。最近板子进入调试阶段,DDR3系统却死活运行不到额定频率,还老是死机,但是降频又能正常工作,各种办法用尽也无济于事,客户只好又来找小A,怀疑是不是有问题,小A此时也摸不着头脑,这么简单的板子怎么可能有问题呢,自己都是按照公司设计规范来做的啊,如果有问题那不是规范有问题?所以小A在束手无策的情况下也就只好找到我们制定规范的SI工程师了。

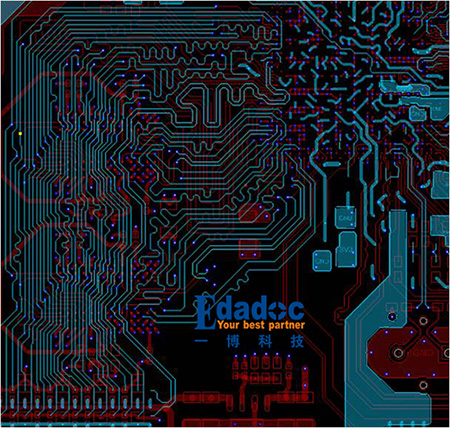

听了小A的描述,,但降频却工作正常,第一反应是时序问题,肯定是什么影响到了。小A也算是经验较丰富的设计人员了,对于等长、线间距及电源设计等注意事项应该是烂熟于心的,而且公司也会不定期的培训,查板后也排除了这些问题,板子见如下图一所示。

图一、Fly_by拓扑

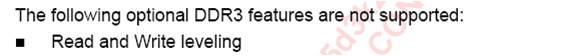

看来要查看芯片手册了,打开芯片功能规范手册,直接找到DDR控制器部分,下面这句话真是亮瞎了我的24K钛合金火眼金睛:

问题找到了,原来这个主控芯片不支持读写平衡功能,既然不支持读写平衡功能,那么这个设计就不能使用Fly_by的拓扑结构,这确实是典型的疏忽大意。

由于无法修改主控芯片内部的参数,也不想降频使用,看来只能使用T型拓扑改版了,可惜啊,小A的疏忽大意差点酿成了大错,还好客户只是前期的小批量测试版本。

各位看官,看到这里您会不会觉得其实设计也不是这么容易的事?稍不留神就有可能阴沟里翻船?所以我们要不断学习,丰富自己的经验,降低出错率。

原文链接:http://www.edadoc.com/cn/TechnicalArticle/Show.aspx?id=555

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

硬件电路是电子产品实现功能的物理载体,电子产品的功能都是依靠硬件电路实现的。

-

3W原则是PCB布线中的一项经验法则,要求相邻信号线的中心间距 至少为单根信号线宽度(W)的3倍 。

-

低电平复位基本概念:是指当复位信号为低电平时,电路进行复位操作。复位信号在有效(低电平)期间,系统或芯片的内部状态被强制恢复到初始状态。

-

之前写的恒流源电路都是单向的,即只能提供一个流向,支持sink或者支持source,但是不同时支持sink和s

-

-

大家好,我是山羊君Goat。时钟就类似于单片机最小系统中的心脏了,是一个单片机最小系统中一个必不可少的成分,可以产生特定频率的时钟信号,其作为时间参考值来保证数据的正常传输。

-

-

-

在工业自动化的精密舞台上,PLC(可编程逻辑控制器)控制柜扮演着指挥家的角色,确保每一台设备都能精准无误

-

在PCB设计中,蛇形走线是一个常见的布线方式,主要用于调节延时,以满足系统时序要求。

-

电源对于嵌入式系统中的作用可以看做是空气对人体的作用,甚至更重要......

-

0

0