3W原则是PCB布线中的一项经验法则,要求相邻信号线的中心间距 至少为单根信号线宽度(W)的3倍 。例如,若线宽为6mil,则间距需≥18mil。其核心目的是减少信号间的串扰(Crosstalk) ,确保信号完整性(SI)和电磁兼容性(EMC)。

为什么是3W?

1、减少电场耦合 :实验表明,当间距达到3W时,信号间约70%的电场耦合可被抑制,显著降低串扰风险。

为了减少线间串扰,应保证线间距足够大,如果线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W规则。

2、磁场耦合控制 :3W间距能有效减小互感,抑制高频信号的磁场干扰。

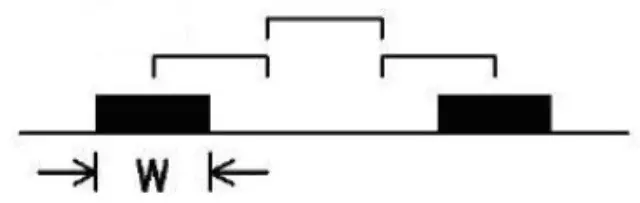

磁场耦合由信号回路间的互感引起,其强度与以下因素相关:

- 间距(d) :导线中心距越大,互感越小。

- 信号频率(f) :高频信号磁场耦合更显著。

- 回路面积(A) :信号与返回路径形成的环路面积越大,互感越强。

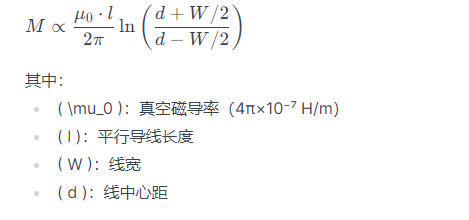

互感系数M的简化公式:

3、经验与理论结合 :该数值源于工程实践与电磁场理论,平衡了布线密度与信号质量的需求。两条走线中间的印制线3有一个过孔。这个过孔通常与第三条走线相连,这条走线中可能通过一个易产生电磁破坏的信号。例如,复位线、音频或视频走线、模拟电路控制走线或者I/O接口线等,它将以电感或电容的形式感受额外的电磁能量干扰。为最小化走线对过孔的串扰,相邻走线的距离间隔必须包括过孔直径和间隙间隔,距离时钟线的2W范围内没有其他信号。对富含RF能量的走线的距离间隔也有同样的要求,这种走线上的能量可能会耦合到元件的引脚上。是否一定要满足3W?

3、经验与理论结合 :该数值源于工程实践与电磁场理论,平衡了布线密度与信号质量的需求。两条走线中间的印制线3有一个过孔。这个过孔通常与第三条走线相连,这条走线中可能通过一个易产生电磁破坏的信号。例如,复位线、音频或视频走线、模拟电路控制走线或者I/O接口线等,它将以电感或电容的形式感受额外的电磁能量干扰。为最小化走线对过孔的串扰,相邻走线的距离间隔必须包括过孔直径和间隙间隔,距离时钟线的2W范围内没有其他信号。对富含RF能量的走线的距离间隔也有同样的要求,这种走线上的能量可能会耦合到元件的引脚上。是否一定要满足3W? 在实际PCB的设计过程中,3W在很多场景下是很难满足的。实操过程中我们首先要识别出需要走3W的信号,比如一些高速信号,而一些GPIO、I2C、UART等等信号其实不需要满足这么宽的间隔。

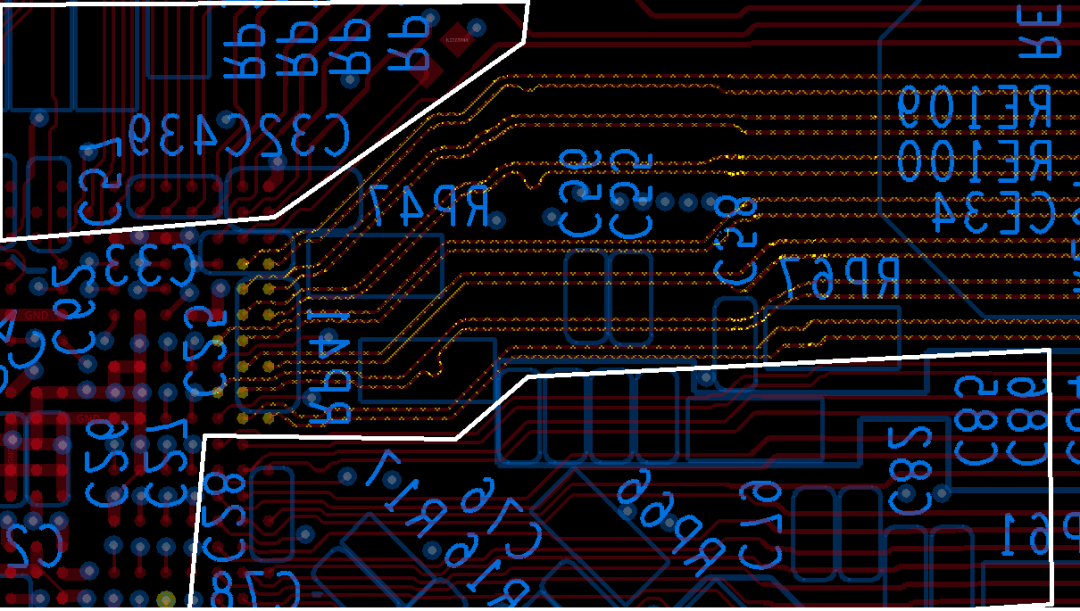

在实际PCB的设计过程中,3W在很多场景下是很难满足的。实操过程中我们首先要识别出需要走3W的信号,比如一些高速信号,而一些GPIO、I2C、UART等等信号其实不需要满足这么宽的间隔。 如图中,我们把足够的空间给MIPI信号(黄色),而其他低速接口或者GPIO电平信号(白框内),我们都直接按照工艺要求,走最小间距即可。

如图中,我们把足够的空间给MIPI信号(黄色),而其他低速接口或者GPIO电平信号(白框内),我们都直接按照工艺要求,走最小间距即可。

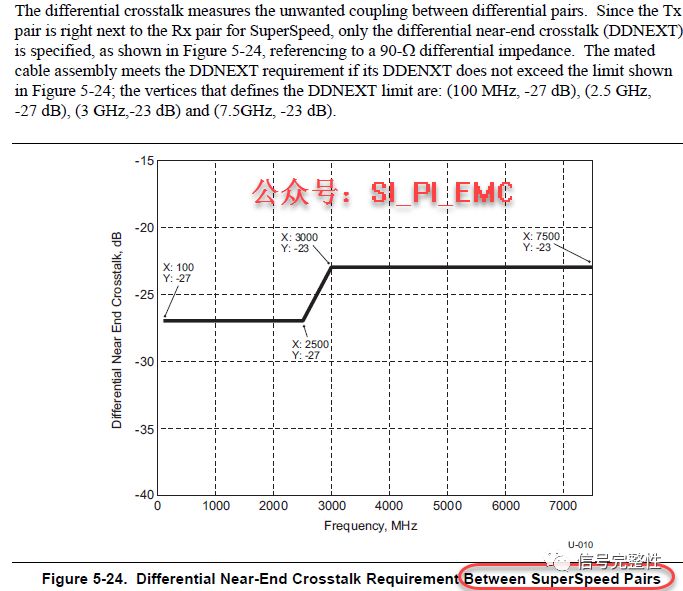

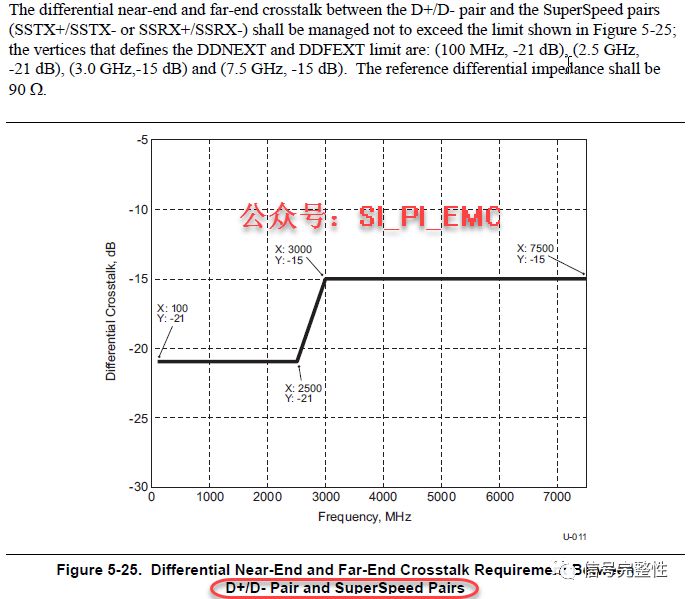

只要不影响到产品正常工作的串扰都是可以接受的。当然,其实这就与产品的实际应用或者要求有关系。因为每一种产品或者应用不同,其要求就不相同。比如,USB3.0规范中就定义了线缆的串扰,这个串扰还分为了superspeedpairs的串扰以及superspeed与D+/D-之间的串扰,如下图所示:

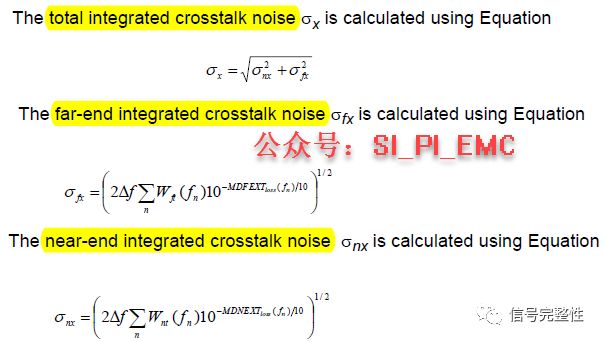

由于USB的设计比较简单以及信号比较少,所以串扰的要求也比较简单清楚,但是对于一些更高速的总线或者要求更高的总线,串扰的要求就会比较复杂,计算的是ICN(Integratedcrosstalk noise),比如下列是OIF CEI对串扰的要求:

The Integrated Crosstalk Noise (ICN) is less than 3.9 mV.MDNEXT shall be less than 1.35 mV RMS. MDFEXT shall be less than 3.6 mV RMS.具体的计算如下所示:

以上只是部分计算公式,只是用于举例,详细的请参考CEI的规范。但是很多工程师看到这个公式估计就晕菜了,更别说计算啦。但是我要说的是,更给出具体规范的就要感谢协会那些定义这些参数的工程师啦,否则,我们只能按经验来做。

那么经验是什么呢?对于串扰而言,没有特殊要求的情况下,就按照信号幅值或者电源电压大小的5%或者-26dB计算,如果信号幅值或者电源电压比较小,则把要求再定紧一些,比如1%或者-40dB。这些都是从数值理论上来计算的,仅供参考。具体到实际项目的时候,还要看实际的情况,毕竟串扰不仅仅与信号传输的结构有关系,还与信号本身也有关系(激励源的上升时间、激励源与受干扰源的相位等等)。

串扰不满足时的应对策略

-

地线隔离

- 在关键信号线间插入地线(Guard Trace),利用地电位吸收干扰。

- 示例:高速时钟线旁布设接地过孔或连续地平面。

层叠结构优化

- 相邻信号层采用正交布线(如一层水平,另一层垂直),减少层间耦合。

- 增加地层作为屏蔽,如使用“信号-地-信号”的层叠顺序。

差分信号技术

- 对高速信号(如USB、HDMI)采用差分对设计,依赖自身的抗干扰特性降低对间距的要求。

端接匹配

- 添加串联端接电阻或并联终端电阻,减少信号反射,从而降低串扰敏感度。

局部牺牲布线密度

- 优先确保高频/敏感信号满足3W,对低频或非关键信号适当放宽间距。

仿真验证

- 使用SI/PI工具(如HyperLynx、Sigrity)评估串扰水平,通过仿真结果指导例外处理。

避免串扰不能单靠3W拉开距离,因为空间有限。也应从PCB设计和布局方面来考虑,例如:(1)根据功能分类逻辑器件系列,保持总线结构被严格控制。(2)最小化元器件之间的物理距离。(3)高速信号线及元器件(如晶振)要远离I/()互连接口及其他易受数据干扰及耦合影响的区域。(4)对高速线提供正确的终端。(5)避免长距离互相平行的走线布线,提供走线间足够的间隔以最小化电感耦合。(6)相临层(微带或带状线)上的布线要互相垂直,以防止层间的电容耦合。(7)降低信号到地平面的距离间隔。(8)分割和隔离高噪声发射源(时钟、I/O、高速互连),不同的信号分布在不同的层中。(9)尽可能地增大信号线间的距离,这可以有效地减少容性串扰。(10)降低引线电感,避免电路使用具有非常高阻抗的负载和非常低阻抗的负载,尽量使模拟电路负载阻抗稳定在loQ~lokQ之间。因为高阻抗的负载将增加容性串扰,在使用非常高阻抗负载的时候,由于工作电压较高,导致容性串扰增大,而在使用非常低阻抗负载的时候,由于工作电流很大,感性串扰将增加。

(11)将高速周期信号布置在PCB酌内层。

(12)使用阻抗匹配技术,以保BT证信号完整性,防止过冲。

(13)注意对具有快速上升沿(tr≤3ns)的信号,进行包地等防串扰处理,将一些受EFTlB或ESD干扰且未经滤波处理的信号线布置在PCB的边缘。

(14)尽量采用地平面,使用地平面的信号线相对于不使用地平面的信号线来说将获得15~20dB的衰减。(15)信号高频信号和敏感信号进行包地处理,双面板中使用包地技术将获得10~15dB的衰减。(16)使用平衡线,屏蔽线或同轴线。(17)对骚扰信号线和敏感线进行滤波处理。

(18)合理设置层和布线,合理设置布线层和布线间距,减小并行信号长度,缩短信号层与平面层的间距,增大信号线间距,减小并行信号线长度(在关键长度范围内),这些措施都可以有效减小串扰。

0

0