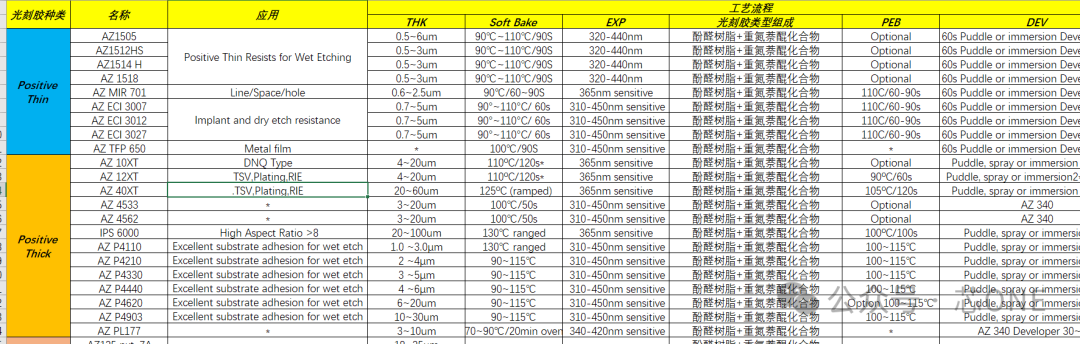

关于常用光刻胶型号也可以查看这篇文章:收藏!常用光刻胶型号资料大全,几乎包含所有芯片用光刻胶

来源:芯one

声明:本文由半导体材料与工艺转载,仅为了传达一种观点,并不代表对该观点的赞同或支持,若有侵权请联系小编,我们将及时处理,谢谢。

0

0