各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物2)热载流子注入(HCI)3)负偏压温度不稳定性(NBTI)4)表面反转(移动离子)5)浮栅非易失性存储器数据保持6)局部电荷捕获非易失性存储器数据保持7)相变(PCM)非易失性存储器数据保持后段制程(BEoL)常见的失效机理1)与时间相关的电介质击穿(TDDB)-- low k材质电介质/移动铜离子2)铝电迁移(Al EM)3)铜电迁移(Cu EM)4)铝和铜腐蚀5)铝应力迁移(Al SM)6)铜应力迁移(Cu SM)

封装/界面常见的失效机理1)因温度循环和热冲击导致的疲劳失效2)因温度循环和热冲击导致的界面失效3)因高温导致的金属间化合物和氧化失效4)锡须5)离子迁移动力学(PCB)--组件清洁度

本文对铝应力迁移模型进行研究

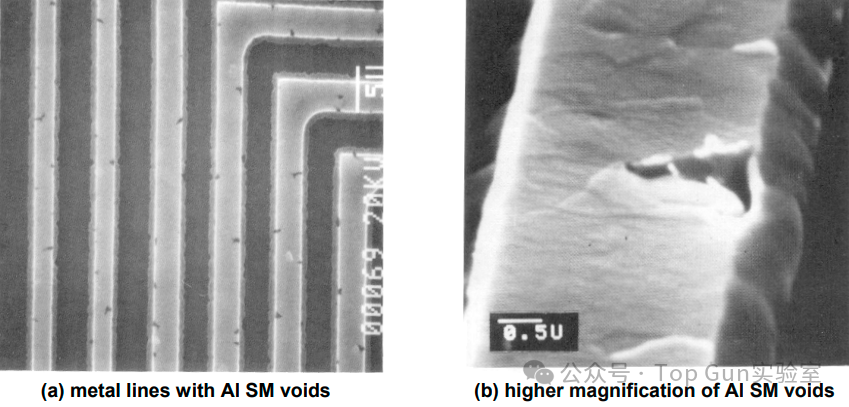

“应力迁移”这个术语描述的是金属原子在机械应力梯度影响下的移动。通常,应力梯度可以假定与所施加的机械应力成正比。与金属移动相关的通量发散会导致超大规模集成电路(ULSI)金属引线中出现空洞,空洞会导致电阻上升从而引起电气故障。 在铝合金互连中空洞的形核和生长过程中,应力和应力松弛的作用非常重要。铝中的铜掺杂在抑制晶界扩散方面有一定效果,但如晶粒尺寸与线宽相比过大效果就会差很多,研究发现由于晶内扩散会形成狭缝状空洞。 本文讨论的模型仅适用于铝合金(掺杂有铜和/或硅)。目前,应力迁移没有标准的行业测试规范。常用的测试方法:a)测试样品:长(>1000um)且窄(<2um)的铝金属条带;b)测试条件:在150~250°C的温度下(无偏置)存储1000~2000小时;注:应力迁移烘烤温度应谨慎选择,最大蠕变速率通常在150°~250°C 。c)判据:电学测试检测电阻增加量或击穿电流减小量。通常,晶界扩散的激活能约为0.5~0.7eV,单晶晶粒(竹节状)扩散的激活能为1.2~1.4eV(掺杂有铜时,激活能可能低至1eV)。使用难熔金属阻挡层或分层金属化往往可以消除竹节状引线中狭缝状空洞形成所造成的影响,难熔金属层充当冗余导体,分流电流,减少由于空洞形成而导致的电阻上升。

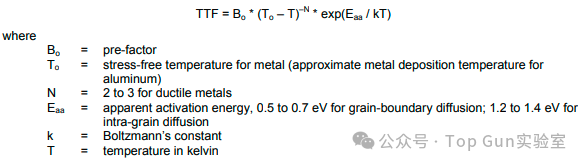

在铝合金互连中空洞的形核和生长过程中,应力和应力松弛的作用非常重要。铝中的铜掺杂在抑制晶界扩散方面有一定效果,但如晶粒尺寸与线宽相比过大效果就会差很多,研究发现由于晶内扩散会形成狭缝状空洞。 本文讨论的模型仅适用于铝合金(掺杂有铜和/或硅)。目前,应力迁移没有标准的行业测试规范。常用的测试方法:a)测试样品:长(>1000um)且窄(<2um)的铝金属条带;b)测试条件:在150~250°C的温度下(无偏置)存储1000~2000小时;注:应力迁移烘烤温度应谨慎选择,最大蠕变速率通常在150°~250°C 。c)判据:电学测试检测电阻增加量或击穿电流减小量。通常,晶界扩散的激活能约为0.5~0.7eV,单晶晶粒(竹节状)扩散的激活能为1.2~1.4eV(掺杂有铜时,激活能可能低至1eV)。使用难熔金属阻挡层或分层金属化往往可以消除竹节状引线中狭缝状空洞形成所造成的影响,难熔金属层充当冗余导体,分流电流,减少由于空洞形成而导致的电阻上升。1)机械应力模型 失效时间(TTF)可以使用埃林模型,在该模型中,计算机械应力的幂律与阿伦尼乌斯因子的乘积。

2)热机械应力模型: 如果应力是由不同的热膨胀率产生的,那么这种应力被称为“热机械应力”,并且与温度的变化(即热应变,ε ∝ (ΔT))成正比,热应变进而驱动应力σ。

2)热机械应力模型: 如果应力是由不同的热膨胀率产生的,那么这种应力被称为“热机械应力”,并且与温度的变化(即热应变,ε ∝ (ΔT))成正比,热应变进而驱动应力σ。

应力迁移寿命预估示例:目标:

计算办公环境与加速应力环境下应力迁移的加速因子(AF)。

假设条件:1)正常使用条件为:50°C芯片温度

2)加速条件为:150℃应力温度3)To:300℃4)N:2.55)表观活化能Eaa:0.55eVAF计算公式:

AF=[(To–Toffice)/(To–Taccel)]–N*exp[(Eaa/k)(1/Toffice–1/Taccel)]

假设条件代入计算:

AF=[(300–50)/(300–150)]–2.5*exp[(0.55eV/8.62x10–5eV/K)(1/(273+50)K–1/ (273+150)K)]=0.28*107=30结论:从加速环境转换为正常使用环境,TTF值将增加到加速应力值的约30倍。机械应力使TTF值增加约0.28倍(负方向),而温度使TTF值增加约107倍。

0

0