在 QII 中调用 CycloneV 的 SERDES 和 reconfig 模块时,IPCore 会自动生成以子目录形式存在相关仿真文件(ArriaV 和 StratixV 也是一样的)。按照 Altera 提供的相关文档,可以通过执行自动生成的脚本文件,或者自己编写脚本文件,实现对 SERDES 的仿真。对于第一种方法,需要使用 quartus_sh 的命令执行脚本文件,尝试了一下并没有成功。其实在 Modelsim 下自行创建 do 文件的方式,可以更容易理解需要哪些仿真文件,并且这种方式会更加通用,适用于所有的仿真流程。

仿真所用到软件环境包括 Modelsim SE 10.0e 和 QII 12.0 SP1。

|

01 |

调用 CycloneV Custom PHY 和 Transceiver Reconfiguration Controller

|

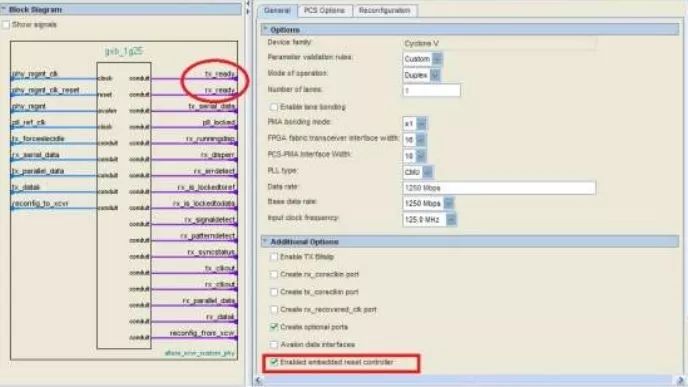

在例化 PHY IPCore 时,使能“Enable embedded reset controller”,PHY 自带 reset 模块,

“tx_ready”和“rx_ready”状态输出指示。

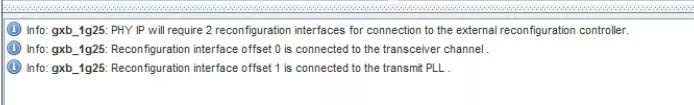

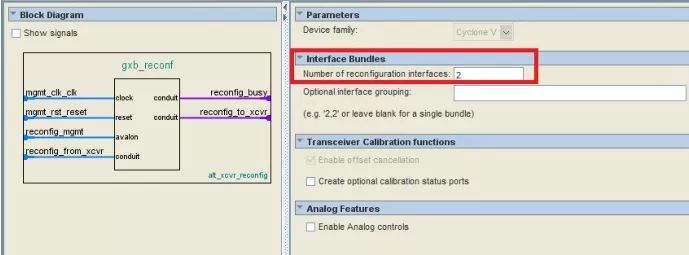

在例化 PHY IPCore 时,可以发现下面信息栏有提示需要与 2 个 reconfiguration 模块相连,一个是连接到 tran sceiver channel,一个是连接到 transmit PLL。所以在例化reconfiguration 模块时,在“Number of reconfiguration interfaces”栏内填写的参数为 2,这样才可以保证 PHY 与 reconfiguration 模块的“reconfig_to_xcvr”和“reconfig_from_xcvr”两个信号的数据位宽相匹配。(PHY IPCore 仅例化了一个 SERDES 通道)

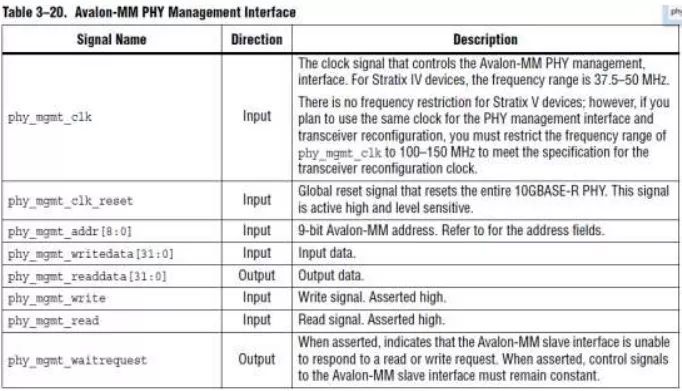

Custom PHY 的相关参数设置,是需要通过 Avalon-MM PHY Management Interface 进行访问的,参数的设置都是以寄存器方式进行读写。参照“Altera Transceiver PHY IP CoreUser Guide”,设置 SERD ES 自回环,使能 RX 字节对齐模块。对应地址偏移为 0x061,“phy_mgmt_writedata”设为 32’d1;地址偏移为 0x085,“phy_mgmt_writedata”设为 32’d1。

|

02 |

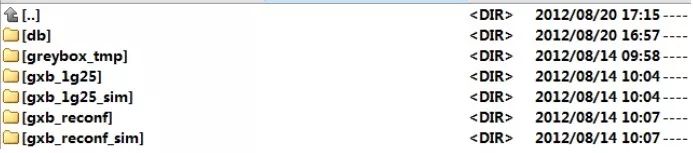

生成 Custom PHY 和 Reconfiguration IPCore 之后,在工程目录下会分别生成两个不同的目录,包括 IPCore 的设计和仿真文件。

|

|

03 |

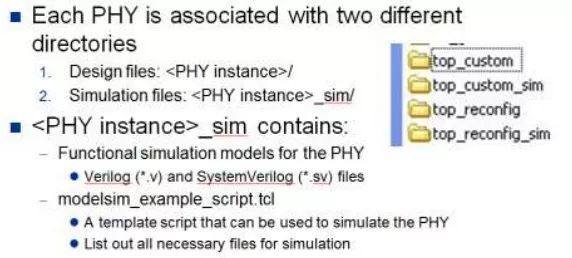

在工程当前目录下新建 Modelsim 文件夹,相关 tesetbench 和仿真产生的文件都会存于此目录下。

|

|

04 |

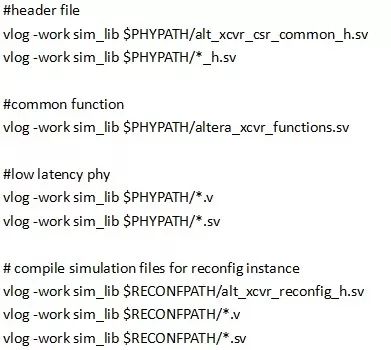

创建 simlib.do 文件,对除了工程相关文件之外的所需仿真文件,进行编译。文件内容如下:

|

set LIBPATH c:/altera/12.0/quartus/eda/sim_lib/

#指定 sim_lib 目录

set PHYPATH ../gxb_1g25_sim/altera_xcvr_custom_phy

#指定 Custom PHY 目录

set RECONFPATH ../gxb_reconf_sim/alt_xcvr_reconfig

#指定 Reconfiguration 目录

vlib sim_lib

vmap sim_lib sim_lib

#创建 sim_lib 仿真库,将相关仿真库文件编译至此库中

vlog -work sim_lib $LIBPATH/220model.v

vlog -work sim_lib $LIBPATH/altera_mf.v

vlog -work sim_lib $LIBPATH/sgate.v

vlog -work sim_lib $LIBPATH/altera_primitives.v

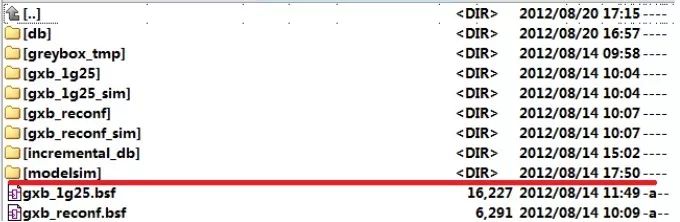

#添加常规需要的仿真库文件之外,其中下面 5 个文件,作为 CycloneV 系列在Modelsim 下推荐编译的仿真库文件

#以下仿真库文件为当前工程调用 PHY 和 Reconfiguration IPCore 的相关文件

|

05 |

创建 sim.do 文件,将工程相关文件进行编译。文件内容如下:

|

#do simlib.do

vlib work

vmap work work

#创建 work 仿真库,将工程相关仿真库文件编译至此库中

vlog +acc -work work -incr -f run.f

#将工程相关带路径的文件名存放在 run.f 的文件中,对其进行编译。Run.f 为任意命名的文件

vsim -novopt -L sim_lib -l run_modelsim.log \

+transport_int_delays +transport_path_delays \

work.tb_top

#对 work仿真库的 tb_top 模块进行仿真,其中 tb_top 为 testbench 中的 module名称,仿 真 记 录 信 息 存 放 于 run_modelsim.log 日 志 文 件 中 ,

“+transport_int_delays+transport_path_delays”参数建议添加,表示当前为高速信号仿真

|

06 |

创建 run.f 文件,将工程相关文件名称存放在此文件中,并带有相对路径。文件内容如下,除了 tb_top.v 的 testbench 文件在当前所建的 modelsim 目录下,其余文件都在上一级,即当前工程目录下。

|

../gxb_1g25.v

../gxb_reconf.v

../mayuan.v

../phy_mgmt_ctrl.v

../top.v

tb_top.v

|

07 |

创建 wave.do 文件,执行上一步创建的 sim.do 文件,并将需要观察的信号置于wave 窗口,并运行仿真。文件内容如下:

|

quit -sim

do sim.do

add wave sim:/tb_top/u1_top/*

add wave -divider phy_mgmt_ctrl

add wave sim:/tb_top/u1_top/phy_mgmt_ctrl_inst/*

radix -hex

run 50us

|

08 |

打开 Modelsim,通过 File->Change Directory 命令将工作目录指定到创建的modelsim 目录下。由于是第一次运行仿真,可以先执行一次“do simlib.do”命令,即编译除工程文件之外的仿真库文件。以后再次运行仿真时,即可跳过此步骤。直接执行“dowave.do”命令,因为 wave.do 文件中已经嵌套了 sim.do 文件。

|

|

09 |

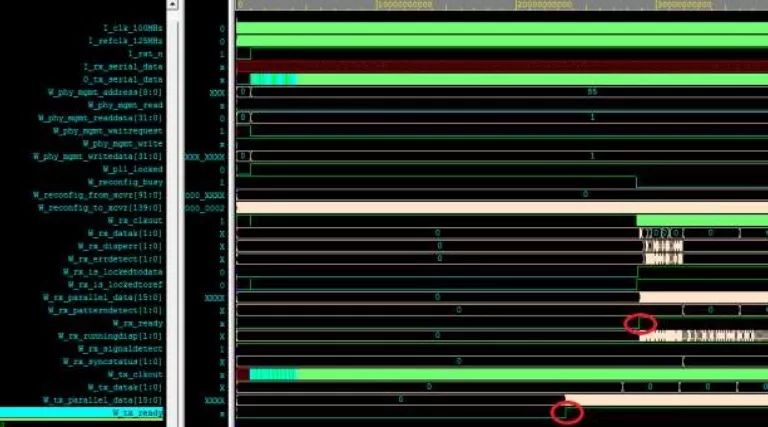

仿真结果

|

可以看到程序中在 tx_ready 信号变高之后,开始发送数据。在 rx_ready 信号变高之后一段时间,开始接收到正确的数据。

0

0