上文FPGA IP之AXI4协议2_信号需求把AXI协议5个通道的的信号进行详细说明(核心就是握手),本文对AXI 5个通道的依赖关系进行详述。

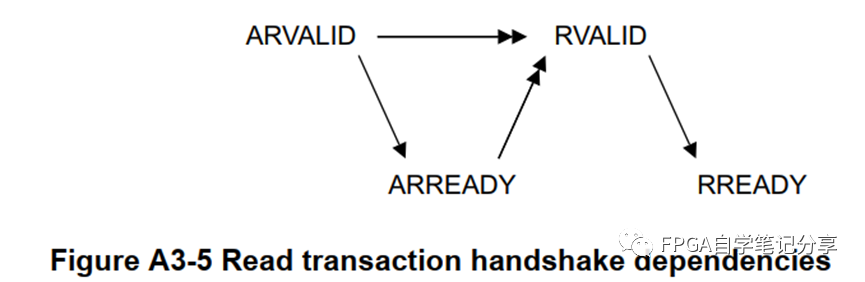

AXI协议要求存在以下基本关系:1 写响应必须始终跟随它所属的写操作中的最后一次写传输之后;2 读数据必须总是跟在数据地址后;3 通道握手必须符合通道握手信号的依赖关(依赖关系:FPGA IP之AXI4协议2_信号需求)。除此之外,协议不定义通道之间其它的任何关系。但是,不同通道上的握手信号之间存在依赖关系,并且AXI4定义了AXI3协议之外的写响应依赖关系。下面的关系图中双箭头表示必须的先后关系,单箭头表示无先后依赖关系。读传输依赖关系如下图,在读传输过程中:1、在ARVALID(读地址有效信号)拉高之前,主端不用等待从端的ARREADY(读地址准备就绪)拉高;2、从端可以等待ARVALID拉高后再拉高ARREADY;3、从端可以在ARVALID拉高前就拉高ARREADY;4、从端必须等待ARVALID和ARREADY都被拉高后,才能拉高RVALID(读数据有效信号),以表明有效数据可用;5、从端不用等待主端拉高RREADY后再拉高RVALID;6、主端可以在RREADY被拉高之前拉高RVALID;

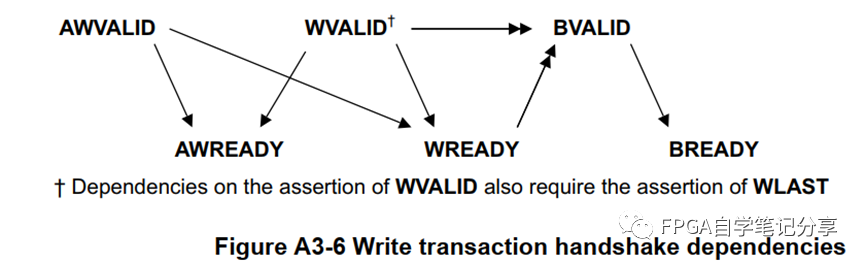

AXI3写传输依赖关系如下图,在写传输过程中:1、在AWREADY或WREADY拉高之前,主端不用等待从端拉高AWREADY或WVALID信号;2、在拉高AWREADY之前,slave可以等待AWVALID或WVALID拉高,或者等待两者都被拉高;3、从端可以在AWVALID或WVALID或两者都被拉高之前拉高AWREADY;4、从端可以在拉高WREADY之前,可以等待AWVALID或WVALID,或者等待两者都被拉高;5、从端可以在AWVALID或WVALID或两者都被拉高之前拉高WREADY;6、从端在拉高BVALID之前必须等待WVALID和WREADY都被高,从端在拉高BVALID之前也必须等待WLAST被拉高,因为写响应BRESP,必须在写事务的最后一次数据传输之后才发出信号;7、在BREADY拉高之前,主端不用等待从端拉高BVALID信号;8、在拉高BREADY之前,slave可以等待BVALID拉高;9、从端可以在BVALID被拉高之前拉高BREADY;

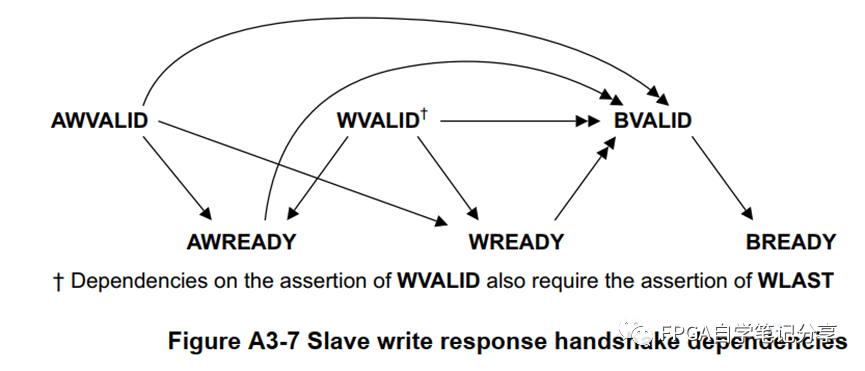

注意:AXI4协议增加了附加依赖项要求如下图,从端在拉高BVALID之前必须等待AWVALID, AWREADY, WVALID, WREADY都被高。

注意:AXI4协议增加了附加依赖项要求如下图,从端在拉高BVALID之前必须等待AWVALID, AWREADY, WVALID, WREADY都被高。 上图中的AXI4写响应依赖项中描述的附加依赖项意味着,写响应的AXI3协议从端与AXI4协议不兼容。将一个支持AXI3协议的老工程转换为axis4协议时需要添加一个控制器,以确保在从端接受了适当的地址之后才提供返回的写响应。AIX4协议适用于AXI3,不用增加控制逻辑。

上图中的AXI4写响应依赖项中描述的附加依赖项意味着,写响应的AXI3协议从端与AXI4协议不兼容。将一个支持AXI3协议的老工程转换为axis4协议时需要添加一个控制器,以确保在从端接受了适当的地址之后才提供返回的写响应。AIX4协议适用于AXI3,不用增加控制逻辑。

0

0