基础知识

1 模块(Module)

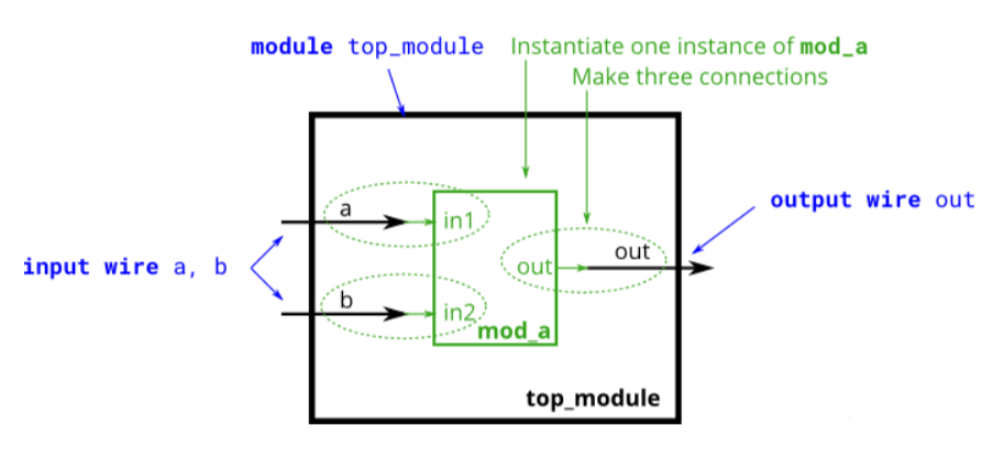

Verilog中的module可以看成一个具有输入输出端口的黑盒子,该黑盒子有输入和输出接口(信号),通过把输入在盒子中执行某些操作来实现某项功能。(类似于C语言中的函数)

图1 模块示意图

1.1 模块描述

图1 所示的顶层模块(top_module)结构用Verilog语言可描述为:

基础知识

1 模块(Module)

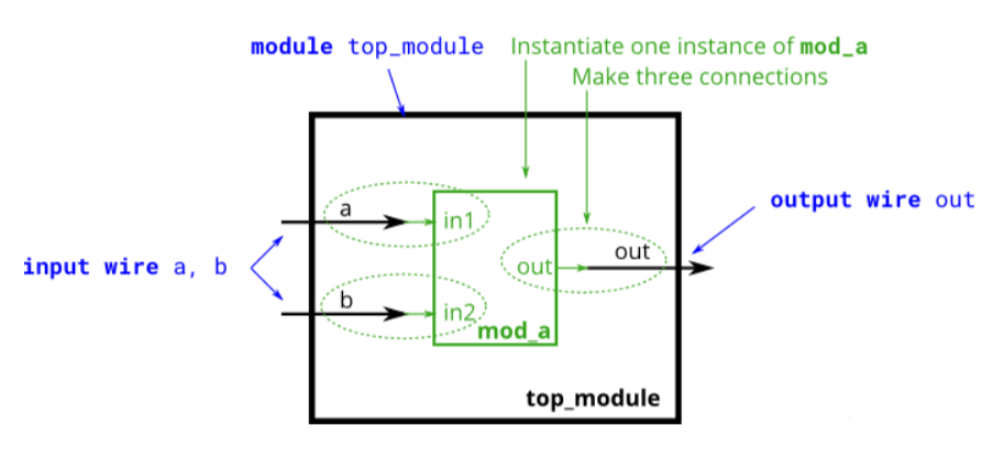

Verilog中的module可以看成一个具有输入输出端口的黑盒子,该黑盒子有输入和输出接口(信号),通过把输入在盒子中执行某些操作来实现某项功能。(类似于C语言中的函数)

图1 模块示意图

1.1 模块描述

图1 所示的顶层模块(top_module)结构用Verilog语言可描述为:

1、介绍\x26amp;nbsp; \x26amp;nbsp; \x26amp;nbsp;IBUFDS原语、OBUFDS原语以及IOBUFDS都是

一、Intel CvP 简介CvP(Configuration via Protocol)是一种通过协议实现配置的方案, Arria® V,Cyclone® V,Stratix® V,Arria® 10,Cyclone® 10 GX,Stratix® 10,Agilex™都支持这个功...

1、综合读写模块(无FIFO)\x26amp;nbsp; \x26amp;nbsp; \x26amp;nbsp;在前六篇SDRAM系列博文中,我们对S

本文将使用 ADI 最新的 AD9094-1000EBZ 和 Intel 的 FPGA Arria10 gx Development Kit,搭建基于 10G 的 JESD204B 测试环境。重点阐述如何搭建演示系统,相关的测试demo使用教程,以及相关...

对于非源同步的低速串行数据通信场景,会存在通信对端的时钟频率相对有偏差的情况,导致数据接收端不能正确的采样;这时候利用Altera中高端器件的高速收发器或者LVDS serdes中的SOFT-CDR及DPA功能便能解决此问题;但...