FPGA数字信号处理之verilog实现NCO(原理)

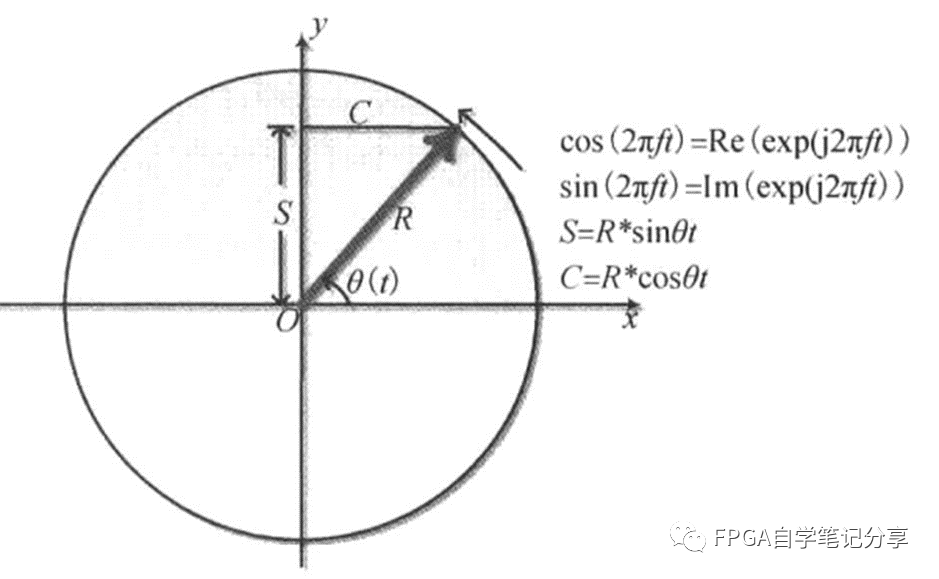

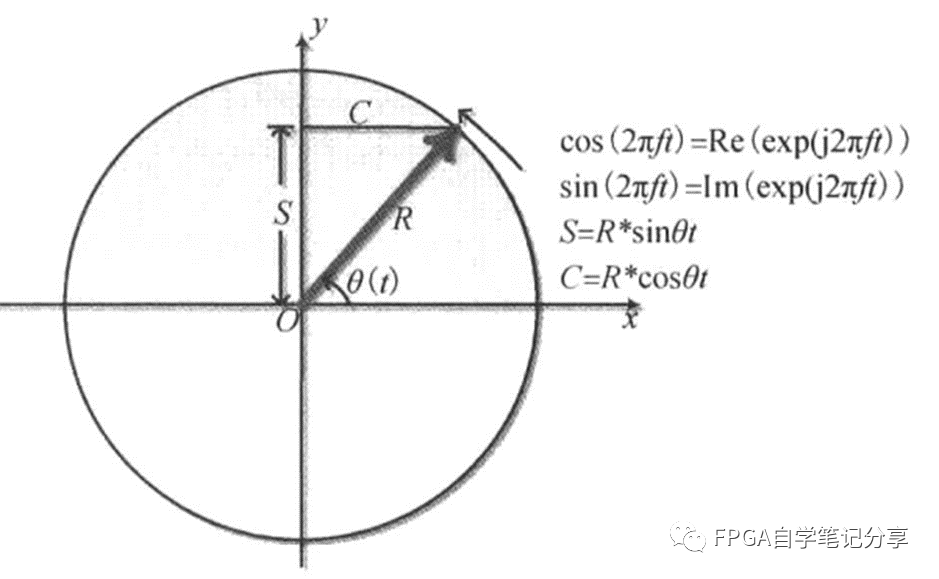

NCO:numerically controlled oscillator,数字控制振荡器,用来产生正弦波、余弦波,是数字信号处理中的基础元件之一。e^(ix)=(cos x+isin x) verilog生成NCO的常用方法有:1、推荐使用双端口ROM查找表的方式进行NCO设计;2、使用CORDIC算法进行NCO设计;3、查找表+计算的方式进行NCO设计;

verilog生成NCO的常用方法有:1、推荐使用双端口ROM查找表的方式进行NCO设计;2、使用CORDIC算法进行NCO设计;3、查找表+计算的方式进行NCO设计;

本文介绍查找表方式实现NCO的原理:

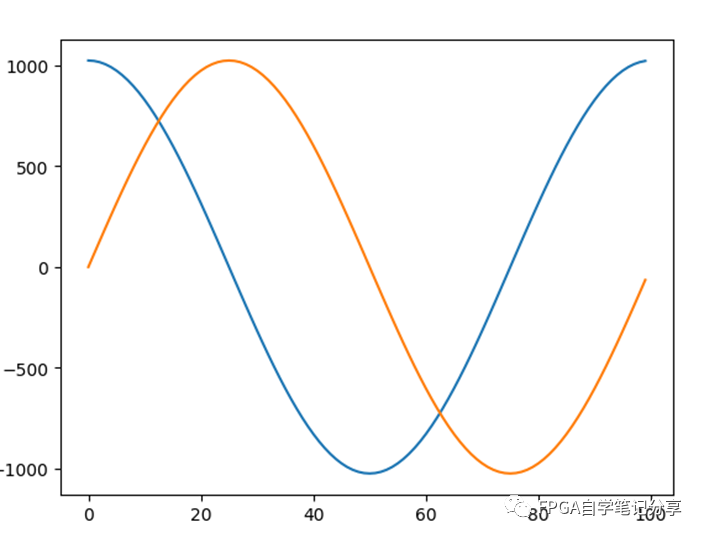

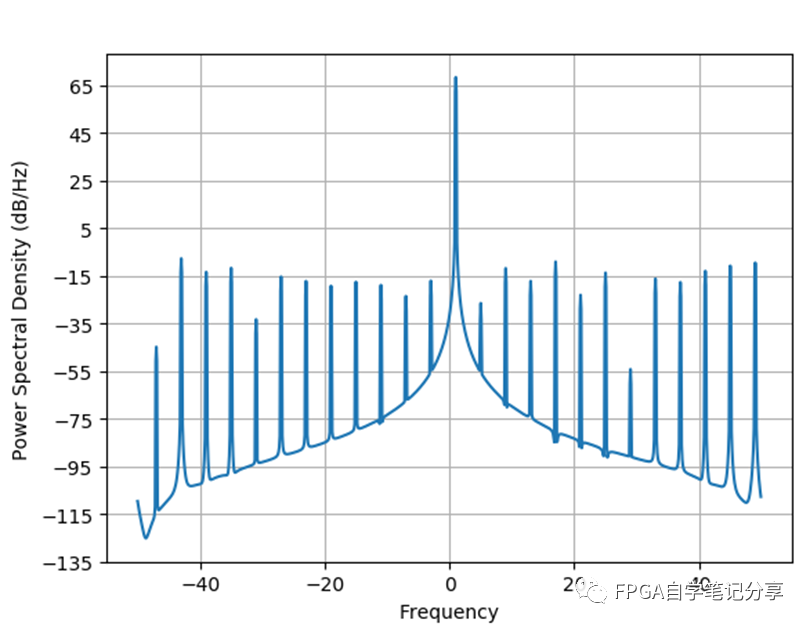

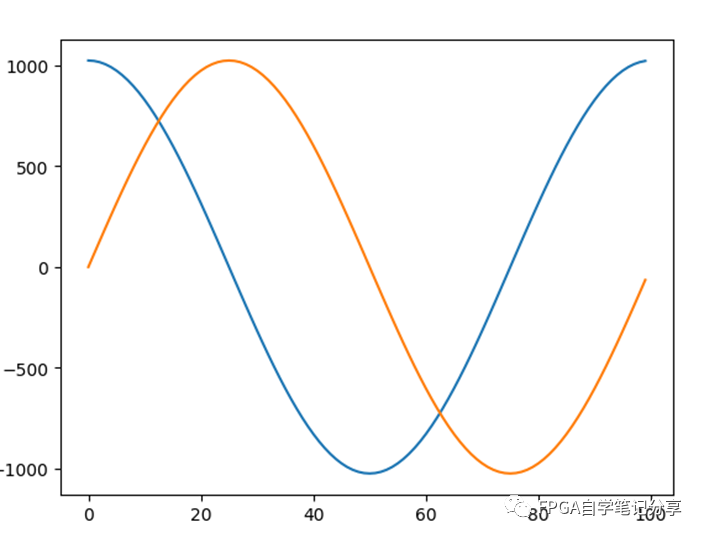

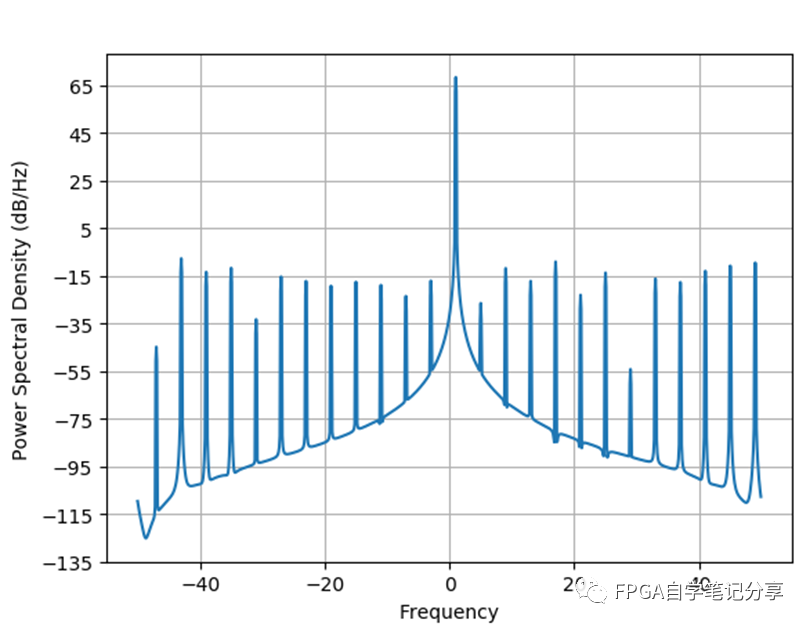

1、根据需求分析NCO需要的步进,进而确定NCO的点数:比如:100MHZ的采样率下,需要的频率是1MHz的整数倍,则NCO的最小步进即为1Mhz,此时一个NCO周期需要的点数为:100MHz/ 1Mhz = 100个点;2、分析需要的量化位宽,使用python或者matlab生成相应信号:Num = 100data_mult = 1024test_data = np.arange(Num)test_data = np.round(np.e**(test_data*1j*2*np.pi/Num)*data_mult)绘制生成信号的时域和频域如下图:

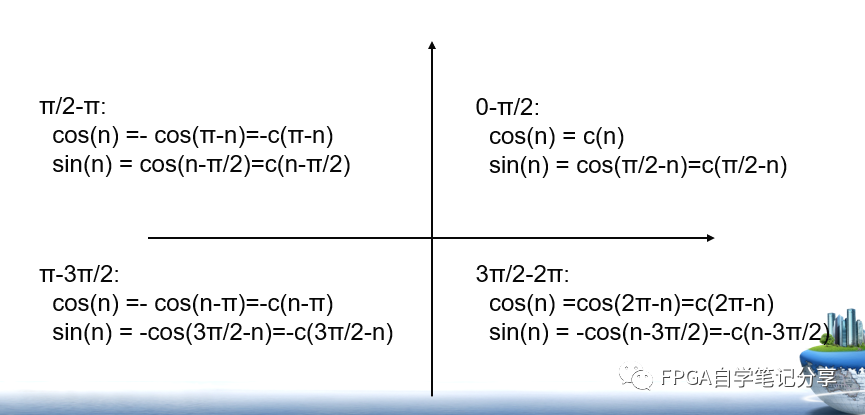

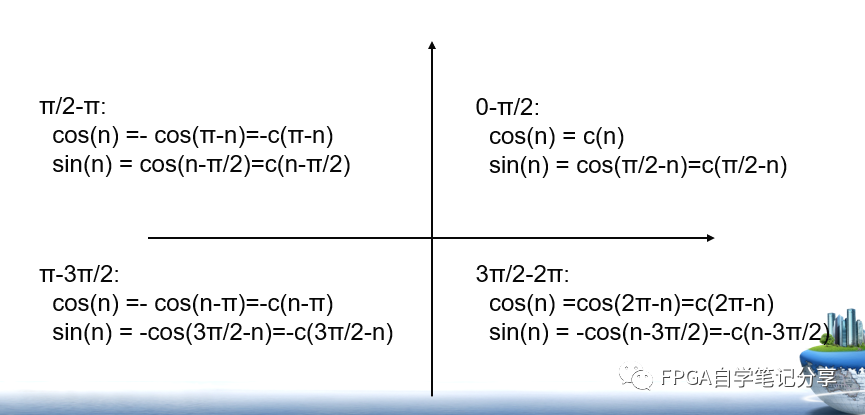

3、保存数据编写verilog代码,注意对最大信号的处理1024要-1。设计时可以根据单音信号的特性优化ROM深度:把0-π/2的 cos(n) = c(n),如下图所示:

3、保存数据编写verilog代码,注意对最大信号的处理1024要-1。设计时可以根据单音信号的特性优化ROM深度:把0-π/2的 cos(n) = c(n),如下图所示:

可以将rom查找表的深度简化到fs/4.

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

2025年的中国国际汽车电子高峰论坛将携手汽车产业的不同市场角色共同探讨汽车电子的未来发展,在技术与市场挑战中寻求更高的产业价值。

- 相关技术文库

- FPGA

- 可编程

- PLC

- verilog

-

什么是模块化设计FPGA/IC设计中根据模块层次的不同有两种基本的设计方法:自下而上方法对设计进行逐次划分的过

-

在电工领域摸爬滚打了20年的你,是否也曾对控制柜里的设计感到困惑不解?

-

-

-

-

1、介绍\x26amp;nbsp; \x26amp;nbsp; \x26amp;nbsp;IBUFDS原语、OBUFDS原语以及IOBUFDS都是

-

-

一、Intel CvP 简介CvP(Configuration via Protocol)是一种通过协议实现配置的方案, Arria® V,Cyclone® V,Stratix® V,Arria® 10,Cyclone® 10 GX,Stratix® 10,Agilex™都支持这个功...

-

1、综合读写模块(无FIFO)\x26amp;nbsp; \x26amp;nbsp; \x26amp;nbsp;在前六篇SDRAM系列博文中,我们对S

-

-

本文将使用 ADI 最新的 AD9094-1000EBZ 和 Intel 的 FPGA Arria10 gx Development Kit,搭建基于 10G 的 JESD204B 测试环境。重点阐述如何搭建演示系统,相关的测试demo使用教程,以及相关...

-

verilog生成NCO的常用方法有:1、推荐使用双端口ROM查找表的方式进行NCO设计;2、使用CORDIC算法进行NCO设计;3、查找表+计算的方式进行NCO设计;

verilog生成NCO的常用方法有:1、推荐使用双端口ROM查找表的方式进行NCO设计;2、使用CORDIC算法进行NCO设计;3、查找表+计算的方式进行NCO设计;

3、保存数据编写verilog代码,注意对最大信号的处理1024要-1。设计时可以根据单音信号的特性优化ROM深度:把0-π/2的 cos(n) = c(n),如下图所示:

3、保存数据编写verilog代码,注意对最大信号的处理1024要-1。设计时可以根据单音信号的特性优化ROM深度:把0-π/2的 cos(n) = c(n),如下图所示:

0

0