FPGA 验证是在芯片的研发环节中重要的组成部分,如何有效的利用 FPGA 的资源, 管脚分配也是必须考虑的一个重要问题。

通常,在综合过程中通过时序的一些约束让对应的工具自动分配是不错的选择,但是,从研发的时间段上来考虑这种方法往往是不可取的。

在研发过程中,RTL 验证与验证板设计必须同步进行,验证代码出来时验证单板也必须设计完成,也就是说管脚的分配必须在代码设计出来之前完成。所以,管脚的分配更依赖于人,而非工具,这个时候就更需要考虑各方面的因素。综合起来主要考虑以下的几个方面:

No.1、FPGA 所承载逻辑的信号流向

通常情况下,在IC 验证中所选用的 FPGA逻辑容量都非常大,外部的管脚数量丰富,因此必须考虑 PCB 设计时布线的难度,如果管脚的分配不合理,则有可能在PCB 设计时出现大量的交叉的信号线,这将给布线带来很多的困难,甚至走不通,即便布线走通了,也可能由于外部延时过大而无法满足时序要求。因此,在管脚分配前,设计者要对 FPGA 工作的环境相当熟悉,要对其中的信号来来源与去向都非常的清楚,然后按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中。

No.2、掌握 FPGA 内部 BANK 的分配的情况

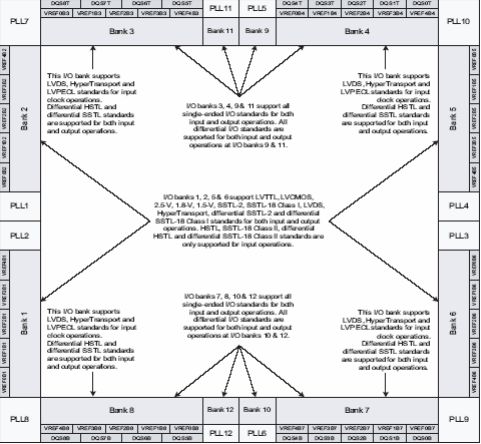

FPGA 内部BANK会分成几个区域,在每个区域中可用的 I/O 管脚数量各不相同。IC 验证多采用 ALTERA 和 XILINX 系列的 FPGA ,这两个厂商的 FPGA 中内部 BANK 的分配有一定的差异,在设计中需要查阅相关的手册。以 ALTERA Stratix II 系列的 FPGA 内部 BANK 的分配为例来说明,如图1。

图1 Stratix II 系列的 FPGA 内部 BANK 分配

图1中详细说明了 FPGA 内部 BANK 的分配情况以及每个 BANK 中所支持的 I/O 标准。设计者根据FPGA 内部 BANK 的分配情况,结合信号流向便可大概确定FPGA 在单板中的方向,同时按照就近的原则将相关的信号分配到相应的 BANK 中,这样即可完成一般信号的分配。

No.3、掌握FPGA每个 BANK 所支持的 I/O 标准

从图 1中可以看出 FPGA 内部的各个BANK 所支持的 I/O 的标准不尽相同,所以在管脚分配时要将支持相同标准的管脚集中到一个 BANK 中,通常情况下,FPGA 中同一个 BANK一般不同时支持两种 I/O 标准,当然也有例外,这就需要查阅相关 I/O 标准所要求的工作条件。

No.4、关注特殊信号的管脚的分配

这里讲的特殊信号主要是指:时钟信号、复位信号、以及一些要求驱动能力较高的信号。

时钟信号:一般时钟信号都是要求分配到全局的时钟管脚,这样获得的时间的延迟将是最小的,驱动能力也最强。

复位信号:因为复位信号要求同步性好,驱动能力强,所以一般的情况下也会从全局的时钟管脚送入。

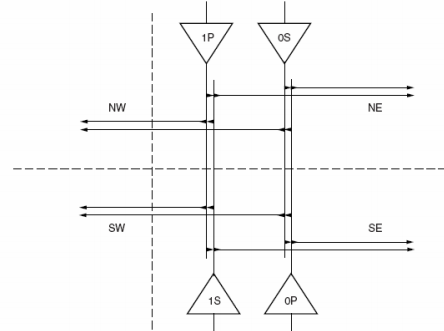

在分配时钟时,根据时钟的多少分配的策略差别很大,也需要重点关注,这需要查阅相应的手册,看每个时钟分别能到达的区域,一般时钟都是差分时钟,如果所用的不是差分时钟就需要注意 P 端与 N 端一般不能同时分配给不同的时钟信号。图2是XILINX 系列的 FPGA 中成对的时钟,如果同时采用,则不能同时到达相同的区域,因为到达相同区域的时钟线只有一根。

图2

所以在时钟较少时最好不要同时使用成对的 P 和 S ,而是只是选择 P 或者是 N 这样就不会出现冲突的情况。

No.5、兼顾信号完整性的考虑

在分配中常常会出现总线分配的情况,同时大量的总线又有可能是同时翻转,这样就会带来一系列信号完整性的问题,故在管脚分配时尽量将大量同时翻转的信号分开。

0

0