1、AXI总线概述

AXI是ARM在1996年提出的微控制器总线家族AMBA中的一部分。AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。

-

AXI4:主要面向高性能地址映射通信的需求,允许最大256轮的数据突发传输;

-

AXI4-Lite:是一个简单地吞吐量地址映射性通信总线,是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元;

-

AXI4-Stream:面向高速流数据传输,去掉了地址项,允许无限制的数据突发传输;

2、AXI总线优势

AXI总线适合高带宽低延时设计,无需复杂的桥就能实现高频操作,能满足大部分器件的接口要求,提供互联架构的灵活性与独立性,向下兼容已有的AHB和APB接口 。

AXI主要特点如下。

-

信息流只以单方向传输,简化时钟域间的桥接。当信号经过复杂的片上系统时,减少延时。

-

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

-

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。分离的读、写数据通道,

-

增强的灵活性。AXI技术拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI技术,允许添加寄存器级来进行时序收敛。

3、AXI4的工作模式

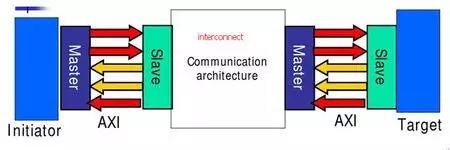

AXI总线的两端可以分为master和slave,他们直接一般通过interconnect连接,如果是一对一的话,interconnect可以没有。

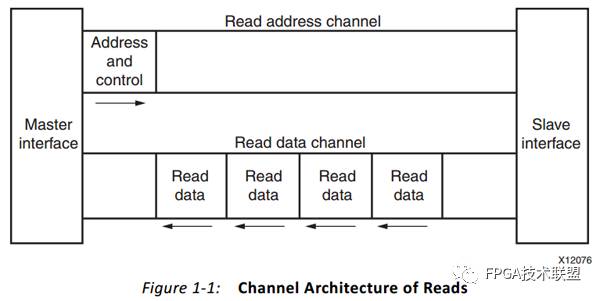

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道,极大的提高了AXI的传输性能。地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输.

4、读写时序

-

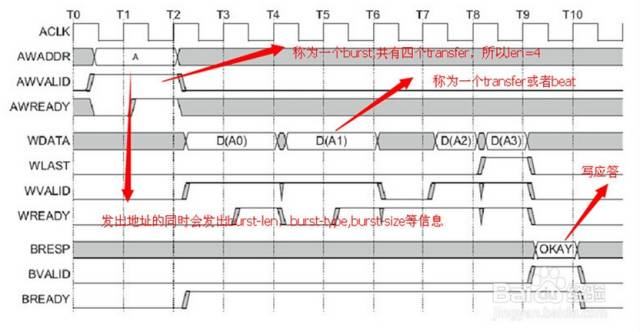

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。

-

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,直到时钟上升沿采样到从机的WREADY。

-

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。

-

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。当ARREADY为高时,从机必须能够接受提供给它的有效地址。

-

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。

5、读写时序传输内容

AXI传输首先发出burst的长度(burst-len),最大是16,burst长度就代表有多少个transfer,一个transfer就代表一个数据位宽的数据,所以一个burst最大的传输数据长度为burst_len*transfer_width;

在发出burst长度时会同时发出当前这个burst中第一个transfer的首地址,后面其它的transfer不会有地址,slave要根据地址递增的方式自己去进行相应的处理,在发出burst长度时会同时发出地址递增方式burst-type,是不变地址(non-incr),是递增还是wrap。

6、握手机制

AXI4所采用的是一种READY,VALID握手通信机制,即主从模块进行数据通信前,新根据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者A等到传输接受者B的READY信号后,A将数据与VALID信号同时发送给B.

在设计时一定不能设计一方依赖另一方,否则会出现死锁的现象,valid可以优先于ready拉高,也可以在ready之后拉高,它们并无先后关系,其实只要是master准备好就可以valid,slave准备好就可以ready,并无绝对的先后顺序,但是当两者同时为高则表示当前的data或者cmd结束或者开始下一个data或者cmd。

AXI最多支持16个master,16个slave,它们可以通过AXI interconnect连接,不同的master发出的id可能相同,但是经过AXI interconnect处理后会变得唯一,所以自己开发AXI interconnect也要注意这个问题。同一个master发出的id可以相同也可以不同,相同的id数据传输必须按照先后顺序否则会出现错误,不能乱序和交叉。AXI 支持ID方式,这也是该总线效率较高的一个原因.

7ZYNQ中的AXI总线

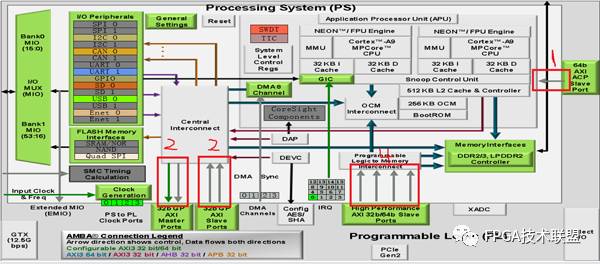

ZYNQ中的AXI接口共有9个,主要用于PS与PL的互联,包含以下三个类型:

-

AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

-

AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

-

AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

-

0

0