在硬件设计中,理论上设计好的产品在打板回来之后,就会进行相应功能的测试,硬件测试来验证所设计的硬件是否有问题,是否能够达到预期。

这其中可以通过量测相关的电路信号来检查是否有一些电路设计不合理的隐患。对于一些常见的信号质量问题如过冲,毛刺,回勾,振荡等等都可以在信号质量量测中来进行检查,因为这些会对正常的电路逻辑造成干扰,影响硬件产品整体的性能和功能。

以下是常见的信号质量问题,看一下有没有经历过。

信号边沿缓慢

信号边沿缓慢也就是上升时间或下降时间所花的时间比较长(比预期长)。这种现象会使得实际应用中出现问题。

它对于电路的危害主要体现在可能因为上升、下降的缓慢,使得在数据信号采集时,造成数据采集错误,从而导致电路运行逻辑出现混乱与故障。

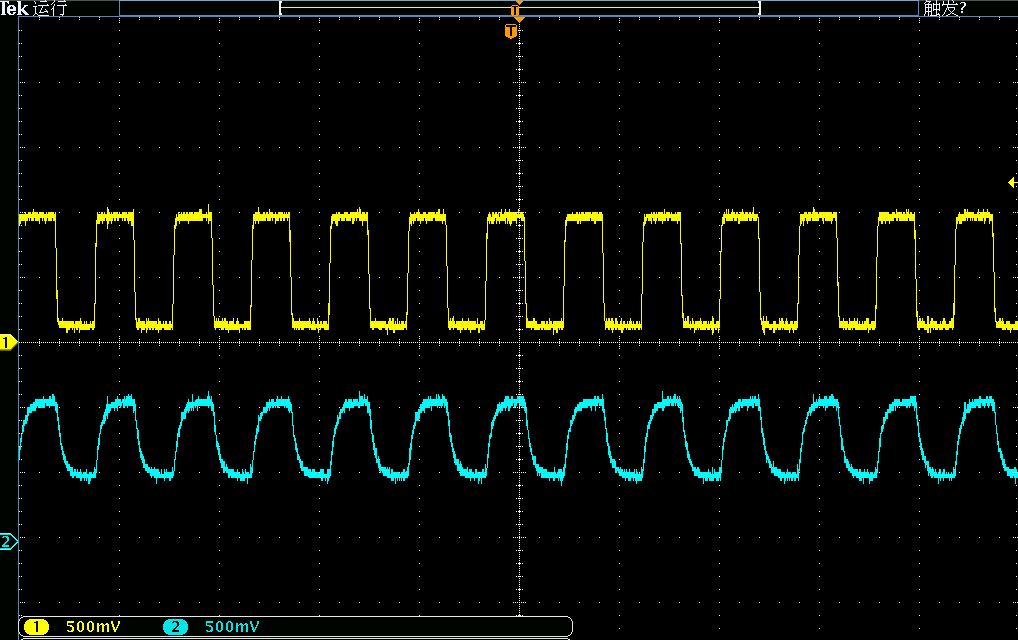

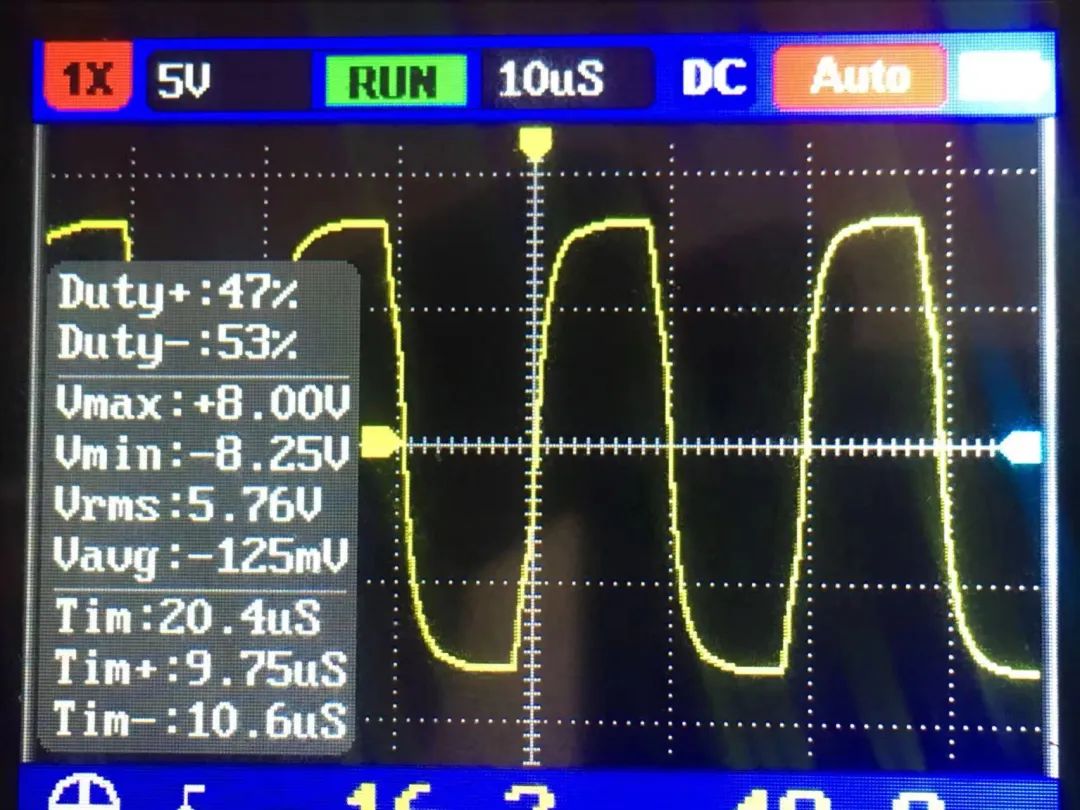

比如说上图中的波形,原本应该是一个方波的形状,但是因为信号边沿缓慢,就使得整个波形上升沿和下降沿都变得有弧度,很容易使得采样数据错误或是其他一些异常情况发生,可靠性下降。

所以在很多信号协议中对于上升时间和下降时间有做详细的测试标准,比如说12C协议,对于实际某个硬件设计中加入了的,就需要测试12C信号的 Rise time 和 Fall time,如果实测时间大于相应芯片所定义的12C信号的 Rise time和 Fall time,那就是设计存在问题的产品,需要进行设计改善。

一般信号边沿缓慢产生的原因主要可能是驱动能力不足或者是负载过大,导致信号边沿比预期所花的时间更长。

对于信号边沿缓慢的情况,解决的角度可以针对性的从原因角度去分析,也就是可以通过提高驱动能力或者减小负载的两种方式来改善信号边沿缓慢的现象。

提高驱动能力:把驱动能力提高,确保信号能够快速并且符合预期的转换电平状态

减小负载:降低负载的消耗,减少信号处理系统对电源的需求,进而降低对驱动的负担

所以当碰到信号边沿缓慢的问题时,需要特别注意信号的采集问题,同时采取相应的措施来改善信号边沿缓慢的现象,保证最终设计出来的硬件产品稳定性和可靠性。

0

0