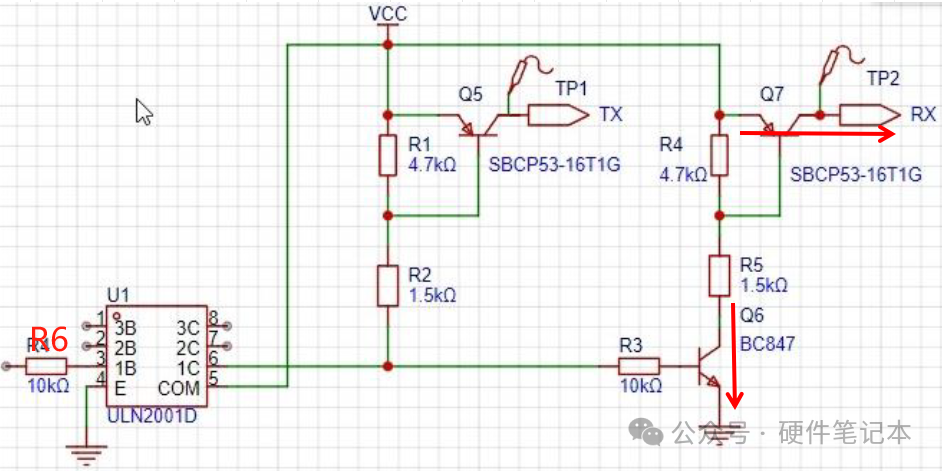

咱先不管这图的实用性,拿到电路图首先应该想到的是,这电路图主要想实现一个什么样的功能,然后再逐一分析。

咱先不管这图的实用性,拿到电路图首先应该想到的是,这电路图主要想实现一个什么样的功能,然后再逐一分析。

功能要求:

假设VCC为12V,

当R6输入为高电平,则TX 输出为12V,RX输出为0。

当R6输入为低电平,则TX输出为0V, RX输出为12V。简单说,就是想实现一个IO口控制数据的收发,且将数据扩大为其它电压VCC(可调),为什么用IO口不直接去控呢?因为单片机IO口一般都是3.3V,要想控制12V,只有通过电平转换电路的方式。收的时候不能发,发的时候也不能收。于是乎,加一个NPN三极管就可以实现反向。好,功能搞清楚了,下面咱们来一步步分析一下:

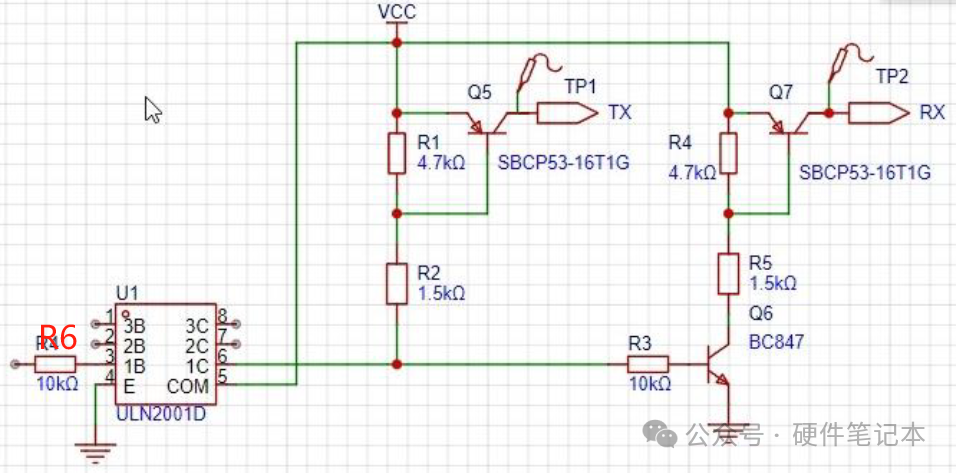

1、芯片U1

芯片U1不影响整个电路的分析,可以先不管它,它是个达林顿管,就是多个三极管复合而成,你也可以看成是个三极管,用法都一样,不过达林顿管的驱动能力比三极管强多了,在这里的主要作用就是增强驱动能力。

2、当R6输入为低电平时

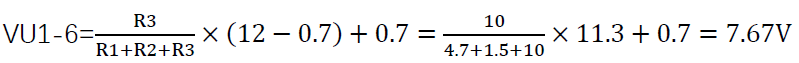

2.1 U1-3脚为低电平时,U1-6脚被外部电阻R1,R2拉高,拉高后的电压为:

2.2 Q5三极管分析

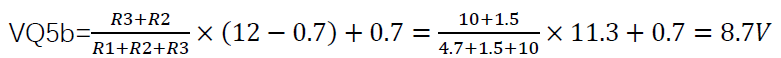

Q5 基极电压为:

Q5的Vbe=12V-8.7V=3.3V ,大于0.7V 所以Q5导通。此时,TX=12V,为高;

Q5的Vbe=12V-8.7V=3.3V ,大于0.7V 所以Q5导通。此时,TX=12V,为高;

由2.1得知,Q6的基极电压为7.67V,大于0.7V,所以Q6导通。

由2.1得知,Q6的基极电压为7.67V,大于0.7V,所以Q6导通。

Q6集电极电压接近0V,同理 Q7的Vbe大于0.7V,Q7导通,则RX输出为12V,为高。

综上所述:当输入为低时,输出TX为高,RX为高。跟要求的功能相反,此处电路有问题。

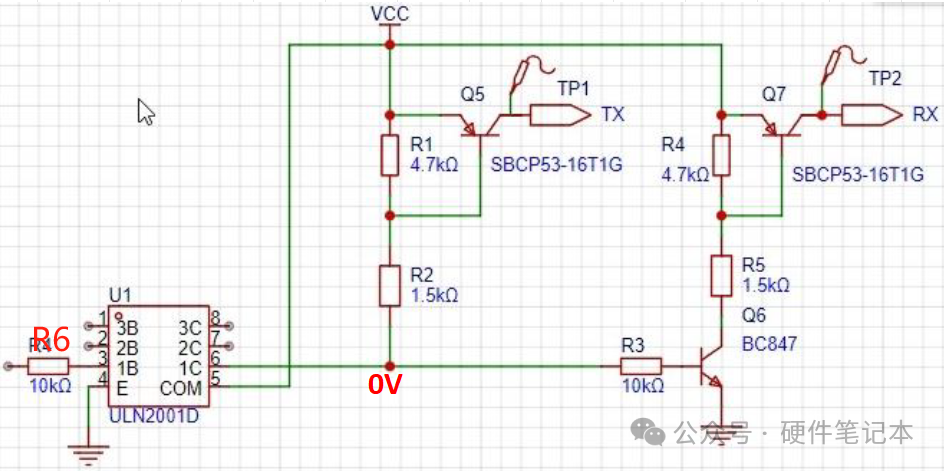

3.1 U1-3脚为高电平时,U1-6脚被拉低,拉低后的电压为0,

即:U1-6=0V

3.2 Q5的Vbe>0.7V(这里简单,大家自己算),Q5导通,TX=12V,为高。

3.3由于U1-6=0V,所以Q6截止,那么Q7也就截止,RX输出为0V。

综上所述,当输入为高时,输出TX为高,RX为低,满足要求。

所以本电路就只有一个问题:当输入为低时,输出TX为高,RX为高。即:那么当输入为低时,怎么让输出TX也为低?

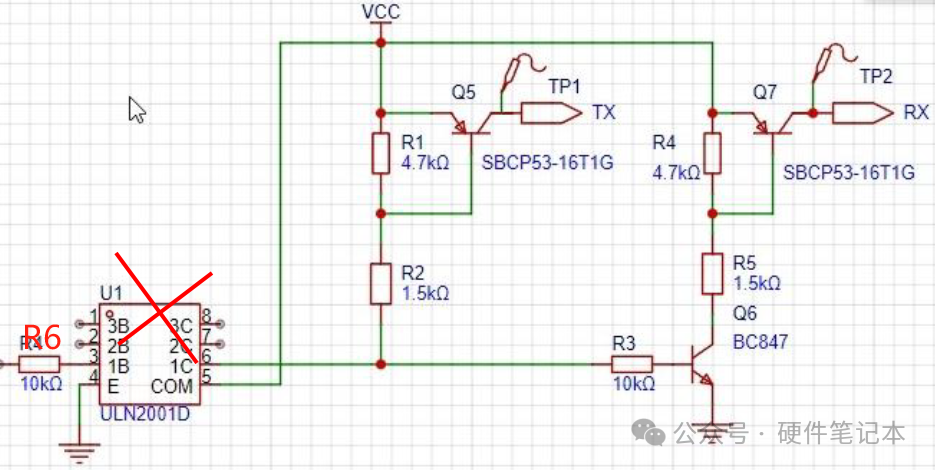

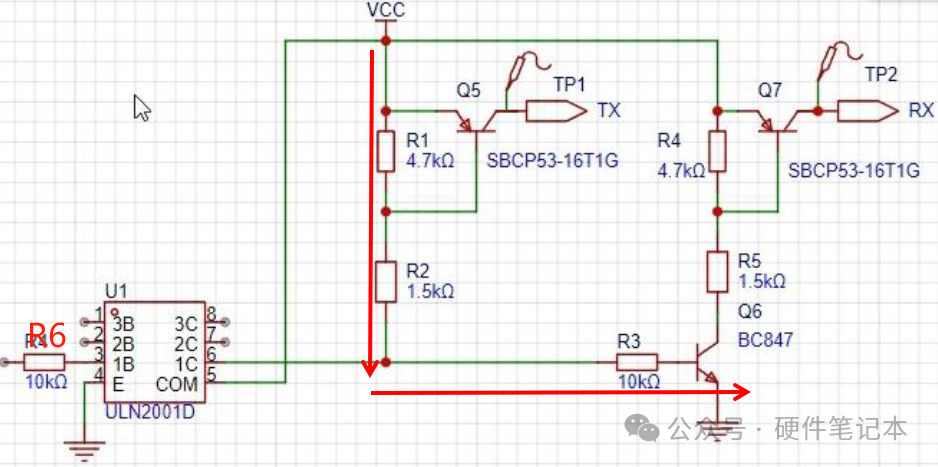

王工仔细观察,不需要删减任何电路,通过更改电阻R1的阻值就可以解决问题。有兄弟问我是怎么想的,授人以鱼,不如授人以渔。请大家看红色箭头所示回路,为什么要看这条回路呢?你想啊,你的目地是改变三极管Q5的开关,但是你发现没,无论输入电平怎么变化,三极管Q5完全没受控制,一直导通。那为什么不受控呢?那是因为三极管基极电压再怎么变化,Vbe压差始终>0.7V,你让他压差<0.7V不就行了,通过计算<300R可实现功能。

小结: 王工只是粗浅的分析本电路,实现了产品的基本功能,真正用在产品上考虑的会更多,比如上下电,三极管的温漂,功耗,还有就算一个没问题,小批量甚至量产是否都OK呢。软件BUG可以升级,硬件BUG只能改板,试错成本高,所以硬件需谨慎。

0

0