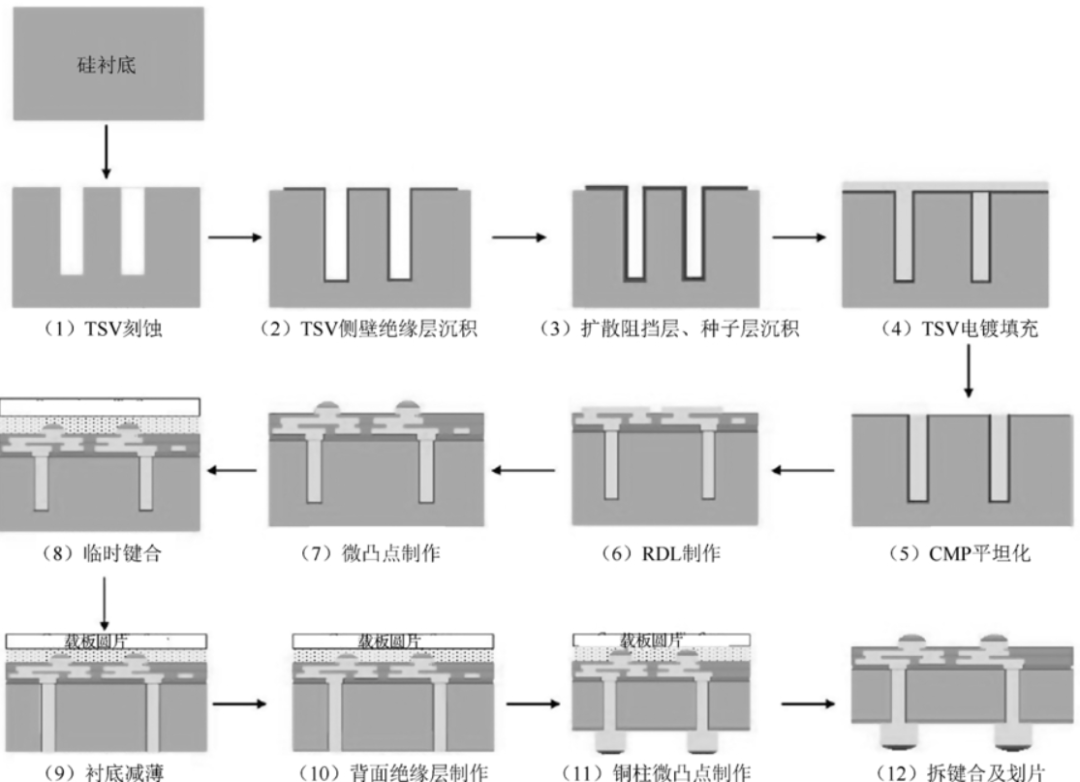

TSV中介层结构与其工艺设计有着密切的关系,图1所示为一种典型的TSV中介层制造工艺流程。

关键工艺步骤包括:

(1)TSV 刻蚀。深层离子体刻蚀工艺和激光钻孔均可以在硅衬底上制作深孔,但BOSCH刻蚀工艺由于刻蚀速率快、各向异性刻蚀深宽比高,成为目前应用最广的制作TSV的技术。

(2)TSV侧壁绝缘层沉积。由于硅衬底是半导体材料,所以必须在硅衬底与铜TSV之间制作绝缘层,TSV深孔内的侧壁绝缘层一般使用SiO2。为了获得较好的SiO2覆盖率,通常采用PECVD的方法来制作绝缘层。

(3)扩散阻挡层、种子层沉积。为了阻挡铜离子向硅衬底中扩散,需要沉积一层Ti作为阻挡层,再沉积一层铜作为种子层,为下一步电镀填充通孔的进行做准备。

(4)TSV电镀填充。为了均匀填充TSV深孔,需要采用自底向上的电镀方法。

(5)CMP平坦化。去除电镀过程中衬底表面的多余铜。

图1 一种典型的TSV中介层制造工艺流程

(6)RDL制作。制作互连线,实现电气互连。

(7)微凸点制作。为实现中介层与芯片的互连,需要制作正面微凸点。

(8)临时键合。在硅片减薄工艺中,硅片需要承受很大的机械应力,为了增大硅片的机械强度防止硅片在加工中破碎,将制作好TSV和互连的硅片与另外一个承载片(Carrier Wafer)临时键合到一起。

(9)衬底减薄。为了形成TSV,对临时键合硅片背面进行减薄加工,露出TSV。

(10)背面绝缘层制作。与正面绝缘层一样制造背面绝缘层。

(11)铜柱微凸点制作。为了实现TSV中介层与封装基板的互连,制造铜柱凸点。

(12)拆键合及划片。拆除承载片,并划片得到单个的TSV中介层。

中介层工艺研究

基于TSV工艺技术进行中介层单项工艺技术的开发,并完成整个中介层工艺的集成,最终完成中介层的制作。

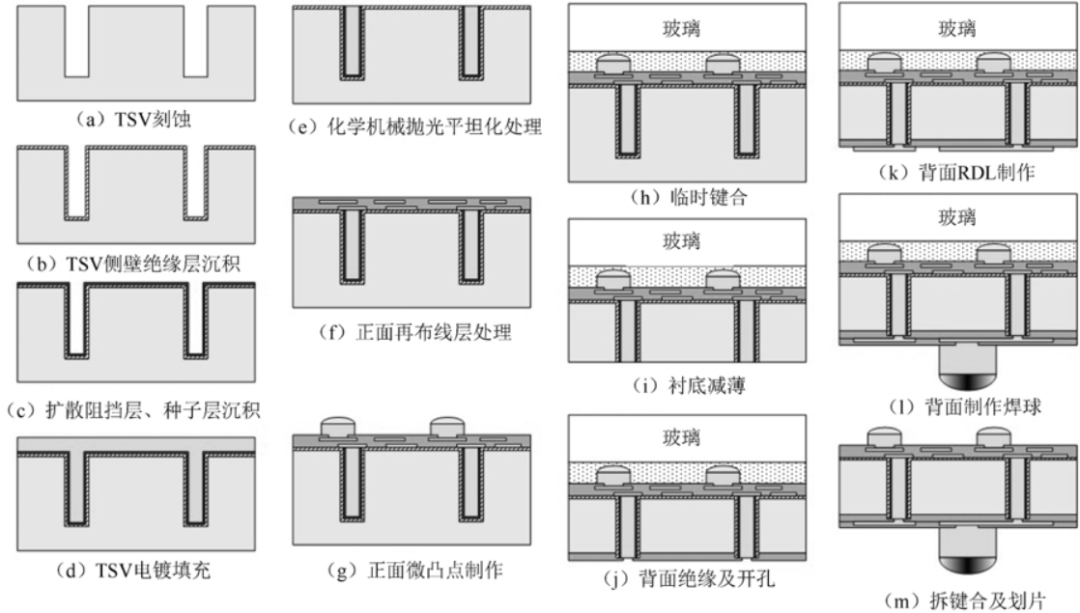

在完成芯片封装基板电性能协同设计及仿真的基础上,根据高性能CPU封装信号完整性设计与电源完整性,以及高性能CPU封装的热及机械应力特点的要求,确定了中介层整体工艺方案。在中介层整体工艺方案确定后,根据整体工艺要求对各单项工艺进行指标分解,完成包括TSV光刻、高深宽比TSV刻蚀、兆声波清洗、绝缘层制作、高深宽比黏附层种子层制作、TSV电镀填充、厚铜层化学机械抛光工艺、正面再布线制作工艺、TSV圆片临时键合工艺、圆片减薄工艺、TSV背面露头工艺、背面钢柱制作工艺及拆键合工艺等单项工艺的开发,实现中介层工艺集成。以下实例经过了8层光刻,约120个工艺步骤,图2展示了TSV中介层的主要工艺流程,按流程完成中介层芯片的制作。

图2 TSV中介层的主要工艺流程

实例为了满足电源线的电流承载能力要求,中介层采用了深宽比为6∶1的TSV(深120μm,直径为20μm)结构。正面两层再布线层,利用焊盘引出;背面为铜柱结构。

-

TSV刻蚀工艺开发

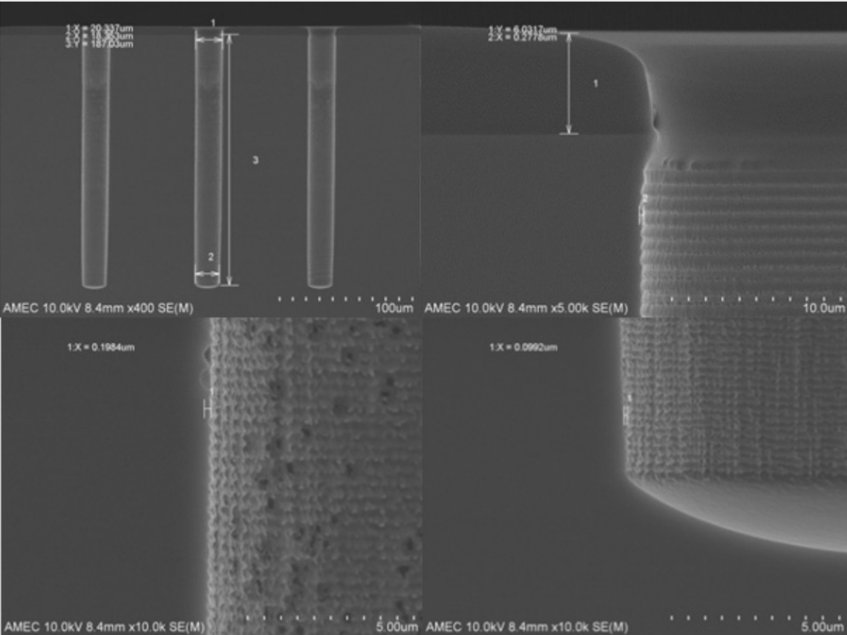

TSV刻蚀将形成高深宽比的盲孔结构,其形貌、尺寸甚至侧壁粗糙程度都将对后续工艺产生影响。当前,业界主流的TSV刻蚀工艺是Bosch刻蚀工艺。本实例中TSV刻蚀均采用Bosch刻蚀工艺技术,最终光刻和刻蚀的关键尺寸偏差约1μm以内,最高深宽比可以接近10∶1(见图3)。

Bosch 刻蚀工艺利用 C4F8 反应产生聚合物进行侧壁保护,从而实现高深宽比的盲孔结构,这些非挥发性的聚合物在保护侧壁的同时也会作为刻蚀残留物存在于圆片表面和 TSV 内。由于刻蚀反应腔室内环境复杂,刻蚀工艺时间长,刻蚀过程产生的聚合物还可能和光刻胶混合,形成更为顽固的残留物。随着TSV深宽比的进一步提高,TSV清洗工艺所面临的挑战将进一步提高。在研究过程中,研究团队还与盛美半导体设备(上海)股份有限公司开展了基于兆声波工艺的高深宽比TSV清洗研究,利用兆声波改善清洗药液在TSV内的浓度分布,并利用兆声波能量对残留物进行物理清洗。TSV刻蚀工艺刻蚀后的贝壳纹小于80nm,刻蚀后TSV清洗困难,通过对清洗工艺进行优化,清洗后未发现残留物(见图4)。

图3 利用Bosch刻蚀工艺完成的TSV形貌

图4 兆声波清洗后TSV内未见异常

2. 绝缘层沉积

TSV内绝缘层用于实现信号线和电源线与中介层衬底的绝缘,TSV内绝缘层的质量将直接影响中介层的信号完整性和电源完整性参数,是保证中介层性能的关键因素之一。由于TSV深宽比较大,传统的CVD成膜技术无法满足其台阶覆盖要求。本实例与沈阳拓荆科技股份有限公司合作,开发了高深宽比TSV的绝缘层沉积技术,要求TSV内绝缘层台阶覆盖率不小于12.5%。

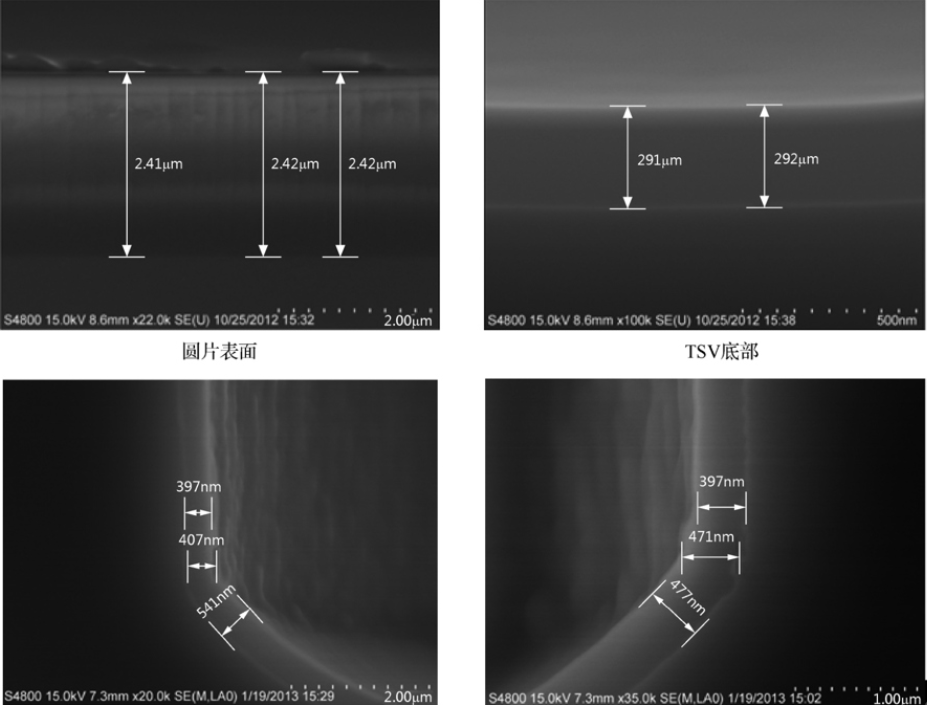

绝缘层沉积采用PECVD工艺,深宽比为6∶1的TSV的台阶覆盖率约为16.7%,最薄弱点SiO2厚度为200nm。TSV绝缘层沉积效果如图5所示。

图5 TSV绝缘层沉积效果

3. TSV填充工艺

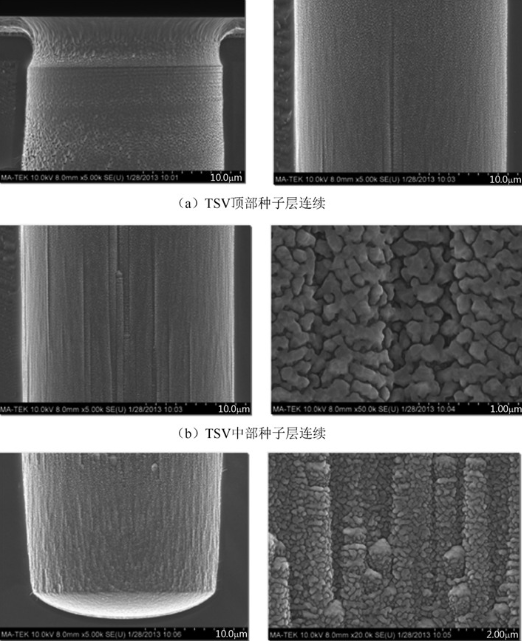

TSV填充工艺分为黏附层种子层制作和电镀填充两步工艺。TSV黏附层肩负着阻挡铜向中介层衬底硅中扩散和增加铜与硅之间黏附性的双重任务。黏附层工艺的好坏除了直接影响种子层黏附效果,还会影响整个多芯片集成系统在使用寿命中的性能稳定。黏附层一般选择Ti、Ta、TiN、TaN等材料,本实例采用北方华创Polaris T系列PVD设备,用Ti作为深宽比为6∶1的TSV中介层的黏附层,黏附层种子层的厚度分别为Ti 500nm、Cu 2μm,经过电镀首板检查及电镀工艺验证,TSV底部起镀和黏附效果可以满足要求。TSV PVD种子层沉积效果如图6所示。

图6 TSV PVD种子层沉积效果

4. TSV电镀后退火及CMP工艺

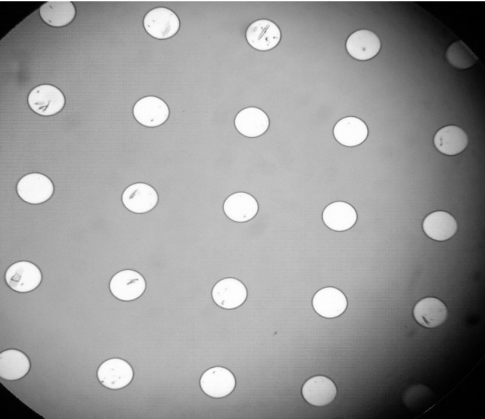

在TSV流程中,CMP工艺的作用主要是去除电镀后圆片表面的铜并对TSV表面进行整平。中介层TSV电镀后圆片表面铜层厚度一般为2~8μm,利用CMP工艺可以获得较好的表面平整度,缺点是工艺成本较高。CMP工艺后TSV俯瞰图如图7所示。除了CMP工艺,还可以采用湿法刻蚀工艺去除表面金属,但是采用该工艺后TSV口部的平整度会比采用CMP工艺差。

图7 CMP工艺后TSV俯瞰图

5. 中介层正面RDL工艺

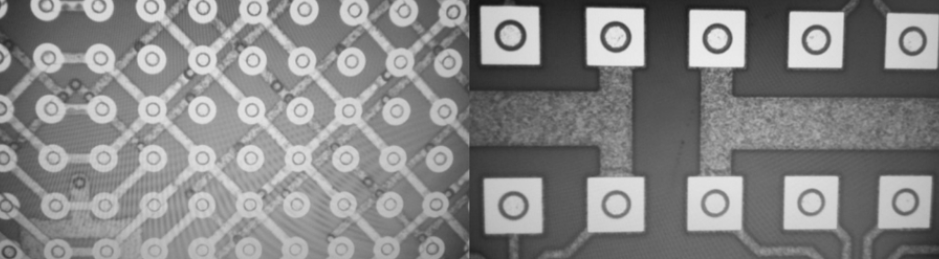

RDL是为实现2.5D集成系统中多个芯片的电互连而在中介层上制作的电流路径和介质隔离层的统称。本实例采用两层RDL,一层焊盘结构,实现了TSV衬底与CPU的直接电学连接。为保证中介层整体性能,在RDL工艺之前需完成Via工艺,采用聚合物材料作介质层。由于该工艺采用常规再布线工艺,在此不再分步阐述,图8是正面RDL工艺效果图。

图8 正面RDL工艺效果图

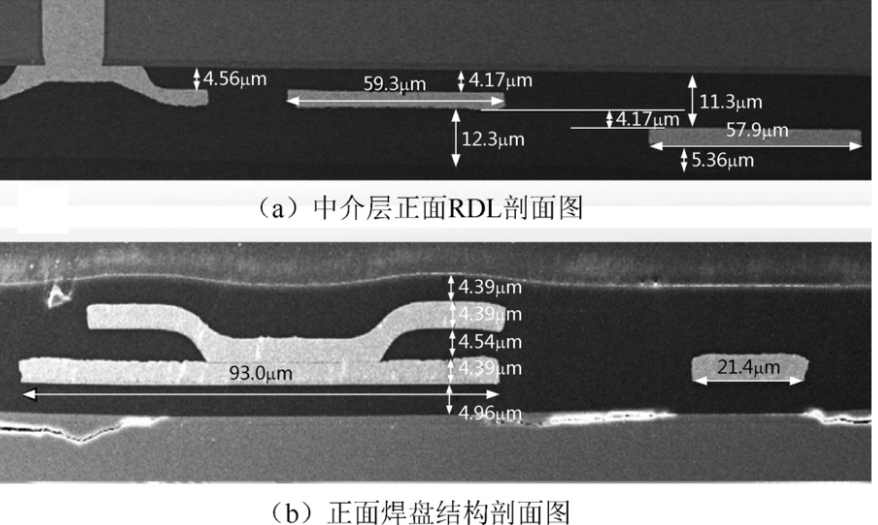

图9所示为中介层正面RDL和正面焊盘结构剖面图。在中介层中,第一介质层厚度约为4.5μm,RDL铜层厚度约为4.39μm;最细线宽为21.4μm,焊盘下开口直径为25.1μm,上开口直径为95.7μm,倾角为40.5°,镍层厚度为1.71μm,金层厚度为0.28μm。

图9 中介层正面RDL和正面焊盘结构剖面图

6. 背面露铜工艺

背面露铜工艺是最终形成TSV结构的关键步骤,目前TSV背面引出方案可以分为抛光和刻蚀工艺两种方案。研磨抛光工艺主要采用背面研磨结合CMP工艺进行背面露铜,该方案对TSV绝缘层和阻挡层没有选择性,TSV露铜的时候TSV内填充的铜会直接露出,造成金属沾污的风险。为了控制金属离子沾污,可以控制抛光工艺的量,在去除表面缺陷后即停止工艺,然后利用硅刻蚀工艺进行背面刻蚀,由于硅刻蚀工艺对TSV绝缘层的刻蚀速率很低,所以在TSV露出时可以保留完整的绝缘层和阻挡层,从而保证工艺过程中不会引入金属沾污。

7. 临时键合工艺

中介层需要双面处理,减薄后需要与载片键合在一起进行后续背面工艺,以降低对工艺设备的要求,提高成品率。键合工艺一般分为两种:如果载片是功能性的,键合后不再需要拆键合,这种键合称为永久键合;如果载片是非功能性的,在背面工艺完成后还需要拆键合,这种键合称为临时键合。

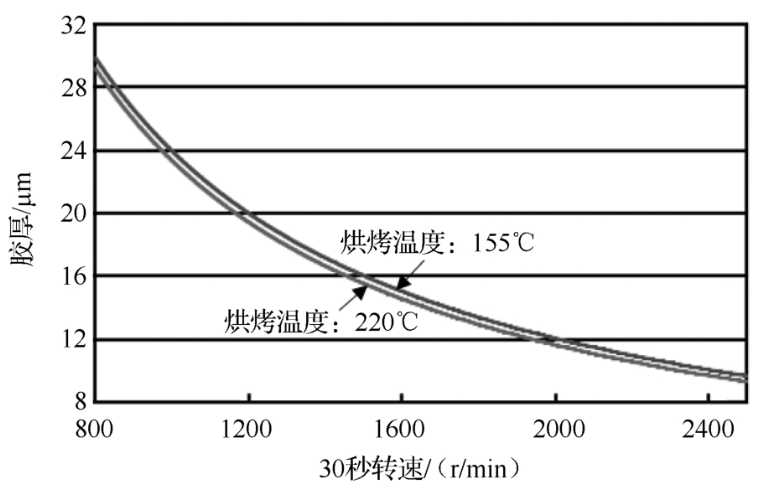

(1)键合前处理工艺。临时键合胶旋涂工艺是进行圆片背面处理的第一步关键工艺,如果旋涂厚度不均匀将导致后续背面研磨过程中TSV圆片厚度均匀性变差,使后续TSV背面露头工艺难度增加。经实验确认,本实例采用的临时键合胶为HT10.10,胶厚为20μm,转速为1000r/min。图10所示为胶厚与转速的关系曲线。

图10 胶厚与转速的关系曲线

(2)预烘烤工艺。根据键合胶热重分析(Thermogravimetric Analysis,TGA)测试结果可以发现,在整个烘烤过程中,热失重分为两个阶段:第一阶段,在117℃时大量溶剂挥发;第二阶段,在大约180℃时热失重曲线趋于稳定。根据以上分析确定预烘烤温度为120℃和180℃两种,可以有效减少键合胶的热失重对键合质量的影响。

0

0