碳化硅金属氧化物场效应晶体管(SiCMOSFET)具有高压、高频、低导通损耗等优异特性而获得产业界广泛关注,但相比于硅 基 IGBT,SiC/SiO2栅氧界面高缺陷密度导致的栅氧可靠性问题成为制约 SiC MOSFET 器件规模化应用的关键瓶颈。通过对近年来国内外 SiC MOSFET 栅氧可靠性研究成果的梳理和分析,阐述了当前栅氧可靠性问题的形成原因,归纳总结了各类常用的栅氧可靠性评估方法, 并进行了比较分析,最后重点探讨了极端工况下 SiC MOSFET 栅氧可靠性及其提升技术的发展现状。

01引言碳化硅金属氧化物半导体场效应晶体管 SiC MOSFET(silicon carbide metal-oxide-semiconductor field effect transistor) 具有低导通电阻、高频、高压等特点而广泛应用于电动汽车、轨道交通、智能电网等领域,并成为当前功率器件研究的热点之一。然而相比 Si IGBT,SiC/SiO2界面缺陷密度比 Si/SiO2高出 1-2 个数量级,较高的缺陷密度会引起栅氧 质量的显著降低,造成器件实际应用中严重的可靠性问题,这已成为 SiC MOSFET 器件规模化实际应用的“最后一 公里”问题。为了有效评估 SiC MOSFET 器件的栅氧质量,经时击穿(TDDB)、高温栅偏(HTGB)等加速老化测试 被用作栅氧可靠性评估手段,通过预测器件工作寿命及监测器件静态参数变化,为 SiC MOSFET 器件长期可靠工作提 供参考。此外,实际应用中 SiC MOSFET 器件会受到例如短路(SC)、非钳位感性负载开关(UIS)等瞬态极端应力 冲击,从而出现器件阈值电压漂移或栅极损坏失效等可靠性问题。因此,为了提高 SiC MOSFET 器件的栅氧可靠性, 国内外大量研究聚焦碳化硅栅氧生长工艺的优化与改善,例如氮、磷退火、高 k材料等。氮退火可显著降低 SiC/SiO2 界面缺陷密度,提高阈值电压稳定性,但在高温退火过程中引起的界面缺陷再生成限制了它对栅氧质量的进一步提升。高 k 材料的引入虽然可以降低栅氧电场强度,减小栅泄漏电流,然而在 400-700℃制造过程中生成的亚氧化物会造成 SiCMOSFET 栅氧可靠性退化。因此,针对以上介绍的栅氧质量提升方法还需要更深入的研究。综上所述,SiC MOSFET 器件栅氧问题是制约其未来发展的关键因素,全面总结与分析 SiC MOSFET 栅氧可靠性问题对于进一步了解其栅氧失 效机理具有重要意义。因此,本文全面综述了 SiC MOSFET 栅氧可靠性问题形成原因、栅氧质量评估、极端工况下栅 氧可靠性和栅氧质量提升方法等,最后对栅氧可靠性研究进行了总结。

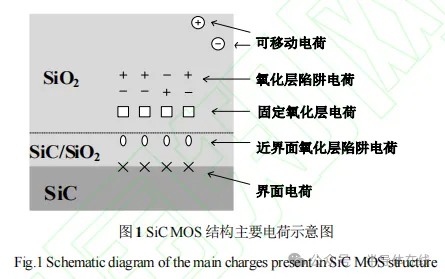

02栅氧可靠性问题形成原因由于 SiC MOSFET 热氧化过程中碳簇等缺陷的形成,导致 SiC/SiO2界面存在大量缺陷电荷,图 1 显示了 SiC/SiO2 界面处的主要缺陷类型,界面缺陷电荷分为可移动电荷、固定氧化层电荷、氧化层陷阱电荷、近界面氧化陷阱电荷和 界面电荷。其中 SiC MOSFET 栅氧化层中的可移动电荷通常是由氧化工艺阶段的碱金属污染所造成,在栅氧中的主要 存在形式为 K+和 Na+离子,它们会在高温高电场下发生迁移,影响阈值电压(Vth)的漂移。氧化层固定电荷的产生是由 热氧化过程中未形成完整晶格的深能级悬挂键、碳团簇和低价氧化物等缺陷所引起的,并且它无法与衬底进行电荷 交换,只有进行低温退火可有效降低固定电荷密度。氧化层陷阱电荷的形成是由于 SiO2 生长过程中自身氧化缺陷及 CO 残留所引起的缺陷陷阱,可通过粒子辐射、热载流子注入和 F-N 隧穿捕获电荷。氧化层陷阱电荷位于栅氧化层体 内,具有较大的捕获和释放时间常数,主要影响 SiC MOSFET 的阈值电压长期稳定性及栅氧可靠性。近界面陷阱电荷 相比氧化层陷阱电荷更靠近 SiC/SiO2界面,分布在 SiC 和 SiO2之间几纳米厚度的过渡层区域。这类陷阱主要来源于界 面附近的氧空位缺陷,这些氧空位的形成是由于过渡层中 Si 和 O 元素的比例失衡所导致的。近界面陷阱相比氧化层 陷阱电荷具有更短的捕获和释放的时间常数,表现为更容易捕获和释放电荷。界面态陷阱电荷的形成源于界面处悬挂键、晶格失配等结构缺陷,主要分为施主型缺陷和受主型缺陷:施主型缺陷的分布靠近价带,在没捕获电子的状态下 显正电,捕获电子后不带电;受主型缺陷的分布靠近导带,在没捕获电子时显中性,捕获电子后带负电。器件正常工 作时,界面电荷和近界面陷阱电荷会捕获电子和空穴,造成阈值电压漂移,氧化层陷阱电荷在高温高电场下捕获电子 和空穴,造成器件栅氧泄漏电流的增大和阈值电压永久性漂移。另一方面,由高斯定理可知,SiO2 介电常数比 SiC 低 2.5 倍,由于功率 SiC MOSFET 工作时栅压较大,导致栅氧层容易承受超过 3MV/cm 以上的电场强度,这会造成严 重的可靠性问题。最后,作为宽带隙材料,SiC 和 SiO2之间的能带偏移量远低于 Si 和 SiO2之间,SiC/SiO2界面的隧穿 势垒降低至 2.7eV,使得电子更容易发生隧穿。因此,在相同电场下,SiC MOSFET 器件的栅极隧穿电流要远远高于硅基器件。

针对 SiC MOSFET 的栅氧可靠性问题,准确的栅氧质量评估方法对器件工作寿命的预测和栅氧可靠性机理研究具 有重要意义。目前常用的栅氧可靠性评估方法有:经时击穿(TDDB)、高温栅偏(HTGB)和高温交流栅应力(ACHTGS)等。

3.1 经时击穿(TDDB)

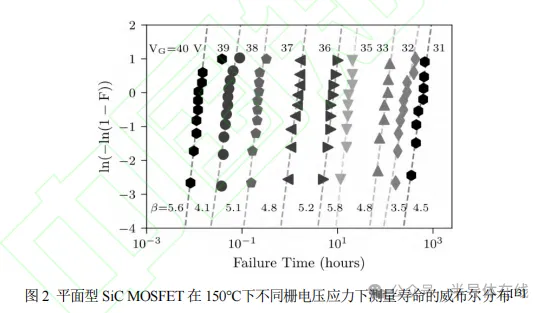

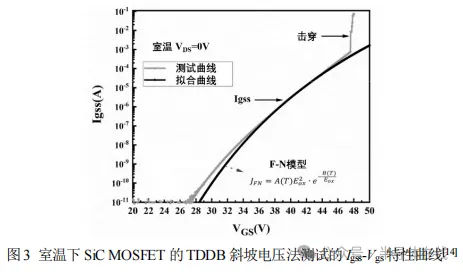

TDDB测试自上世纪90年代起已被广泛用于功率MOSFET栅极氧化物的质量评估,根据器件外加电场的方式, TDDB 寿命预测可分为恒定电压(电流)TDDB 和斜坡电压(电流)TDDB,其中恒定电压法常通过施加一低于氧化 物击穿电压的恒定电压来预测器件的栅氧寿命,而斜坡电压法常用于获得栅极泄漏电流的变化趋势和提取栅氧化物击 穿电场。恒定电压法可以获得不同栅压和温度条件下 SiC MOSFET 的失效时间,并通过威布尔统计分布来评估器件的 栅氧质量,并进一步推测出栅氧化层的使用寿命。图 2 显示为平面型 SiC MOSFET 在 150℃下恒定电压法 TDDB 测试 的栅氧寿命威布尔分布图,可以看出随着施加栅压的增大,器件的失效时间逐渐减小,其中 β 是威布尔斜率参数,失效时间的变化越小,β 越大,表明栅极氧化物均匀性越好。图 3 显示室温下 SiC MOSFET 的 TDDB 斜坡电压法测试 的 Igss-Vgs特性曲线,可以看到,栅极泄漏电流在氧化物击穿之前呈指数增长,其中 F-N 隧穿是主要导电机制。在高 温高电场应力下,由于栅氧电场增大和界面有效势垒高度降低,栅漏电流急剧增大,导致 SiC MOSFET 过早击穿。近 年来,SiC MOSFET 的栅极氧化物寿命已经取得了令人鼓舞的结果,科锐、罗姆和意法半导体等制造商在 150°C 下 对商用平面型和沟槽型 1200V SiC MOSFET 进行寿命预测,20V 栅压下商用平面型和沟槽型器件的工作寿命分别为 800 万小时和 3 亿年,15V 栅压下器件的寿命分别为 6 亿小时和 1 亿年。这源于沟槽型 SiC MOSFET 侧壁栅氧晶 面缺陷密度低于平面型器件的(0001)晶面,使得沟槽器件在较大栅应力下表现出更长的使用寿命。然而在实际工况 中,沟槽型器件引起的栅氧可靠性问题远远大于平面型器件,工作中较大的漏极电压(Vds)引起的栅氧拐角处的电场 集中会导致栅氧被击穿。因此,沟槽型器件的栅氧可靠性研究更多地集中于栅氧底部拐角处。尽管上述测试结果表明 目前商用 SiC MOSFET 的栅氧质量以得到极大的提升,然而相比 Si 器件,SiC 器件的潜在早期失效仍高出 3-4 个数量级,因此提高栅氧化层质量,以减少 SiC MOSFET 的早期失效是目前亟待突破的关键技术瓶颈。

3.2 高温栅偏(HTGB)

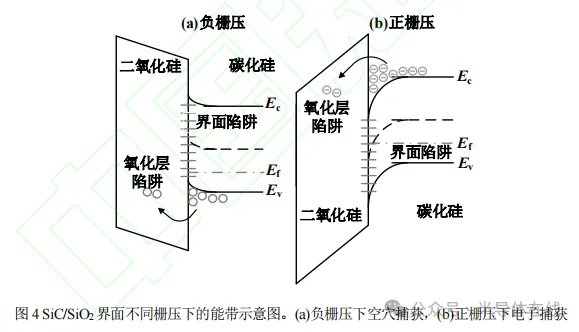

HTGB 常被用于评估 SiC MOSFET 栅氧化层的静态特性退化特性,主要包括阈值电压(Vth)、导通电阻(Ron)和 栅泄漏电流(Igss)。由于 SiC/SiO2 界面较高的缺陷密度,HTGB 测试会导致器件发生 Vth 漂移,这被称为阈值电压不 稳定性(BTI)。图 4 表示为不同栅偏置条件下 SiC/SiO2 结构的能带图,负栅压下,能带向上弯曲,栅氧化层中 空穴被捕获,Vth负漂,称为负偏置温度不稳定性(NBTI)。正栅压下,能带向下弯曲,栅氧化层中电子被捕获,Vth正 漂,称为正偏置温度不稳定性(PBTI)。Vth漂移与施加栅应力时间成幂律关系,随着应力时间延长,栅氧缺陷捕获电 荷越多,Vth漂移更显著。除栅压外,温度的变化也影响 Vth的退化量,Chen 等人研究了 BTI 与温度变化的关系, 当温度为 175℃和 200℃时,Vth 漂移量分别增加 0.17V 和 0.3V。除此之外,由于 Vth 的变化会影响器件的导通电阻, Vth正漂会引起 Ron增大,从而增强导通损耗;Vth负漂会使 Ron降低,导致关断状态下漏极电流增大,并造成器件的误 导通。在长期 HTGB 测试中,Igss会随着应力时间的延长和栅压的增大而增大,最终达到 mA 量级导致栅氧击穿;而在 较低栅压下 Igss的增大在可接受范围内,并不会造成器件失效,只会发生 Vth和 Ron的退化。

3.3 高温交流栅应力(AC-HTGS)

在实际应用中由于器件处于频繁开关状态,因此高温下的栅开关应力也会引起器件显著的栅氧可靠性问题,ACHTGS 主要评估 SiC MOSFET 动态栅应力下的静态参数退化。重庆大学 Jiang 等人研究了动态栅开关应力对 Vth的影 响,结果表明只有当开关频率较高,栅压为双极状态时才会发生显著的 Vth退化,Vth的漂移量与开关次数成幂律关系, 它与施加栅应力的时间无明显的关联。进一步研究表明,AC-HTGS 中 Vth 漂移由开关时栅氧化层的局部电场决定, 总电场可分为栅氧化层电场和 SiC/SiO2界面局部电场,在器件开关瞬间由于局部电场的增强从而加速了电子和空穴的捕获,并随着开关次数增多,更多电子和空穴被捕获进氧化层中,一部分发生复合,一部分被陷阱捕获留在 SiO2中, 最终导致 Vth正漂,并且 AC-HTGS 下的 Vth漂移最终会饱和,不会造成器件栅氧化层的击穿。此外,Zhong 等人研究发现 dVgs/dt 越高,AC-HTGS 下 Vth漂移越显著,并且负栅压对 Vth的影响大于正栅压,同时温度、频率、占空 比等影响因素也被用于研究 AC-HTGS 下 Vth的变化,但它们对 Vth退化的影响并不显著。

通过上述栅氧评估方法的总结可知,TDDB 虽然可以通过栅氧质量评估来预测 SiC MOSFET 的使用寿命,然而其 评估方式单一,忽略了器件在正常工作中会受到漏压、导通电流和极端工况等应力对栅氧的影响,导致其寿命预测的 并不准确性。而 HTGB 相比 TDDB 可以使用额定栅极电压来评估器件长期静态工况下的栅氧退化趋势,更贴近器件 实际应用中的状况,同时 HTGB 主要使用静态参数的退化来预测器件的失效。因此,在实际 SiC MOSFET 栅氧质量评 估中,可通过 TDDB 和 HTGB 的结合来更加准确地预测器件的使用寿命。AC-HTGS 主要针对 SiC MOSFET 在动态栅 应力下的栅氧退化,英飞凌研究表明,当器件开关次数达到一定时,纯栅极开关应力和沟道导通下的开关应力造成的 Vth退化趋势是相近的。因此,AC-HTGS 对 SiC MOSFET 的栅氧质量评估很符合实际工况,但其造成器件栅氧退化的 机理目前并没有形成统一的共识,尚待开展进一步的研究。

04极端工况下栅氧可靠性SiC MOSFET 在工作中常受到极端应力的冲击,包括短路、非钳位感性负载开关和浪涌电流,在这些极端工况下 器件会发生栅介质破裂、热失效和栅氧化层退化等现象。单次极端应力引起的大电流和高温环境主要造成器件发生栅 介质破裂和热失效,而重复极端应力下的器件主要发生栅氧化层退化。因此,在这里主要介绍重复极端应力下的 SiC MOSFET 栅氧可靠性研究。

4.1 重复短路

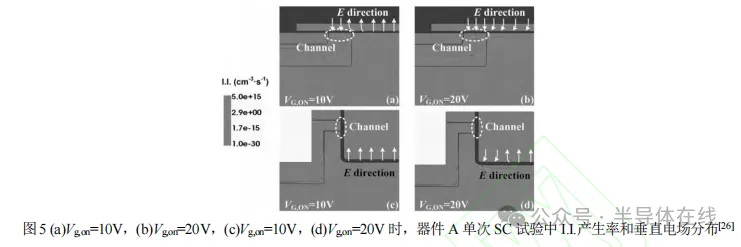

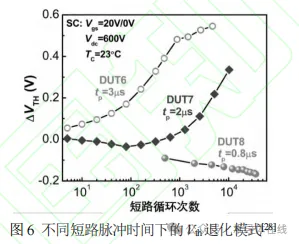

重复短路应力下 SiC MOSFET 会受到高压大电流的冲击,造成器件栅氧可靠性降低,栅氧界面陷阱电荷增多导致 的 Vth 漂移是重复短路应力下栅氧主要的退化机制。Li 等人通过仿真验证了平面型和沟槽型器件在受到不同栅 压短路应力时栅氧电场的变化,如图 5 所示:当开态栅压为 10V 时,栅氧化层倾向于对空穴的捕获,高漏压会使得 JFET 和部分沟道区发生碰撞电离并产生电子-空穴对,栅氧在漏压施加的电场下捕获空穴,使得 Vth负漂;当开态栅压 为 20V 时,沟道区的电子捕获成为 Vth 正漂的主要原因,这表明在不同开态栅压下栅氧承受的电场方向是不同的。除 栅压大小对 Vth漂移的影响外,重复短路的持续时间也会造成 Vth漂移趋势的不同,图 6 显示,当短路时间仅为 0.8μs 时,Vth发生负漂,源于大电场引起的碰撞电离产生空穴注入所致;当短路时间变长,增强了沟道区电子注入栅氧化层,Vth正漂。Yu 等人研究了平面、双沟槽和非对称沟槽器件在重复短路下的退化分析,实验结果表明平面型器件在 25℃ 和175℃下静态特性退化较小,双沟槽和非对称沟槽器件在经受一定短路应力次数后发生栅氧化层破裂,Igss急剧上升。除此之外,重复短路过程产生的巨大热应力会引起顶部源极金属局部过热发生重构,使得 Ron增大。

4.2 重复非钳位感性负载开关

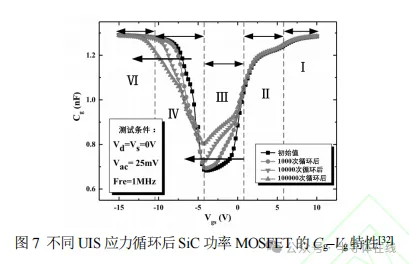

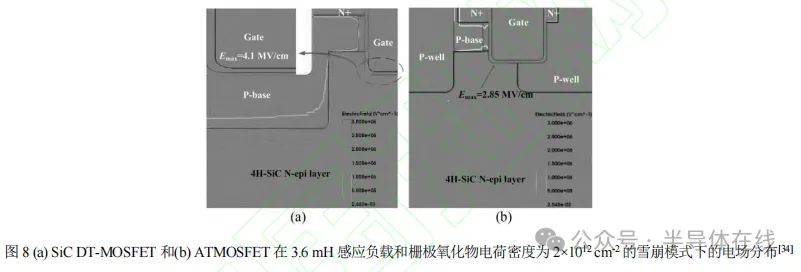

SiC MOSFET 受到重复 UIS 应力下,电流主要从 SiC MOSFET 体二极管流出,TCAD 数值模拟表明 UIS 过程中 JFET 区域碰撞电离率和垂直电场达到峰值,在较大漏极电压下 JFET 区由于高电场发生碰撞电离而产生空穴被注入上 方栅氧化层中,这是导致重复 UIS 下栅极氧化层退化的主要机制。Wei 等人研究了平面型 SiC MOSFET 经受重复 UIS 应力后栅氧在不同区域的退化趋势,如图 7 所示,Cg-Vg曲线结果显示在Ⅱ区域曲线无显著变化,而Ⅲ和Ⅳ区域 CgVg曲线负漂,进一步验证了 JFET 区上方栅氧化层对空穴的捕获。而有的报道指出,经过一定次数的 UIS 后,部分沟 道区域上方的栅氧化层也会捕获空穴,使得 Vth负漂。Deng 等人对比了双沟槽以及非对称沟槽 SiC MOSFET 的仿 真结果,如图 8 所示,重复 UIS 应力下双沟槽器件由于更大的槽栅底部氧化层电场,造成了更严重的热空穴注入,使 得双沟槽器件底部栅氧化层发生缺陷累积并最终产生电流通路;非对称沟槽器件经历重复 UIS 应力下由于栅氧承受的 电场较低,最终发生热失效。Ron 正漂是因为重复 UIS 后器件材料的热疲劳和内部热膨胀系数不同所导致的封装退化。除此之外,由于 JFET 区上方栅氧化层捕获空穴,使得 Cgd增大,Cgd增大导致器件的米勒平台持续时间增长,延 长了器件的关断时间。

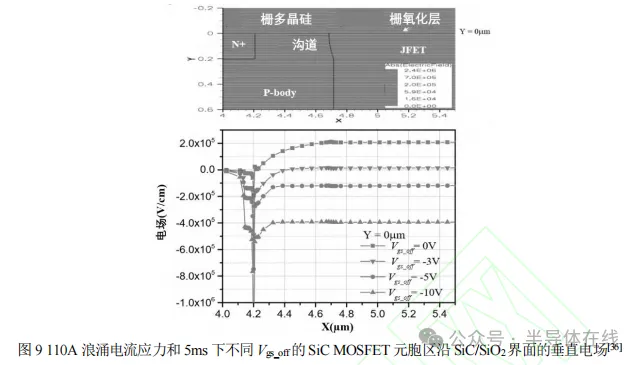

4.3 重复浪涌

SiC MOSFET 的体二极管成为电路中反并联二极管的研究被逐步报道,目前工艺技术的发展使得商用 SiC MOSFET 体二极管导通状态下的双极退化问题逐步得到改善,因此重复浪涌电流应力下的栅氧化层退化成为其主要 失效机制。研究表明,当体二极管导通并且 Vgs=0V 时,大部分电流走 SiC MOSFET 体二极管,小部分电流走沟道, 静态测试显示 Vth正漂,说明有电子被注入栅氧化层中。这源于当 Vsd>0,Vgs=0 时,栅极和 SiC MOSFET 表面沟道处 存在电位差导致沟道被开启,流过沟道的电子因电场作用被注入栅氧化层中。图 9 的 TCAD 仿真表明沟道区有大量电 子流过,当关态栅压从 0 到-10V 时,沟道区和 JFET 区电场方向发生变化,栅氧化层在电场作用下从捕获电子变为捕 获空穴,使得 Vth在栅压为 0V 时正漂,栅压为-5V 和-10V 时负漂;当关态栅压为-3V 时,沟道处电场较弱,栅氧化层 的电荷隧穿效应被减弱,因此 Vth无显著漂移。Ron随着重复浪涌电流应力而持续增大,这是由重复热应力的封装退化引起的。除此之外,有研究表明了非对称沟槽型器件受到重复浪涌应力后,即使 Vgs为 0V,Vth也发生了负漂,而在栅压为负时,Ron和 Vth等其他电性能的退化趋势与平面型器件相似。

目前 SiC MOSFET 的重要研究方向之一聚焦在如何通过 SiC MOSFET 制造工艺的改善和器件结构优化来降低 SiC/SiO2界面缺陷和栅氧电场,从而提升栅氧可靠性。常用的 SiC MOSFET 栅氧可靠性提升方法有:氮退火、高 k 材 料和结构优化等。

5.1 氮退火

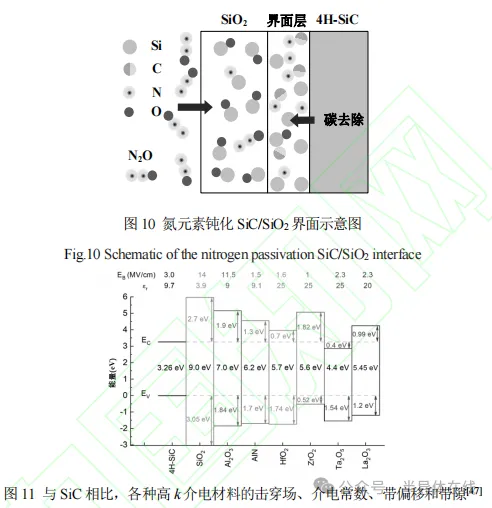

氮(N)元素退火可显著降低 SiC MOSFET 界面态密度,提升栅氧化层质量。图 10 显示 N 与 SiC/SiO2界面处 的悬挂键、C 缺陷形成 Si-N 键和 C-N 键,减少界面缺陷电荷,使得界面态密度显著降低。近年来,氮等离子体钝化 技术因其较大的钝化覆盖范围而被用于降低于 SiC/SiO2界面态密度,Yang 等人使用电子回旋共振微波(ECR)混合 N 和 O 等离子体后氧化退火 SiC MOSFET,降低界面态密度至 2.27×1012cm-2,但 PBTS 和 NBTS 显示迟滞效应仍大于 NO 退火,并且近界面氧化层电荷仍然存在。此外,N 退火在 1000-1500℃高温中会引起界面缺陷的再生成,使得 N 元 素对界面态密度的降低有一定的限制。Yang C 等人使用超临界 N2O 流体(SCN2O)改善 SiC/SiO2界面缺陷,经过 SCN2O 后氧化退火,界面态密度显著降低,栅氧化层临界电场相比 N2O 退火增加 18.19%,并且此工艺在 120℃的低 温下进行,减少了因高温氧化退火中 SiC/SiO2界面不稳定而产生新的缺陷。综上所述,N 退火技术有效地提升栅氧界 面质量,提高沟道迁移率和沟道电阻,然而,近界面陷阱电荷的存在导致退火后 SiC MOSFET 的 BTI 效应依旧未得到 显著的改善,这对于提升 SiC MOSFET 栅氧长期可靠性仍具有一定限制。

除 N 元素退火提升 SiC MOSFET 的栅氧界面缺陷技术外,磷和硼元素掺杂也可显著降低器件界面态密度。Hiroshi Yano 等人将器件置于 POCI3环境中高温退火,使得导带边缘附近的界面态密度降至 1×1011cm-2 /eV,并且 近界面陷阱密度对比 NO 退火技术更低,但在高温高栅压下的 Vth漂移量更大,这源于更多的氧化层陷阱电荷的生成。而具有更小原子质量的硼元素通过钝化工艺降低 SiC MOSFET 栅氧界面陷阱密度的同时,能够降低与氧原子结合的强 度,促进氧化物中的应力松弛,以增强栅氧质量。

5.2 高 k 材料

高 k 材料的使用可显著提升 SiC MOSFET 的栅氧可靠性,目前,改善 SiC MOSFET 栅氧化层常见的高 k 材料如 Al2O3、HfO2和 ZrO2等,图 11 表明它们具有较大的禁带宽度,能与 SiC 带隙形成合适的能带排列,避免栅极泄漏电流 的产生;较高的介电常数可显著降低栅氧化层电场,使得栅氧被击穿的风险大大降低,同时栅氧电场的降低可减小栅 氧化层的厚度,减少成本及提升栅开关速度。目前使用高 k 材料的方法是将较薄的 SiO2夹在高 k 材料和 SiC 之间形成 复合栅氧化层,可将 SiO2厚度减小至 10nm 左右,SiO2层也可作为界面屏障,可以减少高 k 材料与 SiC 因物理性质差 异而形成的界面缺陷,同时能够减轻高 k 材料与 SiC 之间产生的泄漏电流,避免在高 k/SiC 界面发生化学反应。HfO2 具有 20-25 的介电常数,尽管可以降低栅氧电场,但其能带带隙与 SiC 之间的势垒高度偏差较低,容易发生栅漏电流, 造成栅氧化层退化,因此常用来与其他高 k 材料复合以减少栅漏电流效应。大多数高 k 材料的局限性在于 400-700℃ 的制造过程中亚氧化物的形成,这种中间副产物被证明对SiC MOSFET栅氧可靠性是有害的,表现为栅泄漏电流增大。

5.3 结构优化

结构优化主要通过改变 SiC MOSFET 的器件结构以提升其栅氧可靠性。目前平面栅结构优化最新研究表明, 使用额定1200V嵌入源场板的分裂栅SiC MOSFET结构,可以将传统结构的栅氧电场从3.86MV/cm降到2.64MV/cm, 提升了阻断电压,并且开关损耗相比传统平面型器件降低 25%。针对双沟槽器件拐角处的电场集中,有研究者使用足 够深度的双 p 型基区掺杂结构改善 1200V 沟槽型器件的栅氧可靠性,较深的 p 型基区掺杂可保护沟槽拐角处的栅氧 电场,增强 SiC MOSFET 的击穿电压。此外,一种反向沟道的 SiC MOSFET 沟槽型器件新结构被提出,当器件关断 时,栅氧被接地的 p 屏蔽层所保护,没有受到显著的影响,并且开关损耗降低 64.5%。上述的器件结构优化虽然可降 低 SiC MOSFET 工作时的栅氧电场强度,然而实际生产工艺的成熟度和商业化仍需要很长的一段时间。

06结论本文通过对近年来国内外 SiC MOSFET 栅氧可靠性研究成果的梳理和分析,较全面综述了 SiC MOSFET 栅氧可靠性的研究现状。首先介绍了目前 SiC MOSFET 栅氧存在的主要问题,并对 TDDB、HTGB 和 AC-HTGS 在内的栅氧 质量评估方法进行了总结与对比。此外,对于 SiC MOSFET 在极端工况下的栅氧可靠性研究分析表明,重复短路、重 复 UIS、重复浪涌在内的极端应力会造成器件栅氧静态参数退化和封装退化,主要表现为 Vth和 Ron的退化。最后,为 提高 SiC MOSFET栅氧质量,氮退火、高 k 材料和器件结构优化等栅氧质量提升方法被整理和分析,结果表明这些方法虽然在一定程度上提高了SiC MOSFET 的栅氧质量,但由于其自身的局限性,使得改善器件长期的可靠性具有一定 的限制。综上所述,虽然本文针对 SiCMOSFET 器件目前存在的栅氧可靠性问题进行了归纳与总结,可以为此方面的 研究提供一个全面的认识和理解,但其栅氧高缺陷密度形成机制及其极端应力下栅氧损伤失效机理的物理本质上的认 识仍不明确,如何降低和抑制 SiC/SiO2界面缺陷的产生是突破 SiCMOSFET 器件栅氧可靠性问题的根本所在,只有揭 示栅氧界面缺陷形成机理并拥有更加有效的生产工艺,才能彻底地解决 SiC MOSFET 器件的栅氧问题。

0

0