-

什么是Combinational loop?

-

常见的Combinational loop 有哪些?

-

Genus 如何处理Combinational loop?

-

LEC 如何处理Combinational loop?

-

Innovus/Tempus 如何处理Combinational loop?

什么是Combinational loop

在数字集成电路中有许多许多的专有名词,特别难用一个汉语词或一段汉语句子清晰表述,有时候直接引用英文并不是为了装逼也不是偷懒,只是为了不曲解。对Combinational loop 的定义:

-

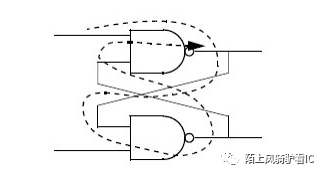

Combinational loop: A combinational feedback loop is a path that can be traced through combinational logic - back to the starting point.

-

组合逻辑环:起始于某个组合逻辑单元经过一串组合逻辑又回到起始组合逻辑单元的逻辑环路,称为组合逻辑环。

常见的Combinational loop

跟Latch 一样,Combinational loop 如果不是用于特别用途,通常是不应该出现在代码中的,所有不预期的Combination loop 都要当做bug 处理,需清除,除此之外常见的Combinational loop 有:

-

伪随机数生成器,由奇数个反相器组成的回环;

-

DFT Bypass 逻辑,在DFT 模式有组合逻辑环;

Genus 如何处理Combinational loop

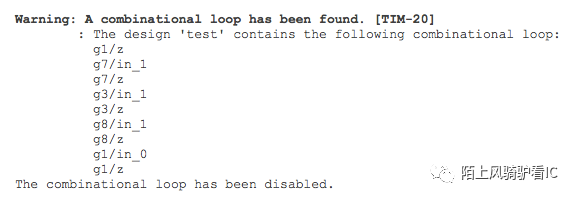

默认,综合工具都会对RTL 代码做QA 检查,当发现代码里有不期望的东西存在时就会报警,比如遇到Latch 会报警,遇到位宽不一致会报警,遇到未定义的module 会报警,遇到Combinational loop 同样会报警,在Genus 中,如果RTL 中有Combinational loop 工具会在elaborate 的时候报TIM-20 的警告:

- 交给工具处理,需要额外的分析时间,而且不一定可以得到期望的『断点』。

- 用户通过命令设置,老驴推荐这种方式,如果Combination loop 不是设计意图,请及早修掉,如果是设计意图,请在期望的点上用对应命令将其打断。

Genus 命令 check_timing_intent 检查SDC QA 时,会检查代码中的Combination loop. 如果代码中有Combination loop 且SDC 中没有对应的命令 "set_disable_timing" 将其打断,则:

- 如果在syn_gen 之前执行report_timing , 那工具会自动插入 cdn_loop_breaker;

- 如果在syn_gen 之前未执行report_timing, 那工具会在syn_gen 过程中插入cdn_loop_breaker.

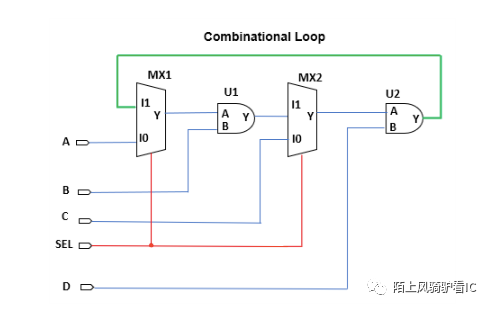

处理起来看似很简单,但是如果电路本身比较复杂,让工具自己分析去打断Combinational loop 有时候是不经济的有时候是不科学的有时候是不可行的,如下一个简单的电路:

- 有多个点可以插入loop breaker 将loop 打断,但是哪种选择是Designer 期望的?是所谓『经济』的?对于工具而言没有足够的输入信息无法做出经济的抉择;

- 在任何一个点插入loop breaker 将loop 打断都会导致某条真正的timing path 断掉,哪条path 是可以被抛弃的『子儿』,如何选择才合理公平科学?

-

对于更复杂的电路,工具分析了许久,就是找不到可以插入的点,于是工具会像个傻子一样在原地爱的魔力转圈圈。

LEC 如何处理Combinational loop

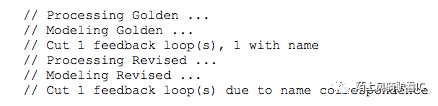

Combinational loop 在LEC 中是不允许存在的,LEC 会在modling 的时候插入CUTPOINT 打断Combinational loop, CUTPOINT 属于keypoints. LEC 插入CUTPOINT 的过程:

- LEC 在modling 时插入CUTPOINT;

- LEC 先对Golden 进行处理,并将插入CUTPOINT 的pin/net 记住;

- LEC 首先根据记录的信息在Revised 中寻找对应点插入CUTPOINT;

- 如果根据记录的对应点处理之后,还有额外的Combinational loop, LEC 会用内嵌算法进一步插入CUTPOINT

report message -modeling –verbose

通常,如果Golden 跟Revised 有相同或极类似的Combinational loop, 工具可以会找到对应的位置插入CUTPOIN, 那么都不会有什么问题。但真实case 总会有一些特别情况,如优化之后Revised 中Combinational loop pin/net 的名字完全改变,数量也有变化;如Combinational loop 跨了逻辑层;对于这些复杂情况,首先需要依靠工具内嵌算法去做分析,如可以加一些modeling 选项,打开某些更复杂的算法去分析:

set flatten model -cut_remove_redundant set flatten model -cut_place_algo 1 也可以让工具给出更多信息:set flatten model -cut_show_net

analyze setup -cut

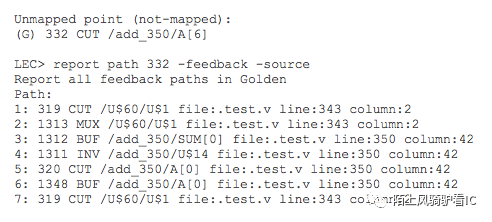

经过如上分析之后,如果还有由CUTPOIN 引起的不等,则需要进一步分析处理,可以用如下命令分别报出工具已经插入的CUTPOIN, 设计中所有的Combinational loop 及其在代码中对应的位置:

report gate -type cut

REPort PAth -feedback

report path -feedback -source

-

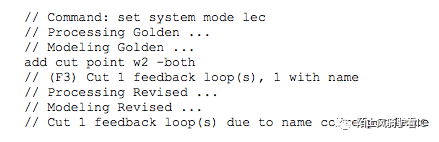

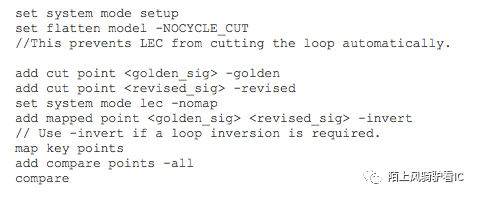

可用set flatten model -nocycle_cut 不让工具加cut point.

-

可用set analyze option -nocut 不让工具分析cut point.

-

可参考如下脚本自己加cut point.

Innovus/Tempus 如何处理Combinational loop?

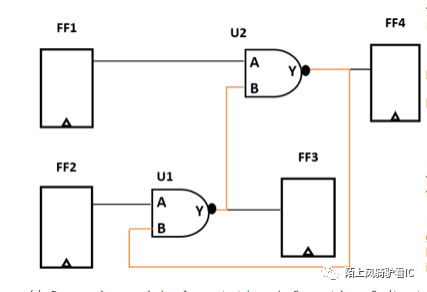

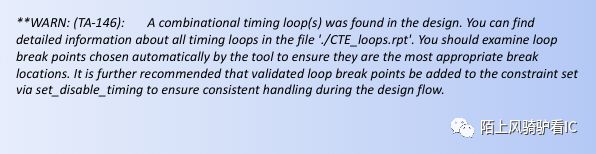

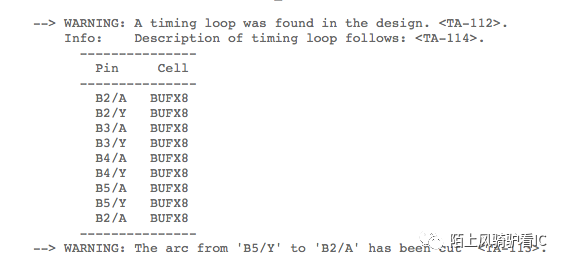

默认,Innovus 跟Tempus 见到Combinational loop 同样会报警会,并且自动将其打断。

CTE_loops.rpt 中有如下信息:

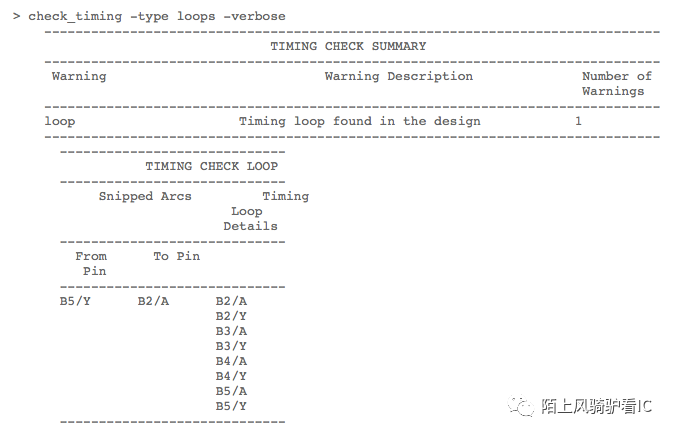

可用check_timing 报出设计中所有的Combinational loop:

timing_dynamic_loop_breaking

忠告:不论电路复杂简单,所有意图之内的Combinational loop 请用set_disable_timing 打断,所有意图之外的Combinational loop 请修掉.

写在最后,Combinational loop 是常规设计必须要规避的电路结构,如果不得不有,若交给工具,因为每个工具的算法不同,得到的结果会有差异,所以最好由硅农用命令设掉。Combinational loop 除对综合,形式验证,布局布线,静态时序分析有影响之外,对DFT 同样有影响,此处引用一段原话:

-

Long ATPG runtime

-

Long or hanging gate-level simulations (indication of an oscillating loop)

-

Failing gate-level simulations

驴说IC

本文源自微信公众号:陌上风骑驴看IC,不代表用户或本站观点,如有侵权,请联系nick.zong@aspencore.com 删除!

0

0