本文简单整理一下运放的CMRR定义、理解与应用,以及影响差分放大器CMRR的主要因素分析和解决。关于CMRR的好文档非常多了,所以本文不会很长,只是把我觉得比较便于理解CMRR概念的重要信息都串起来;文末会贴一些我看过的非常好的资料。

一、 CMRR的定义

CMRR的英文全称为common mode rejection ratio,中文翻译为共模抑制比。有些资料里也会出现CMR,共模增益的意思。

CMRR是一个基础但比较难掌握的直流参数。

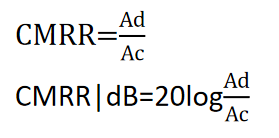

CMRR定义为差模增益Ad比上共模增益Ac,参见图1.1。为了归一化共模增益,或者说把输出折算到输入,才有了CMRR的定义。

图1.1 CMRR定义

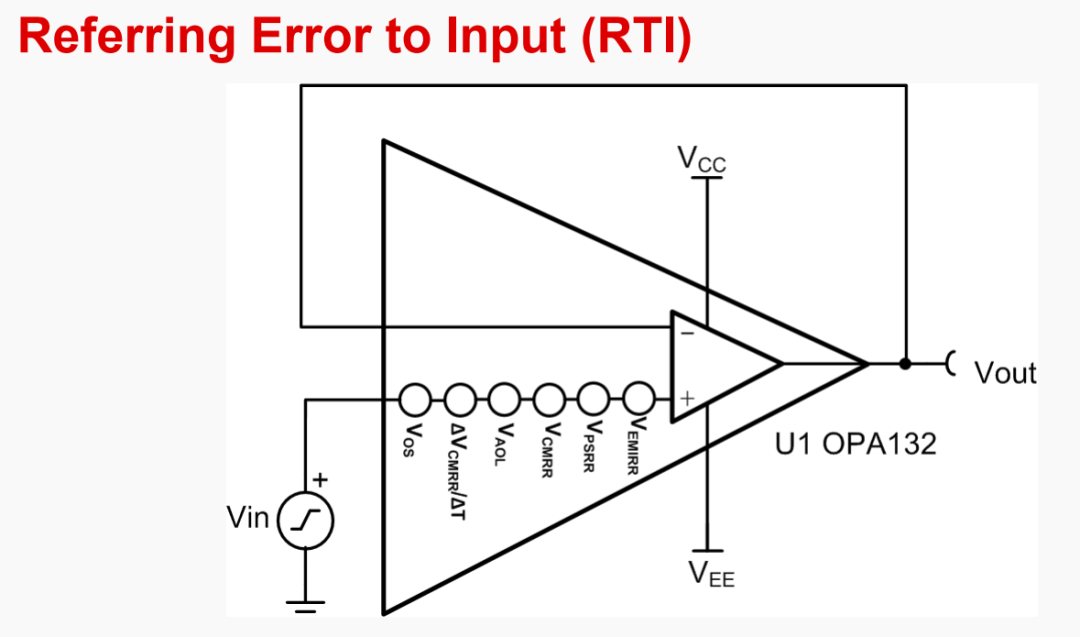

图1.2 CMRR一般折算到同相输入端

二、如何使用数据表中的CMRR参数

那我们怎么用这个参数呢?由于运放不是理想的,它的共模抑制比不是无穷大,所以会造成一些误差,但通常都很小,可忽略不计。

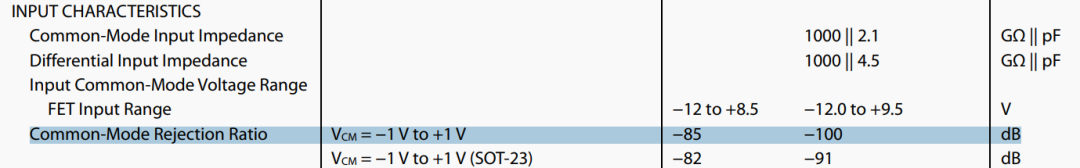

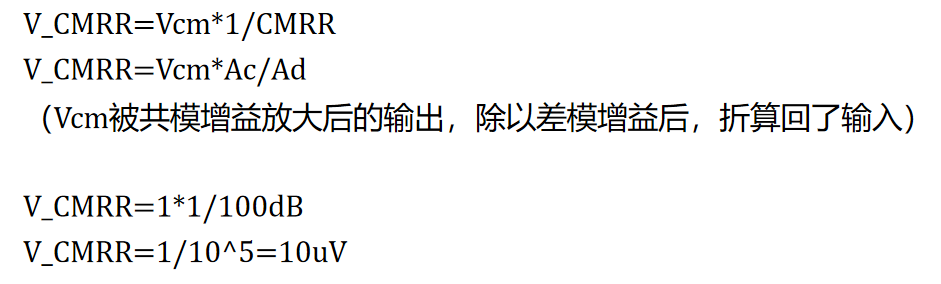

以AD8065举例,它的共模抑制比典型值为-100dB,参见图2.1。当Vcm等于1V时,由于CMRR的关系,同相输入端会有一个误差电压10uV,这里定义为V_CMRR,参见图2.2。

图2.1 AD8065的共模抑制比(Vcm=-1V~1V)

图2.2 当共模电压为1V时候,它会在输入端引入10uV的误差,进而被噪声增益放大

三、仿真验证AD8065的V_CMRR与计算值对比

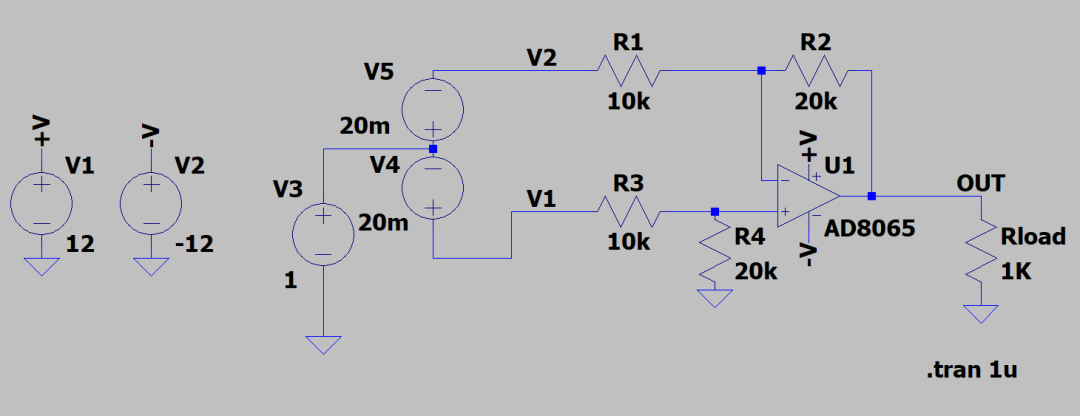

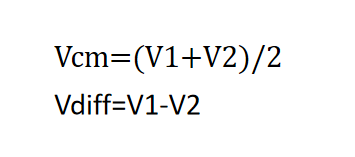

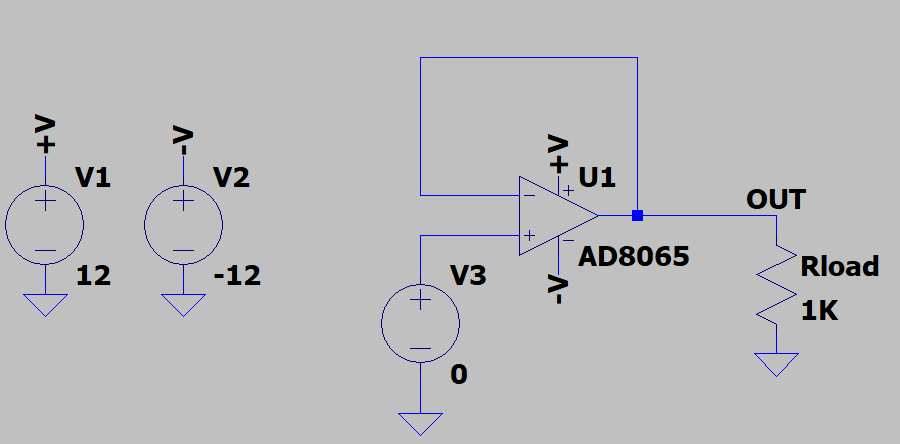

在仿真验证之前,先要解释两个概念,共模电压和差模电压,电路图参见图3.1,公式参见图3.2。

图3.1 理解共模电压与差模电压的电路图

图3.2 共模电压与差模电压公式

用于验证计算得到的V_CMRR的仿真电路参见图3.3。仿真方法很简单,先将V3置0得到一次输出Vo1(这是输入失调电压引起的误差),再将V3置1得到一次输出Vo2,那么,V_CMRR=Vo2-Vo1-1,结果参见表1。再次见到,运放自身的CMRR引起的误差是很小的,只有10uV——说明我们的计算方法没有问题。

图3.3 仿真V_CMRR的电路图

|

|

电压 |

说明 |

|

Vo1 |

0.000399996V |

Vos引起的误差,约0.4mV,跟数据手册是对得上的。 |

|

Vo2 |

1.00041V |

V3置1后的输出 |

|

V_CMRR |

约10uV |

跟前面用数据表的CMRR=100dB计算得到的结果是一致的,都是10uV! |

表1.1 仿真得到的V_CMRR,与计算值一致,仿真模型跟数据手册标称值是吻合的。

四、运放自身限制CMRR的因素

|

序号 |

运放自身限制CMRR的因素 |

说明 |

|

1 |

输入级电路失配 |

类似输入失调电压 |

|

2 |

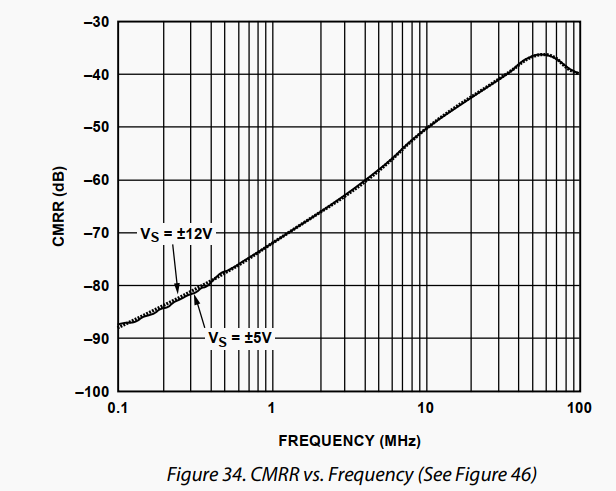

拖尾恒流源寄生电容随频率变化而变化 |

所以CMRR随频率变化,参见图4.1 |

表2 运放自身CMRR的因素

图4.1 AD8065的CMRR随频率增加而减小(注意它这里的CMRR是负值,我觉得是为了数据好看;dB单位可压缩数据、扩大视野,还能变乘除为加减)

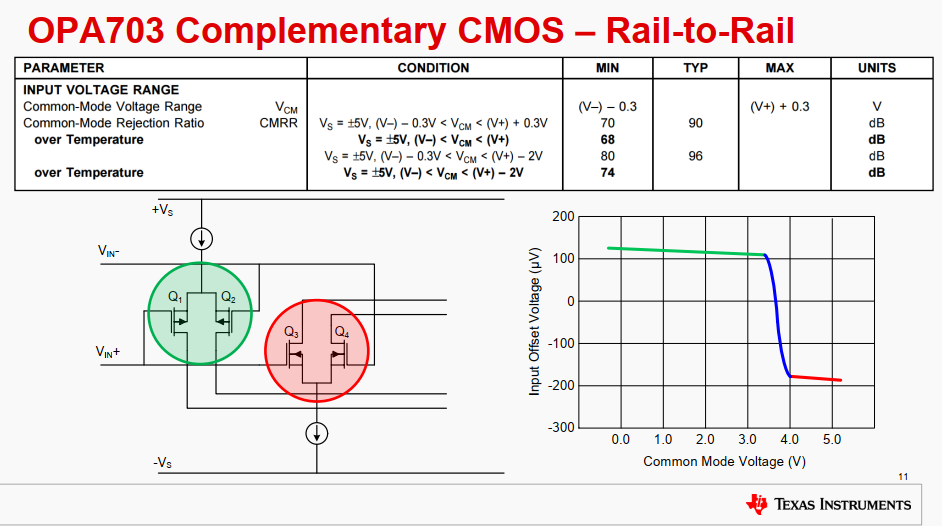

顺便提一下,有些轨到轨输入运放,根据Vcm会在两个输入对(PMOS和NMOS)之前切换,在不同输入对的Vos和Ibs是不一样的。从CMRR可判断这款器件是否存在交越失真,即图4.2中蓝色曲线部分。如果CMRR在全段Vcm范围内数值会变小,那么可以说明这颗运放会存在交越失真现象。

可以用反相拓扑解决这一问题,因为这样Vcm就固定了。

图4.2 CMOS型轨到轨输入运放从CMRR数据可判断是否存在交越失真

五、影响差分放大器CMRR的主要因素

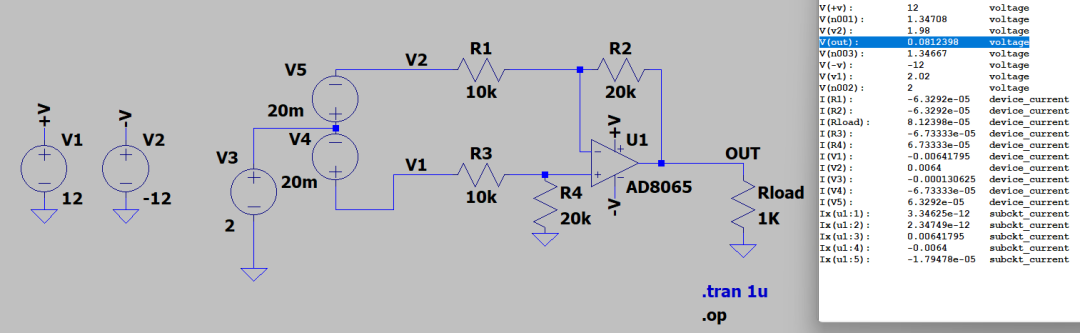

前面也简单计算过了,运放自身的CMRR非常高,由运放自身导致的V_CMRR,即CMRR引入的误差,是非常小,几乎可以忽略的。更常见的问题是电阻不匹配导致的CMRR严重恶化,主要是在图5.1这样的电路中。该电路差分增益为2倍(化简后为R2/R1),40mV信号放大2倍仿真约为81mV,增益误差约为1%,是可以接受的。

图5.1 采用理想电阻的仿真结果

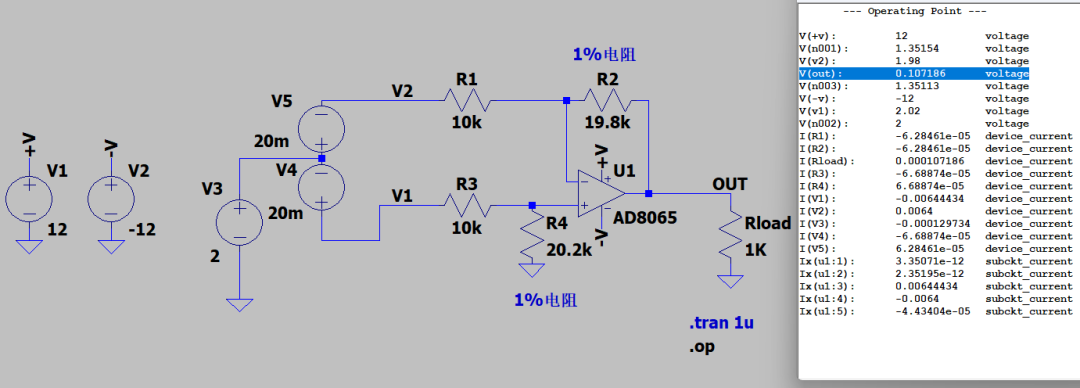

要是只有R2和R3、即最大阻值的电阻用1%电阻的话,那么同样的输入条件,仿真得到的输出约为107mV,增益误差高达33.75%!这是没办法接受的。直观的理解,就是共模电压V3被放大得太多了。

图5.2 只有R2/R3采用1%电阻的仿真结果

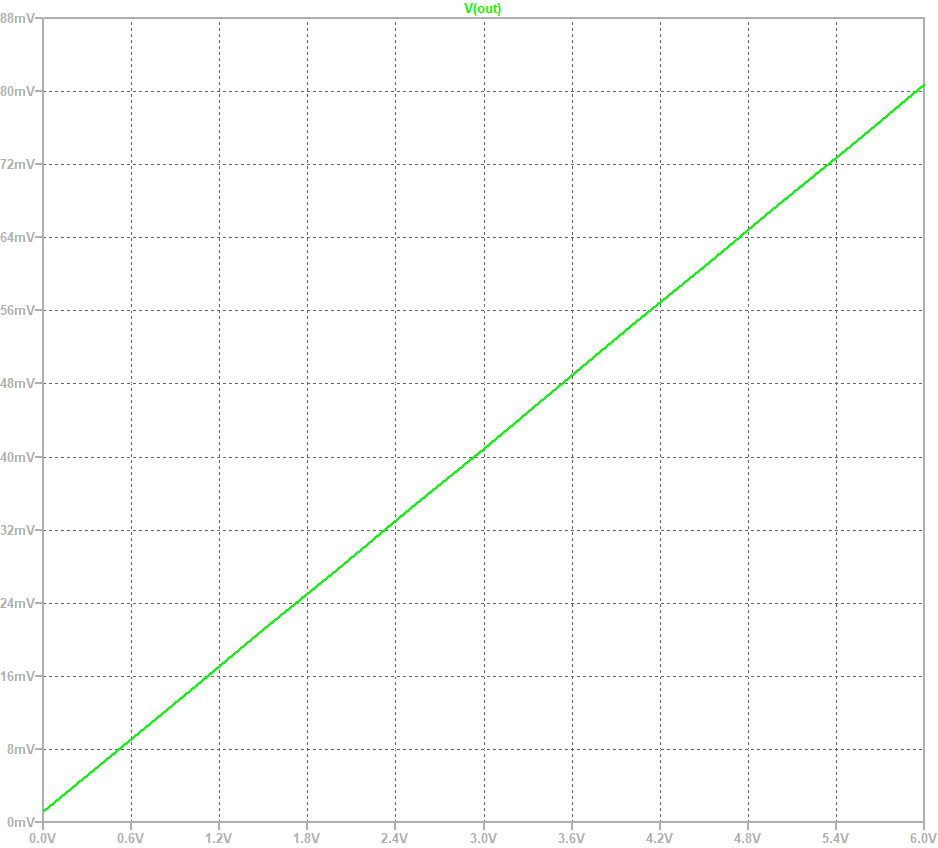

随着共模电压增大,误差也会越来越大,参见图5.3。

图5.3 随着共模电压增大,它所引起的误差也在变大(Vcm:0~6V,它引起的误差约:0~80mV)

我们先知道在图5.2电路中由于电阻匹配是导致CMRR主要因素就够了。如果非要用这种电路做差分放大,那么可以用如LT5400之类得器件,参见图5.4。或者直接选用仪表放大器(除了它的共模抑制比大以外,输入阻抗也更高,可忽略信号源内阻问题,因为图5.2电路中的输入阻抗有时也是个问题,如果信号源阻抗较大,也会造成误差)。

图5.4 LT5400四个匹配的电阻器(匹配度最高达到0.025%,在IC制造中,调节电阻的比率比调整电阻的绝对值要容易的多)

最后,如果共模电压Vcm非常小的情况下,使用图5.2电路配上普通1%电阻也是可以的,原因参见图5.3。

六、总结

本文整理了运放CMRR的定义,如何使用CMRR计算共模电压引入的误差(折算到同相输入端),并仿真进行了验证。运放自身限制CMRR的因素我们简单了解即可,因为运放自身CMRR通常很大,不是导致误差的主要因素。电阻匹配通常是差分放大器CMRR恶化的主要因素,本文这节讲的很粗略,更多请见参考资料。

七、参考资料

1、郑荟民写的《运算放大器参数解析与LTspice应用仿真》书里有关于电阻匹配引起误差的实际案例与详细推导,这本书写的非常好!

2、TI 的精密实验室运算放大器课程也讲了一些,CMRR部分不够详细;

3、TI的《信号链基础知识合辑(1-10)》有CMRR和CMR区别的内容,但有点小错误,比如CMRR公式错了;

4、TI的《TI信号链精品博文集锦——看一个TI老工程师如何驯服精密放大器》也有需要的更多内容。

0

0