通常情况下,我们会看到上拉电阻经常与MOS管一同出现,其实这对应的是一个处于开漏状态的GPIO口。开漏状态的GPIO口存在以下两种输出状态: 1. 当MOS管处于导通(打开)状态时,此时GPIO口输出的是低电平。2. 当MOS管处于截止(关闭)状态时,GPIO口的输出呈现浮空/高阻态,这时我们无法确定其输出电压的具体数值。

鉴于上述第二种情况,就需要在电路外部给这个GPIO口连接一个上拉电阻。当MOS管处于截止状态时,这个电阻能够将输出电压拉高到高电平状态,而这个起到拉高电压作用的电阻,就是我们所说的上拉电阻。 要是这个输出端所连接的后级输入部分已经集成了上拉电阻,那么从外部来看,就无需再额外添加一个上拉电阻了。就像在上图中,我们能看到一个带有上拉电阻的开关。实际上,这个开关在原理上与MOS管是相似的。设想一下,如果没有内部集成的这颗上拉电阻,一旦开关断开,这一端就会处于浮空状态,其电压值无法确定。

要是这个输出端所连接的后级输入部分已经集成了上拉电阻,那么从外部来看,就无需再额外添加一个上拉电阻了。就像在上图中,我们能看到一个带有上拉电阻的开关。实际上,这个开关在原理上与MOS管是相似的。设想一下,如果没有内部集成的这颗上拉电阻,一旦开关断开,这一端就会处于浮空状态,其电压值无法确定。

所以上拉电阻的作用是为了解决输出浮空状态时电压不确定而出现的,辅助浮空状态输出高电平。

通常情况下右边等效输入阻抗都非常大,所以当左边这个MOS管关闭时,基本不会有电流流过电阻,所以A点电压还是接近于3.3V。

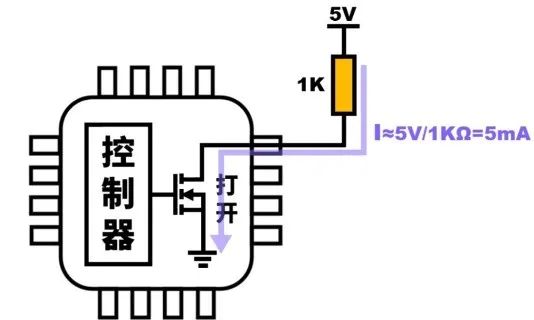

当MOS管导通时,电路中会形成一个通路,此时就会产生漏电流。以下图1K的上拉电阻为例,漏电流可达到5mA。这部分电流不仅白白浪费,还会在电路中产生热量,对电路的稳定性和性能产生不利影响。从这一角度来看,为了减少漏电流及其带来的负面影响,上拉电阻的阻值越大越好。

当MOS管导通时,电路中会形成一个通路,此时就会产生漏电流。以下图1K的上拉电阻为例,漏电流可达到5mA。这部分电流不仅白白浪费,还会在电路中产生热量,对电路的稳定性和性能产生不利影响。从这一角度来看,为了减少漏电流及其带来的负面影响,上拉电阻的阻值越大越好。但如果上拉电阻的阻值过大,虽然漏电流会相应减小,但驱动能力也会随之变弱。而驱动能力不足,又会导致电路无法正常工作,影响信号的有效传输。所以,在选择上拉电阻阻值时,需要在漏电流和驱动能力之间找到一个平衡点。

在电路中,存在着一个对地的寄生电容,这对电路的驱动能力有着重要影响。当电路中的信号从低电平向高电平转换时,从示波器上看,呈现出的是方波的上升沿。但要是把时间刻度放大,就会发现低电平到高电平的转换并非瞬间完成,而是有一个逐步爬升的过程。

在电路中,存在着一个对地的寄生电容,这对电路的驱动能力有着重要影响。当电路中的信号从低电平向高电平转换时,从示波器上看,呈现出的是方波的上升沿。但要是把时间刻度放大,就会发现低电平到高电平的转换并非瞬间完成,而是有一个逐步爬升的过程。这一爬升过程,本质上是通过电阻给寄生电容充电的过程。上拉电阻的阻值大小,与充电速度紧密相关。电阻越大,充电就越慢,爬升过程也就越迟缓。这极有可能导致像PWM或者IIC这类对波形要求较高的信号出现失真现象。因为PWM和IIC通信需要信号能够快速切换,所以为了保证信号的准确性和快速性,上拉电阻的阻值应尽量控制在10K以内 。

1

1