DDR1~DDR5的区别及管脚定义详解

核桃设计分享

176浏览

0评论

0点赞

2025-06-12

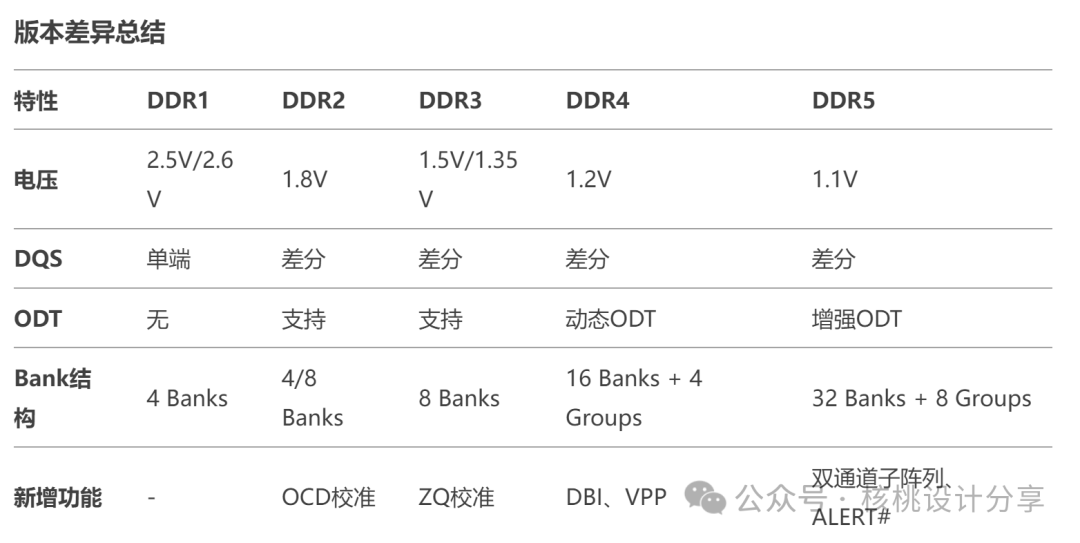

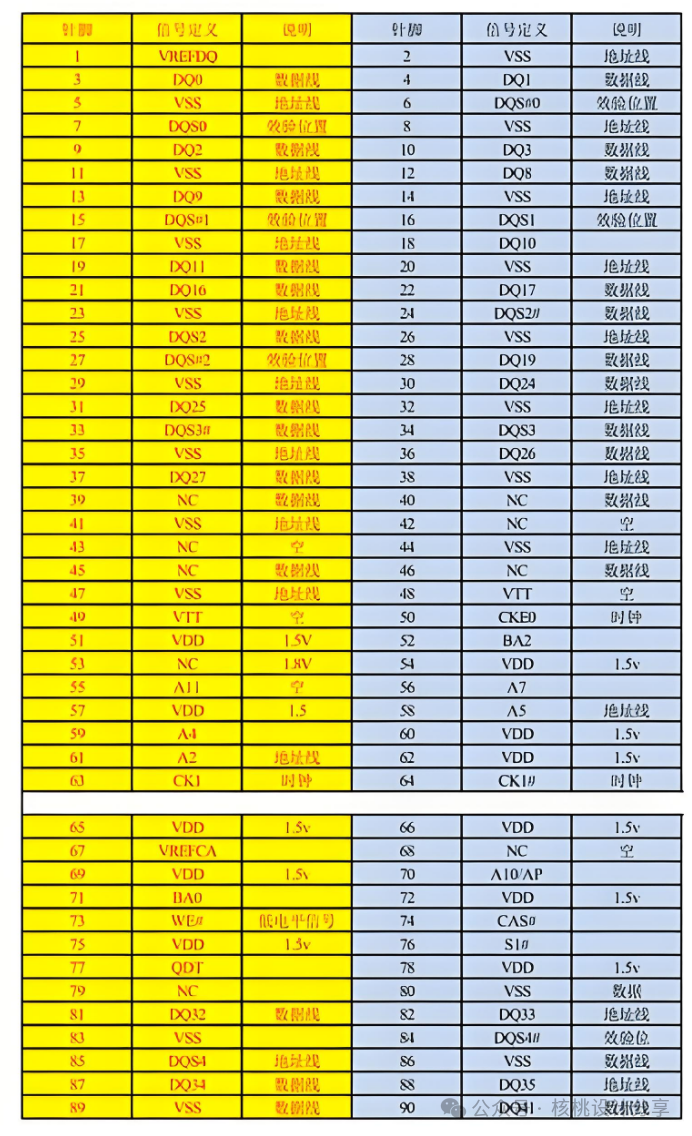

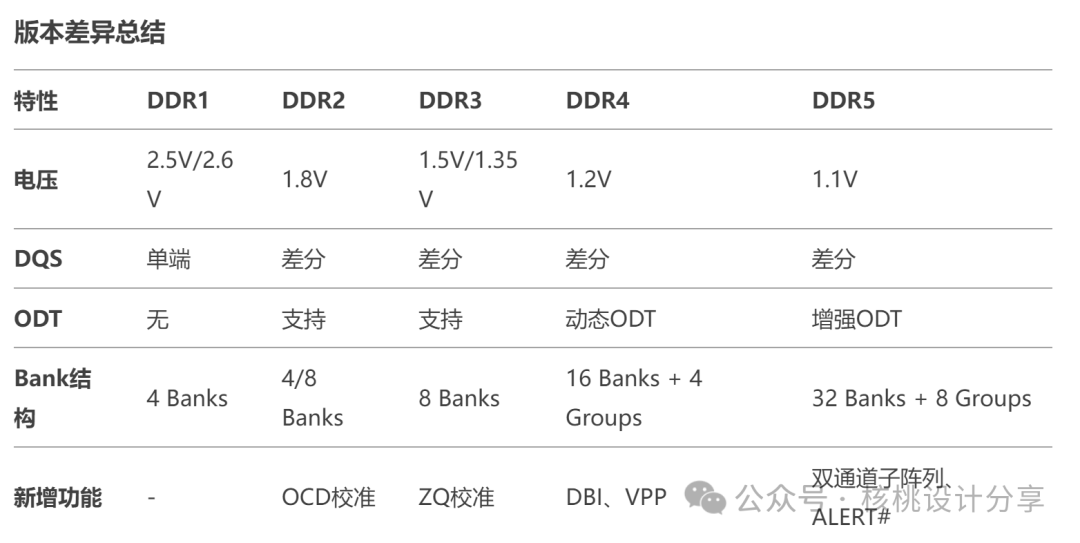

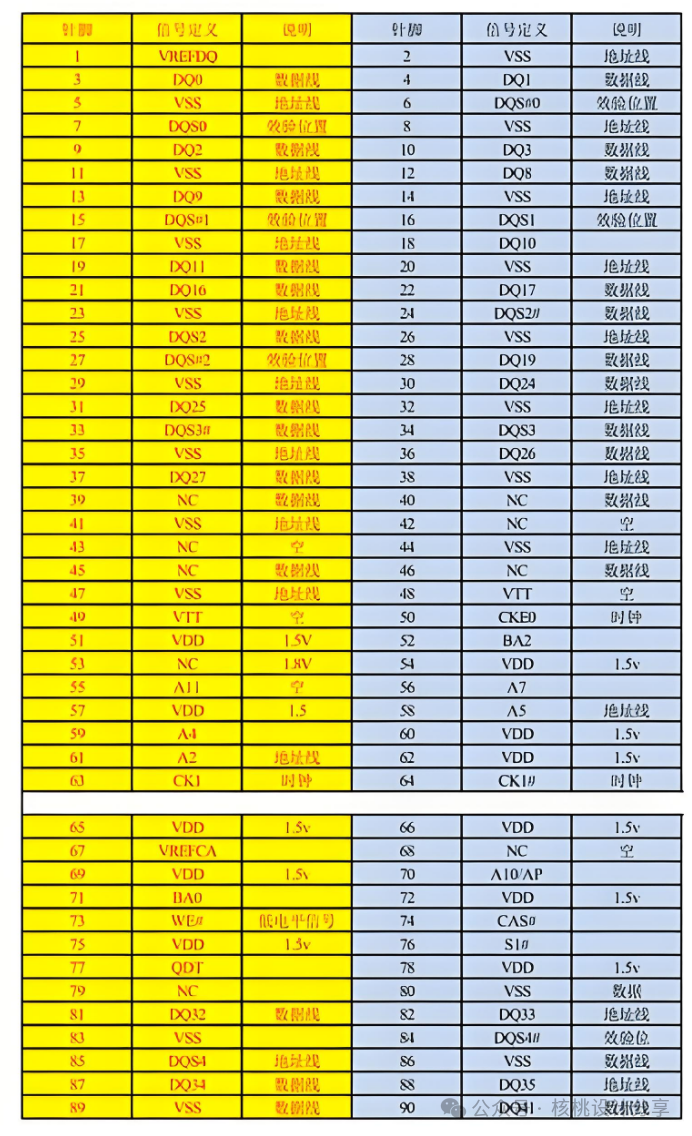

目前DDR最新的版本是DDR5,对于之前的版本DD1~DDR4区别上不大,核心的功能管脚基本保持一致。我们先了解一下DDR1~DDR5的一些主要的区别,如下表所示: 从上表可以看得出来,DDR1~DDR5最大的区别在于工作电压,越来越低了,说明功耗越做越低了。DDR的管脚定义在大体上来看可以分为6组。(1)电源管脚和GND管脚主要分为VDD和VDDQ已经对应的地管脚VSS和VSSQ。VDD:核心电压,对应的负极是VSS(参考电位)VDDQ:I/O电压,对应的负极是VSSQ(参考电位)(2)数据相关信号线DQ[0:N]:数据传输线,全部为双向数据线,负责读写数据。DQS/DQS#:差分数据选通信号(同样是双向),主要用于同步数据采样。DM/DBI:数据掩码(DDR1~DDR3),或者数据总线反转(DDR4)其中:DM:写入数据时能屏蔽无效的数据。 DBI:在DDR4中主要用于优化整体功耗和信号的完整性。(3)地址线与Bank选择线A[0:N]:地址总线(包括行地址和列地址),其中DDR1是14位地址(A0~A13),DDR4为17位地址(A0~A16)。BA[0:M]:Bank地址,用于选择存储体。其中DDR1一共有4个Bank,DDR4有高达16个Bank,4个Bank Group。BG[0:K]:Bank Group地址。(4)控制信号CS#:片选信号,选择需要操作的芯片。RAS#/CAS#/WE#:行列地址选通与写使能控制。ODT:片上终端使能,动态调整终端电阻,可以起到改善信号完整性的作用。CKE:时钟使能管脚,用于控制时钟信号(如低功耗模式时)RESET#:硬件复位信号,低电平有效。(5)时钟信号CK/CK#:差分系统时钟,上升/下降沿均触发数据操作。CK_t/CK_c:增强差分时钟命名。(6)其他VREF:参考电压,用于数据接收端的电平判定。ZQ:外部校准管脚,调整驱动强度与终端电阻。一般连接240Ω电阻到VSSQ,电阻建议用高精度的。TEN/ALERT#:温度传感器与错误报警输出管脚(仅在DDR5上有)。

从上表可以看得出来,DDR1~DDR5最大的区别在于工作电压,越来越低了,说明功耗越做越低了。DDR的管脚定义在大体上来看可以分为6组。(1)电源管脚和GND管脚主要分为VDD和VDDQ已经对应的地管脚VSS和VSSQ。VDD:核心电压,对应的负极是VSS(参考电位)VDDQ:I/O电压,对应的负极是VSSQ(参考电位)(2)数据相关信号线DQ[0:N]:数据传输线,全部为双向数据线,负责读写数据。DQS/DQS#:差分数据选通信号(同样是双向),主要用于同步数据采样。DM/DBI:数据掩码(DDR1~DDR3),或者数据总线反转(DDR4)其中:DM:写入数据时能屏蔽无效的数据。 DBI:在DDR4中主要用于优化整体功耗和信号的完整性。(3)地址线与Bank选择线A[0:N]:地址总线(包括行地址和列地址),其中DDR1是14位地址(A0~A13),DDR4为17位地址(A0~A16)。BA[0:M]:Bank地址,用于选择存储体。其中DDR1一共有4个Bank,DDR4有高达16个Bank,4个Bank Group。BG[0:K]:Bank Group地址。(4)控制信号CS#:片选信号,选择需要操作的芯片。RAS#/CAS#/WE#:行列地址选通与写使能控制。ODT:片上终端使能,动态调整终端电阻,可以起到改善信号完整性的作用。CKE:时钟使能管脚,用于控制时钟信号(如低功耗模式时)RESET#:硬件复位信号,低电平有效。(5)时钟信号CK/CK#:差分系统时钟,上升/下降沿均触发数据操作。CK_t/CK_c:增强差分时钟命名。(6)其他VREF:参考电压,用于数据接收端的电平判定。ZQ:外部校准管脚,调整驱动强度与终端电阻。一般连接240Ω电阻到VSSQ,电阻建议用高精度的。TEN/ALERT#:温度传感器与错误报警输出管脚(仅在DDR5上有)。

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

15年以上测试经验资深专家实操、案例演示、经验分享。吸波材料、绝缘材料、天线、微波和射频元器件材料等介电常数精确测量。参会赢丰厚礼品:Encok蓝牙耳机、HD3乐高、飞利浦电动牙刷、几何计数无绳跳绳、芒米雨伞、IPAD平板包、10周年冰箱贴等

-

压力变送器作为测量仪器,是工业中最常用的传感器之一。上篇文章中,小编对压力变送器的种类有所阐述。为增进大家对压力变送器的认识,本文将对绝对压力变送器、绝对压力变送器的原理以及选型予以介绍。如果你对压...

-

继电器,虽是老生常谈的话题,但是却耐人寻味。本文中,小编将对继电器、继电器的主要作用予以阐述。此外,小编还将介绍高频继电器的工作原理、高频继电器的特点和高频继电器的结构。如果你对继电器具有兴趣,不妨...

-

CMOS在电路中具有重要作用,大家对于CMOS通常较为耳熟。但是,大家对于CMOS却未必十分了解。为增进大家对CMOS的认识,本文将对CMOS相关知识予以详细介绍。如果你对本文内容具有兴趣,不妨继续往下阅读哦。 CMOS(Co...

-

-

-

mos管栅极电阻的作用mos管栅极简介在了解mos管栅极电阻的作用之前,我们先了解一下mos管栅极及其他2个极

-

介绍了多层PCB设计的基本概念,包括为何需要多层设计、其优势(如信号质量提升、成本效益和空间利用)以及如何判断

-

怎么提高buck电路的工作效率?我们知道在buck电路设计中一个十分需要关注的点就是效率,效率的高低决定了你的PCBA是否可以当“暖手宝”,一摸就烫手。

-

-

片式多层瓷介电容器(MLCC)除有电容器“隔直通交”的通性特点外,还有体积小、比容大、寿命长、可靠性高和适合表

-

-

从上表可以看得出来,DDR1~DDR5最大的区别在于工作电压,越来越低了,说明功耗越做越低了。DDR的管脚定义在大体上来看可以分为6组。(1)电源管脚和GND管脚主要分为VDD和VDDQ已经对应的地管脚VSS和VSSQ。VDD:核心电压,对应的负极是VSS(参考电位)VDDQ:I/O电压,对应的负极是VSSQ(参考电位)(2)数据相关信号线DQ[0:N]:数据传输线,全部为双向数据线,负责读写数据。DQS/DQS#:差分数据选通信号(同样是双向),主要用于同步数据采样。DM/DBI:数据掩码(DDR1~DDR3),或者数据总线反转(DDR4)其中:DM:写入数据时能屏蔽无效的数据。 DBI:在DDR4中主要用于优化整体功耗和信号的完整性。(3)地址线与Bank选择线A[0:N]:地址总线(包括行地址和列地址),其中DDR1是14位地址(A0~A13),DDR4为17位地址(A0~A16)。BA[0:M]:Bank地址,用于选择存储体。其中DDR1一共有4个Bank,DDR4有高达16个Bank,4个Bank Group。BG[0:K]:Bank Group地址。(4)控制信号CS#:片选信号,选择需要操作的芯片。RAS#/CAS#/WE#:行列地址选通与写使能控制。ODT:片上终端使能,动态调整终端电阻,可以起到改善信号完整性的作用。CKE:时钟使能管脚,用于控制时钟信号(如低功耗模式时)RESET#:硬件复位信号,低电平有效。(5)时钟信号CK/CK#:差分系统时钟,上升/下降沿均触发数据操作。CK_t/CK_c:增强差分时钟命名。(6)其他VREF:参考电压,用于数据接收端的电平判定。ZQ:外部校准管脚,调整驱动强度与终端电阻。一般连接240Ω电阻到VSSQ,电阻建议用高精度的。TEN/ALERT#:温度传感器与错误报警输出管脚(仅在DDR5上有)。

从上表可以看得出来,DDR1~DDR5最大的区别在于工作电压,越来越低了,说明功耗越做越低了。DDR的管脚定义在大体上来看可以分为6组。(1)电源管脚和GND管脚主要分为VDD和VDDQ已经对应的地管脚VSS和VSSQ。VDD:核心电压,对应的负极是VSS(参考电位)VDDQ:I/O电压,对应的负极是VSSQ(参考电位)(2)数据相关信号线DQ[0:N]:数据传输线,全部为双向数据线,负责读写数据。DQS/DQS#:差分数据选通信号(同样是双向),主要用于同步数据采样。DM/DBI:数据掩码(DDR1~DDR3),或者数据总线反转(DDR4)其中:DM:写入数据时能屏蔽无效的数据。 DBI:在DDR4中主要用于优化整体功耗和信号的完整性。(3)地址线与Bank选择线A[0:N]:地址总线(包括行地址和列地址),其中DDR1是14位地址(A0~A13),DDR4为17位地址(A0~A16)。BA[0:M]:Bank地址,用于选择存储体。其中DDR1一共有4个Bank,DDR4有高达16个Bank,4个Bank Group。BG[0:K]:Bank Group地址。(4)控制信号CS#:片选信号,选择需要操作的芯片。RAS#/CAS#/WE#:行列地址选通与写使能控制。ODT:片上终端使能,动态调整终端电阻,可以起到改善信号完整性的作用。CKE:时钟使能管脚,用于控制时钟信号(如低功耗模式时)RESET#:硬件复位信号,低电平有效。(5)时钟信号CK/CK#:差分系统时钟,上升/下降沿均触发数据操作。CK_t/CK_c:增强差分时钟命名。(6)其他VREF:参考电压,用于数据接收端的电平判定。ZQ:外部校准管脚,调整驱动强度与终端电阻。一般连接240Ω电阻到VSSQ,电阻建议用高精度的。TEN/ALERT#:温度传感器与错误报警输出管脚(仅在DDR5上有)。

0

0