应某友人要求,写一篇总结数字电路实现流程各个步骤的输入输出文件都有哪些。本文所有输入输出都基于Cadence 数字实现工具,其他厂家对应工具需要的输入文件也都大同小异,驴只补充所知道的一些小异,未补充的不代表没有,只代表驴不知。通常在项目起始就需要跟各家vendor 搜集输入数据,故每一步将所涉及到的tech file 单独列出,因为所涉及文件种类巨多,难免遗漏错误,恳请广大驴友补充更正。

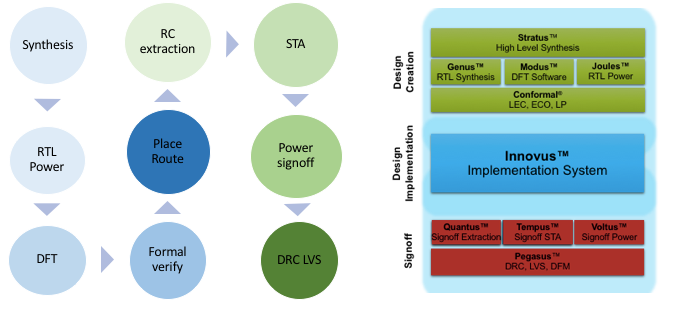

驴按照自己的理解,将数字电路实现流程划分成九大块:

-

综合,synthesis

-

RTL 功耗分析, RTL Power

-

可测性设计,DFT

-

形式验证,Formal Verify

-

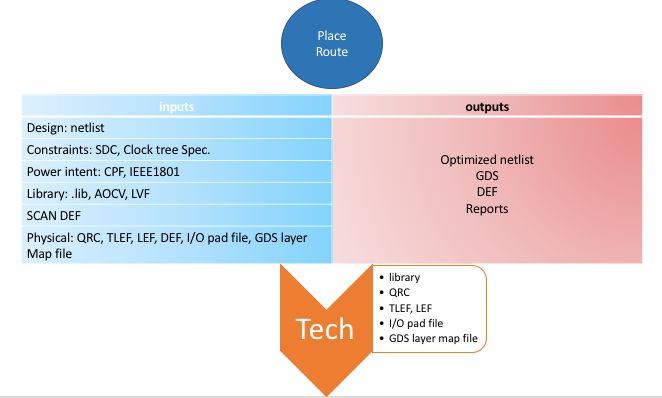

布局布线,Place Route

-

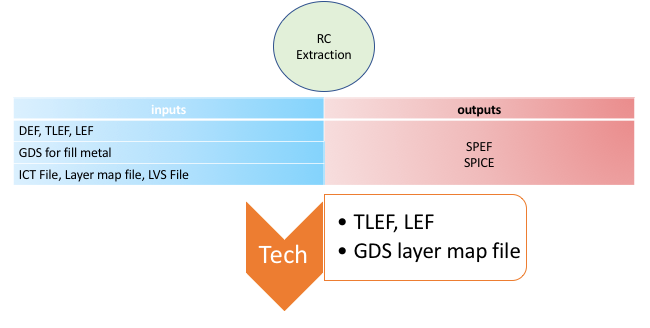

寄生参数抽取,RC extraction

-

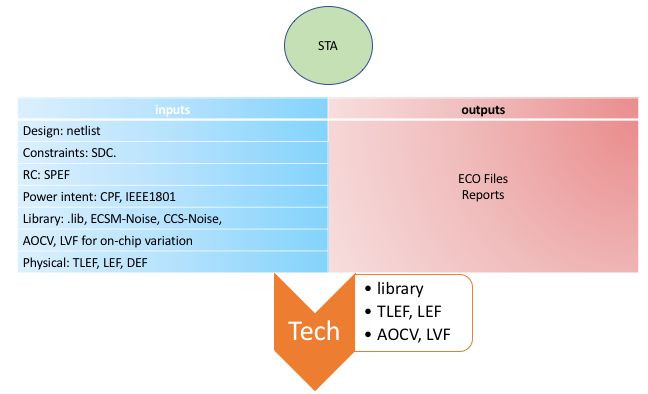

静态时序分析,STA

-

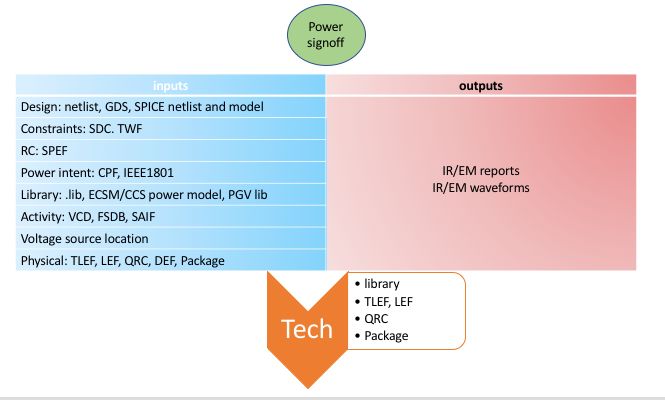

IR, EM 分析,Power Signoff

-

DRC, LVS

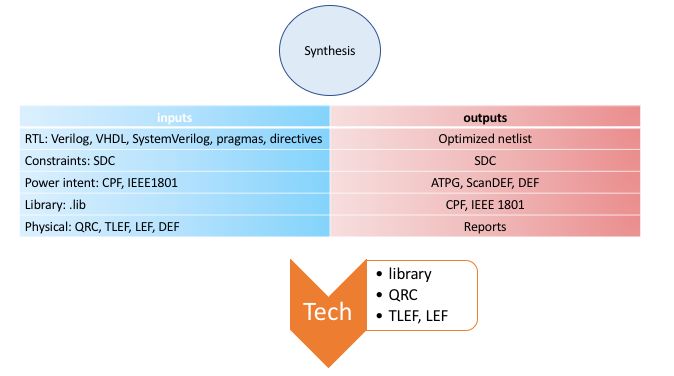

综合:

补充,S 家工具做物理综合时,不吃QRC, 需要读入tluplus 跟 layer map file.

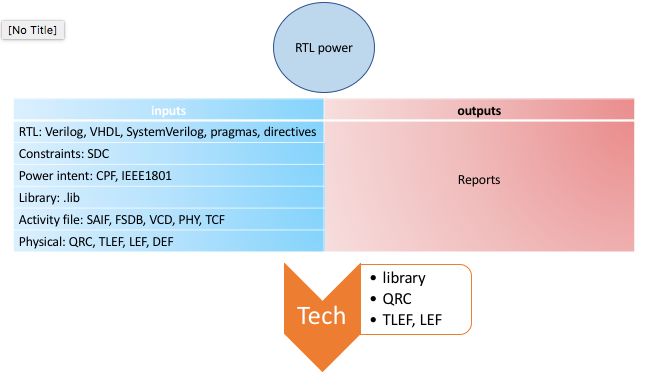

RTL 功耗分析:

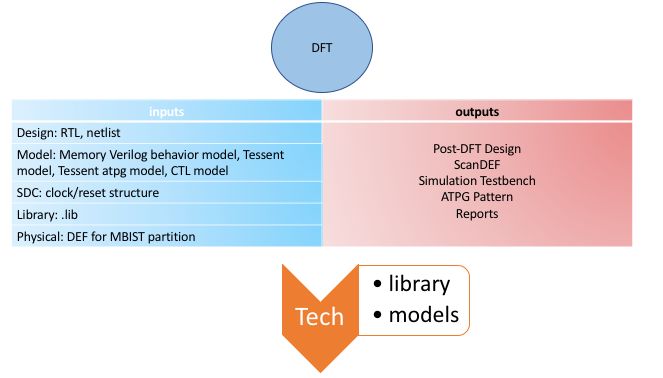

可测性设计 DFT:

形式验证跟低功耗检查:

布局布线:

补充,S 家工具,不吃QRC, 需要读入tluplus 跟 layer map file.

寄生参数抽取:

补充,S 家工具,需要nxtgrd tech file.

静态时序分析:

IR, EM 分析:

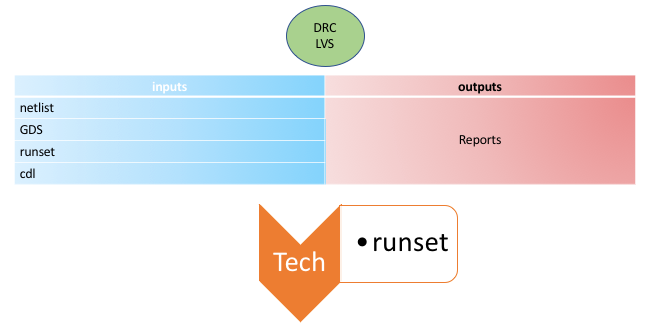

DRC, LVS:

驴说IC

本文源自微信公众号:陌上风骑驴看IC,不代表用户或本站观点,如有侵权,请联系nick.zong@aspencore.com 删除!

0

0