数字实现硅农大方向可分为前端后端或中端后端,再细分可分为综合、DFT、形式验证、PR, PV, PI, STA 等,细分之后各工种缝扣子的缝扣子,挂衣领的挂衣领,相互有了差别,但是不论哪一个工种,都会涉及到一个词叫DRC: Design Rule Check.

数字电路实现中的DRC 只知道以下三类:

- Timing 相关的DRC: transition, capcitance, fanout.

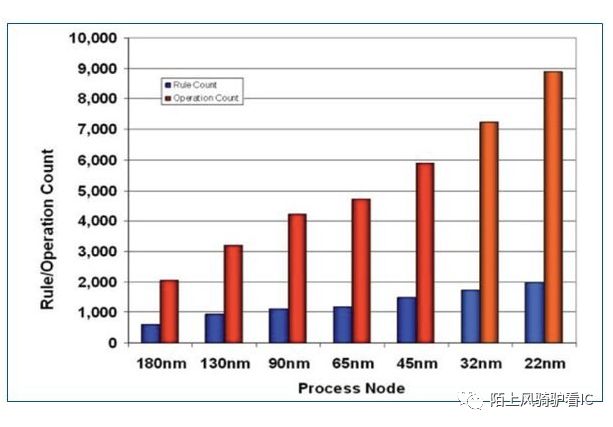

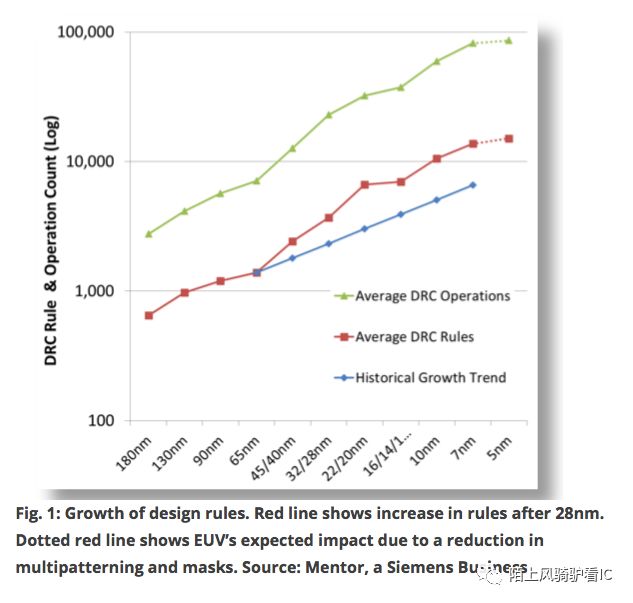

- Physical 相关的DRC, 无数多条。

- DFT 相关的DRC.

Timing 相关的DRC

Max/min Transition time: 用于约束信号翻转时上升或下降过程所允许的最大或最小时间,在数字电路实现过程中,该值可以从library 中读出,或用命令set_max_transition, set_min_transition 进行设置。如果两个值同时存在,工具在优化或检查时以最紧的为标杆。

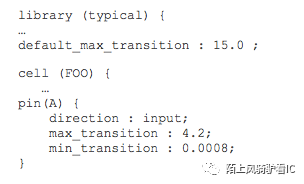

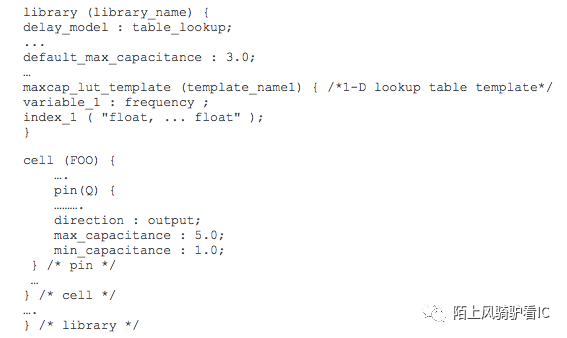

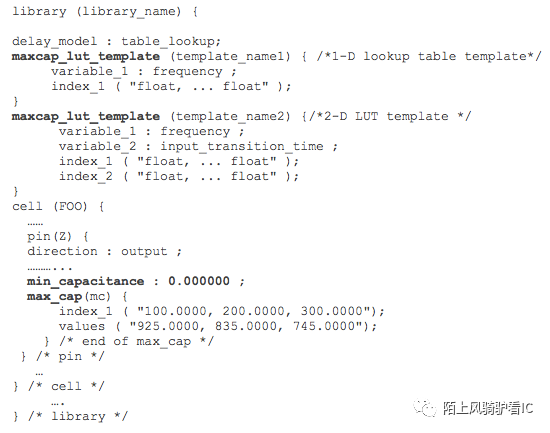

如下例所示,在library 中通常会有default_max_transition 的定义,在pin 上会有max_transition 跟min_transition 的定义,先进工艺的lib 中max_transition 跟min_transition 可能是一张一维或二维的表格。

Physical 相关的DRC

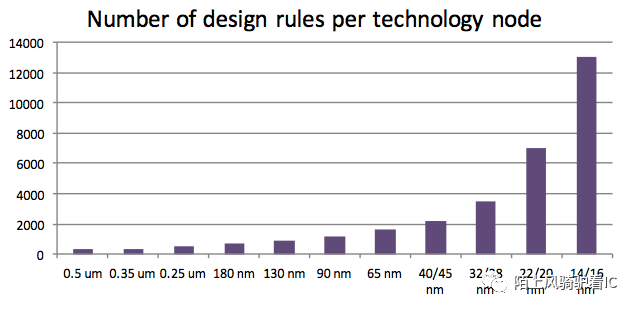

Placement 跟Routing 都分别有许多rule, Placement 的rule 规定了谁跟谁可以放在一起,谁跟谁不能放在一起,谁跟谁放在一起要距离多远才不会摩擦除火花或者相互撕咬;Routing 的rule 规定了金属走线跟过孔的宽度、厚度、高度及线之间的距离。大致有如下类型:

- Minimum width and spacing for metal

- Minimum width and spacing for via

- Fat wire Via keep out Enclosure

- End of Line spacing

- Minimum area

- Over Max stack level

- Wide metal jog

- Misaligned Via wire

- Different net spacing

- Special notch spacing

- Shorts violation

- Different net Via cut spacing

- Less than min edge length

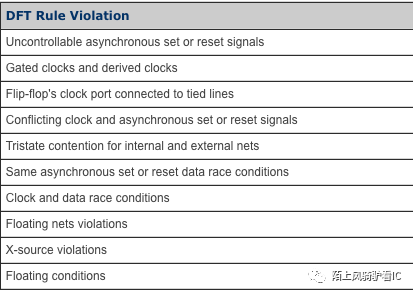

随着工艺的进步设计的复杂应用场景的特殊需求多元化,DFT 越来越复杂,rule 也越来越多,通常最常涉及的DFT DRC 包含如下部分:

本文源自微信公众号:陌上风骑驴看IC,不代表用户或本站观点,如有侵权,请联系nick.zong@aspencore.com 删除!

0

0