74 HC573系列是一个高速硅通道CMOS设备而且是一个低功率引脚互换性的肖特基TLL(LSTTL)闭锁器。

74HC573系列基本描述:

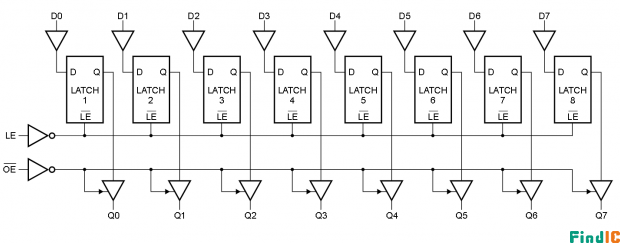

74HC573系列具有八进制D型透明锁存器,每个锁存器有单独的D型输入和3态真输出,用于总线导向应用。闩锁使能(LE)输入和输出使能(OE)输入对所有闩锁都是公用的当LE高时,Dn输入的数据进入锁存。在这种情况下闩锁是透明的,即闩锁输出将在其相应的D输入改变时改变状态。当输入电压低时,闩锁存储在输入电压高到低转换之前的设置时间内的信息。当OE低时,8个锁存器的内容可在输出。当OE高时,输出进入高阻抗关断状态。OE输入的操作不会影响锁存器的状态74HC573系列功能相同

74HC573系列主要特征:

•输入和输出在包的相反两边允许与微处理器容易接口

•适用于微处理器和微型计算机的输入或输出端口,

•面向总线应用的三态非反相输出

•共三态输出使能输入

•与74HC563: 74HCT563和74HC373: 74HCT373功能相同,

•符合JEDEC标准No.7A

•ESD保护:

HBM EIA/JESD22-A114-C超过2000 v

MM EIAJESD22-A115-A超过200V

•在-40℃至+85℃/-40℃至+125℃范围内

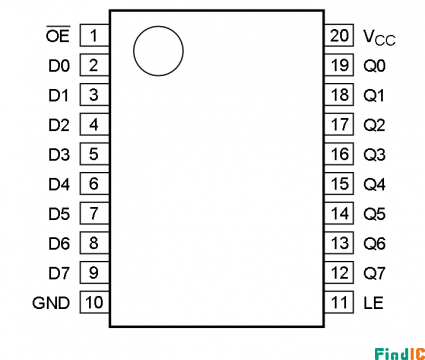

74HC573D引脚图及功能:

脚OE-,1:状态输出使能输入(低电平有效)

脚D0, 2:数据输入0

脚D1、3:数据输入1

脚D2、4:数据输入2

脚D3、5:数据输入3

脚D4、6:数据输入4

脚D5、7:数据输入5

脚D6, 8:数据输入6

脚D7、9:数据输入7

脚GND, 10:接地(0 V)

脚LE, 11:锁存器使能输入(有效高电平)

脚Q7,12:3-state门锁输出7

脚Q6,13: 3态锁存器输出6

脚Q5,14: 3态锁存器输出5

脚Q4,15: 3态锁存器输出4

脚Q3,16: 3态锁存器输出3

脚Q2,17: 3态锁存器输出2

脚Q1,18: 3态锁存器输出1

脚Q0,19: 3态锁存器输出0

脚VCC, 20:电源电压

74HC573系列真值表:

74HC573系列逻辑图及原理图:

74HC573系列应用电路图:

如上图,在P3口同时接了两个74HC573锁存器,两个芯片的输出使能端OE都接地,数据锁存使能端LE分别接P2^6和P2^7,锁存器的输出数据端Qn都接LED条形显示器,本例通过对P3口赋不同的值来使U4的上四个LED灯点亮,U5的下四个LED灯点亮。

74HC573D核心参数:

制造商: NXP

产品种类: 闭锁器

电路数量: 8 Circuit

逻辑类型: D-Type Latch

极性: Non-Inverting

静态电流: 8 μA

输出线路数量: 8 Line

高电平输出电流: -7.8mA

传播延迟时间: 15ns

电源电压-最大: 6V

电源电压-最小: 2V

最小工作温度: -40°C

最大工作温度: +125°C

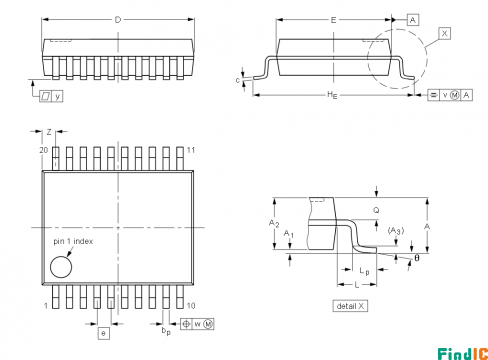

封装: SO-20

高度: 2.45 mm

长度: 13 mm

输出类型: 3-State

类型: D-Type

宽度: 7.6 mm

通道数量: 8 Channels

输入线路数量: 10 Line

电源电流—最大值: 8μA

工作电源电压: 2 V to 6 V

单位重量: 266.700 mg

74HC573系列封装参数:

0

0