在设计之初往往有相当大的问题,尤其是在、Layout、等部份都需要注意,本文将从这些面向加以探讨。

印刷电路基板的噪讯对策

几乎所有的电路都使用印刷电路基板,这意味着印刷电路基板的噪讯对策俨然成为噪讯对策的核心。

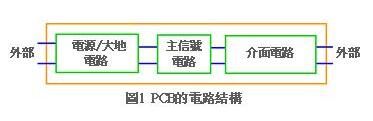

如图1所示,印刷电路基板内的电路可以分成三大类:

*电源/大地电路

*主信号电路()

*接口电路

主信号电路是执行实际电路动作的部位,主信号电路随着电路的种类与用途,还能够再细分成数个单元。接口电路是执行印刷电路基板与外部信号交易(接口)的电路,接口电路以噪讯对策立场而言,它具备防止印刷电路基板外部的噪讯渗入电路基板,以及电路基板内部的噪讯放射至基板外部两种功能。

电源/大地(ground)电路主要功能是提供电源给信号电路与接口电路,大地具备不平衡电路的折返线功能。原本电源与大地必需维持稳定的电位,不过实际上电源与大地会各自产生共通(impedance),因此在噪讯对策上属于非常棘手部位。

印刷电路基板的Layout

以噪讯对策观点而言,必需根据种类与用途将电路加以分类,才能够将噪讯对策配置(Layout)在印刷电路基板上。原则上高噪讯加害性电路与低抗噪讯电路,最好能够分别配置在独立的电路基板上,不过实际上基于成本与电路规模等考虑,两电路混载情况相当普遍。

如上所述高噪讯加害性电路与低抗噪讯电路,两者必需尽量分开配置,尤其是噪讯很大的信号线,尽量避免长距离回绕布线。加害性很高的布线则尽量避免通过低抗噪讯电路周围,如果采取平行或是密接布线时,crosstalk会有变大之虞。 布线的回绕方式取决于组件的配置,为达成上述布线原则,组件的配置成为重要的课题。

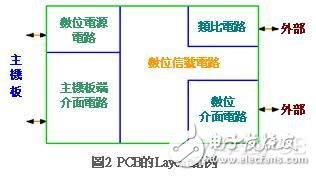

图2是典型的印刷电路基板Layout范例,如图所示该电路基板是复数个电路基板之中的一片,此时只要透过主机板就能够进行信号交易。主机板执行基板之间的数据交易时通常会有Bus通行,虽然图2的基板主体是数字电路,不过却混载小规模的模拟电路。

数字电路透过主机板端的接口电路,除了与其它基板进行接口(inrface)之外,数字接口还能够与外部进行其它接口作业。 模拟电路能够与外部进行模拟信号交易,模拟电路单元设有A/D转换器,为了避免模拟电路对数字接口发生噪讯干扰,因此设置A/D转换器时必需远离数字接口。

模拟电路的电源必需与数字电路的电源完全分开独立设置,不过模拟电路的电源电压若与数字电路的电源电压相同时,模拟电路的噪讯很低的情况除外,模拟电路可以使用部份的数字电路电源,此时必需在模拟电源的入口处设置,杜绝数字电路的噪讯。

至于大地则是将数字与模拟单元连接成一点,再利用数字与模拟连接部位的图案(pattern)不规则回绕设计使它具备若干的阻抗,再利用该阻抗能够使数字与模拟单元产生分离效果。

印刷电路基板的布线

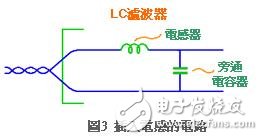

基板的入口处通常会设置旁通(bypass condenser)。以图2为例,旁通器设置在电路端。基板入口处的旁通电容器,除了发挥旁通电容器原本的功能之外,它还可以抑制基板内的电源阻抗,过滤来自基板外部的噪讯。为强化上述目的,某些电路还会插入与旁通电容器形成LC滤波器(图3)。

一旦使直流重迭时,由于直流成份的影响造成电感值大幅降低。此外电源用电感会有很大的直流动,因此必需选择适合的电感器。一般电源基板入口处设置的电感器,大多使用图4的Toroidal型电感器。

旁通电容器采用两段式结构,为了使旁通电容器支持应宽广的频域,因此必需分别使用可以支持低频的电容器与支持高频的电容器。基板入口处设置的电容器属于低频用,虽然它的容量取决于基板内部流动的电流值,不过一般都使用数十μF左右的铝质电电容器。

高频用旁通电容器则设置在IC附近,大多使用数0.01μF左右的陶瓷电容器。理想上每个IC附近最好插入一个旁通电容器,小电流IC每隔2~3个设置一个即可。第二段旁通电容器同样设置在IC附近,如果距离IC太远的话,由于受到图中的电感器影响,容易造旁通电容器效果被削弱等问题。

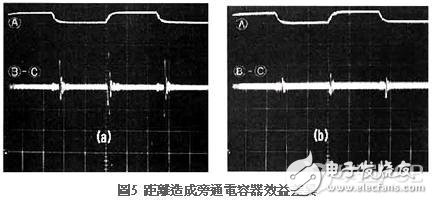

图5是距离与旁通电容器的互动特性测试结果,图5(a)的旁通电容器与IC的距离为10cm,图5(b)为3cm,两者其它条件完全相同,不过(a)与(b)的效果却截然不同,距离为10cm时旁通电容器几乎未发挥任何作用。

本实验使用数字IC(Inverter),图中的Ⓐ为IC的动作波形,如图所示随着动作波形的变化,IC的电源电流也发生改变。Ⓑ-Ⓒ为电源-大地之间的波形,如图所示Ⓐ变化时,电源内部会产生严重的噪讯。

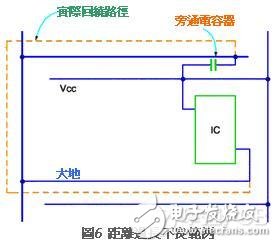

图6的旁通电容器外观上看似非常靠近IC,实际却是典型的设计不当范例。旁通电容器的效果,基本上取决于电源-大地-图案三者之间的回绕方式,虽然旁通电容器的效果非常大,不过布线的阻抗也非常重要,因此设计上通常会使用非常粗大的图案(图7)。

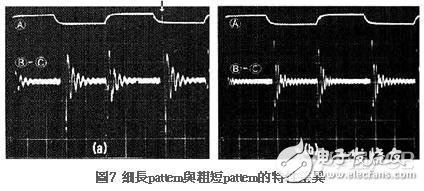

此处为探讨图案的影响,IC附近刻意不插入旁通电容器,只在基板入口处设置的旁通电容器,其结果如图7所示。图7(a)从旁通电容器一直到IC为止的图案比较细长(高阻抗),图7(b)的图案则比较粗短(低阻抗),不过两者的波形都呈状。

振动的原因主要是连结(Linking)所造成,以图7(a)为例,由于连结周期与布线长度呈比例,因此图7(a)的连结周期非常长,而且振幅也比较大。图7(a)的Linking最初呈站立状,Ⓐ的波形凸出延伸(亦即图7(a)的上方箭头处与下方③的部位),实际上①部位的波形也呈相同形状。

连结波形之中②部位对照Ⓐ波形的站立,虽然①与③对照呈下降状,不过①、②、③三者的连结振幅彼此相异,主要原因是受到IC的”H”/”L”非对称性特性影响所致,一般IC的”L”电流驱动能力强大者居多,因此此处IC也出现相同现象。

一般低频模拟电路只须一点接地(earth)即可,高频时则需采用Beta earth方式,此时包含大地(ground)在内所有有关电源的布线,也必需采用Beta earth设计方式,至于数字电路空白部位,若以Beta图案填补非常有效。

多层基板的电源与大地(ground)大多采用Beta图案设计方式,主要理由是Beta图案的阻抗比线状图案低,而且Beta图案还兼具遮蔽(shield)信号导线层的功能,这意味着多层基板在噪讯对策上非常有效。 设计信号导线首要工作是缩短信号导线的长度,因此布线前组件的配置技巧具有决定性影响。

基板内的布线大多是不平衡状态,此时电路上必需考虑包含信号线在内的信号折返线(亦即大地线)。信号线与大地线构成的电路,必需避免变成大面积回路(loop)。此外基于crosstalk等考虑,设计上必需尽量避免低抗噪讯信号线与高加害性信号线邻接、平行配置,无法回避时可以在两信号线之间插入大地线(ground wire)。

高阻抗部位的抗噪讯能力不如低阻抗部位,因此高阻抗部位的布线必需采取最短距离设计,或是加长低阻抗部位的布线长度,必要时可以插入缓冲器(buffer)。

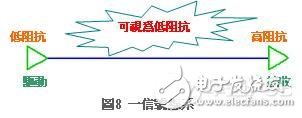

长距离布线时信号线的阻抗会变成信号线的阻抗特性,布线很短时布线两端的其中一端会受到低阻抗支配,因此可以将布线整体视为低阻抗。信号线的一端为驱动端,另一端为接收端的设计相当普遍,驱动端的输出阻抗很低,接收端的输出阻抗却很高,信号线很短的场合,驱动端的阻抗可以视为低阻抗。

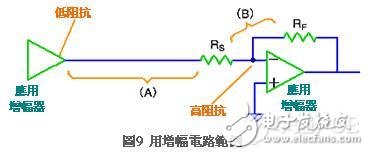

如图9所示驱动与接收端之间插入高阻抗组件时,高阻抗组件与接收端之间的布线会变成高阻抗,此时必需缩减高阻抗部份的布线长度,加长低阻抗部份的布线长度。图9中的接收器为反相增幅器,由于应用增幅器的输入阻抗很高,因此与RF之间的(B)属于高阻抗,换言之此时必需缩减该部位的布线长度,加长(A)部位的布线长度

设计基板布线时必需注意反射造成的连接(linking),尤其是驱动与接收端挟持的信号线,刚好符合产生连接的条件。以往基板不太会发生连接问题,主要原因是在一般尺寸的基板内部,连接的频率大多比信号的频率高(长20cm的图案,频率大约是250MHz)。

此外IC选择取决于信号的频率,低动作频率的IC无法使大于本身频率的信号通过,换言之IC本身具备滤波器效应,即使有高频连接通常都不会造成困扰。不过最近几年信号的频率不断更新记录,基板内部信号与连接的频率非常接近,导致连接问题越来越严重。

高频噪讯(noise)不但会在信号线内部传递,还会透过信号线放射散播,因此单纯在接收端设置滤波器,过滤连接的效果非常有限,根本对策是彻底消弭连接(图10)。信号频率很高时,延缓信号的站立方法容易造成信号本身迟钝,另外一种方法是使接收端适当终结藉此消除连接,不过终结接收端时电流仍旧在流动它会消费电力,基于省能源等考虑一般都是采取驱动端终端设计方式。

如果接收端插入滤波器,在接收端可以消除连接,不过却无法消除信号在线的连接。如图10(b)所示驱动端插入滤波器可以取代终端器。信号在线的滤波器通常都是使用图11所示的Ferrite beads type。

中空圆筒状Ferrite beads磁性材料,利用通过中心的导线形成电感器(Induct)。理想性电感器完全没有损失,只有纯粹的电感值,实际电感器则有损失。损失越低表示电感器的质量越高,电感器的质量指针为「Q」,Q值越大损失越低,零损失时Q值为无限大。

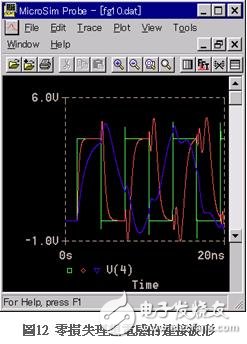

不过噪讯滤波器要求适当的损失,尤其是连接防止用电感器的损失如果太低时几乎没有任何效果。图12是两端的反射100%布线,使用零损失理想电感器时的模拟分析连接波形(因为模拟分析可以创造零损失时各种状态)。

由图可知随着电感值的大小,连接的波形与频率也跟着改变,不过连接却不会衰减,连接会随着信号在布线中复数次的往返不断产生,电感值则限制该往返信号的频率。

纯电感值不会消费信号的能量,因此连接不但不会衰减反而会不断产生,此处为了消弭连接,因此要求一定的能量损失,亦即滤波器必需具备适当的损失。Ferrite beads的损失并非单纯的阻抗,它的损失大小具备频率特性,因此透过适当的Ferrite beads特性选择(频率特性、电感值、损失的大小),不但可以使信号的波形迟钝,还能够有效抑制连接。

图13是实际使用Ferrite beads时的波形,值得一提的是Ferrite beads并非连接至基板内的图案,而是直接与接口连接。如图所示13(a)是无Ferrite beads时的波形;图(b)~(d)分别是逐渐增加Ferrite beads电感值时的波形。

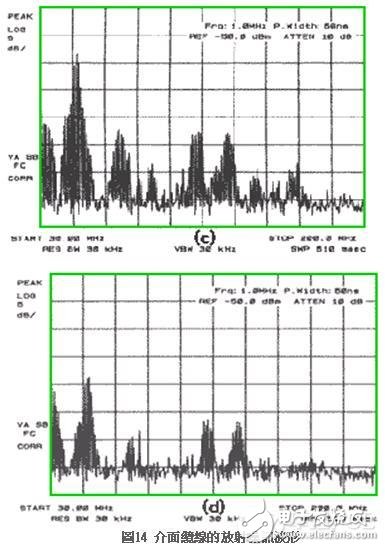

图13(b)仍旧残留若干连接;图13(d)出现瘫陷(sag),图中水平部位应该呈平整状,实际上却是急遽下降之后略为提高,至于瘫陷则是电感值过大造成的特殊现象。图13(c)被认为最适宜的Ferrite beads。数字信号的场合,图13(d)比较妥适,不过即使是图13(d)的波形也不会引发误动作。若与图13(c)比较,信号的高频成份反而大幅减少,其结果如图14所示,来自信号信的放射噪讯亦随着降低。

0

0