要说硬件设计改善最令人头疼的莫过于EMC问题的整改了,很不巧最近就遇到了好几个,日常加班整改 。

。

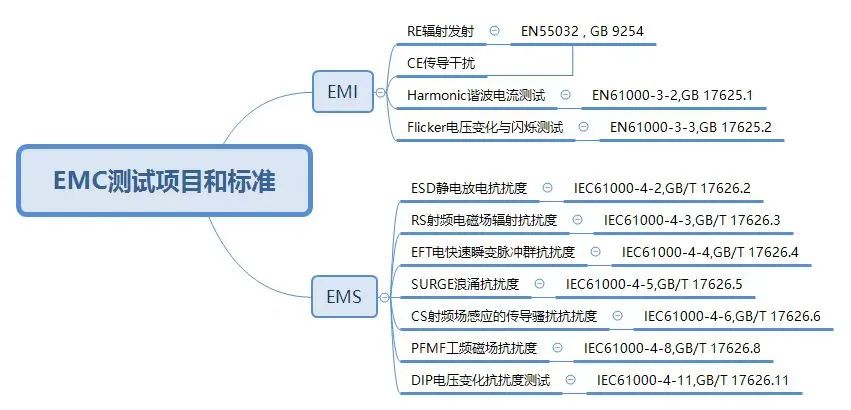

EMC认证测试是好大的一块内容,并且产品要想在市场上合格的流通,那EMC认证也是必须要做的一项。

其中ESD问题是经常会出现的一类问题,前面也有写过ESD静电的内容,可跳转《如何进行静电测试?(电子硬件)》,当ESD问题出现的时候,就需要硬件去进行整改,整改的过程常常都是心酸与泪。

因为ESD问题是一种看不见摸不着的东西,所以不好进行模拟,更多是通过理论与经验与进行试错与分析验证。

如果碰上了ESD问题,可以通过以下思路去进行改善。

最直接的方式就是通过物理隔离的方法将ESD阻挡在产品的外部,从实际场景中将两者剥离,让ESD进来都困难,从而有效的改善ESD问题。

实际应用时可以使用金属外壳将PCB的地与产品外壳地隔开,不过这也是看具体场景的,如果设备外壳本身就没有良好的接大地,那可能改善效果就不大。

也可以使用高阻值的磁珠,进行串联隔离,从而防止ESD进入到产品内部。

-

ESD静电管

另外就是使用专门的ESD静电管了,利用ESD静电二极管的特性充分保护电路。

在将ESD静电二极管并联到电路的时候,如果电路正常工作,ESD静电二极管就处于截止状态(高阻态),不会影响电路的正常工作,但是当电路异常比如说ESD导致异常过压等情况时,它就会立即从高阻态转变为低阻态,这样瞬间电流就有一个低阻态的导通路径,从而把异常的过压限制在一个安全的范围内,保护被保护的电路以及相关元件不损坏。

当异常过压消失的时候,ESD静电二极管又恢复到高阻态状态,电路正常工作。

在相关的ESD干扰路径上加上静电管,从而避免ESD从一些位置耦合到芯片中,造成芯片的损坏。

-

改变ESD的电流回路路径

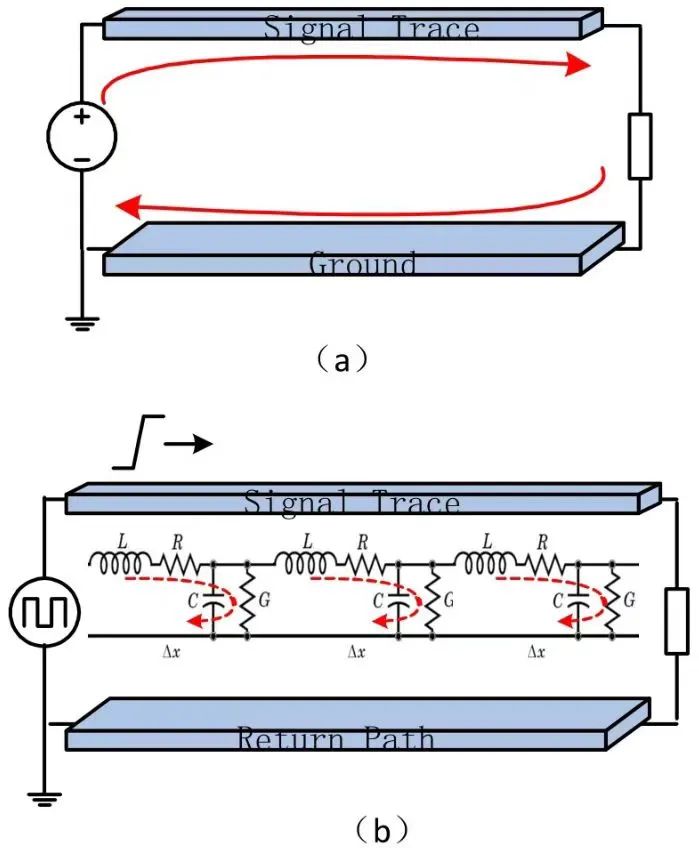

改变ESD的电流回路路径,使得回路面积减少,具体的方法实现上比如可以采用完整的地铺铜或者增加一定数量的过孔来使得地阻抗的一致性,从而使得静电电流自动选择阻抗最低的路径返回到源端。

-

加屏蔽罩

拆开手机电路板,可以看到上面有很多元件芯片都有加一个屏蔽罩。

它可以有效的保护元器件,并且会减少干扰,对于ESD的改善也是有帮助的,可以通过拉远距离的方式使得PCB板中的敏感元件远离ESD放电电流路径,从而改善ESD问题,同时它也是一种非常很常见的方式。

-

电源和信号线的布局布线优化

这个就是从PCB设计上动手,在电源布局上进行改善与优化,比如说DCDC电源布局合理,反馈走线尽量短,电感远离敏感IC或器件等,信号线上的高频旁路电容采用就近接地的方式,从而减少进入整个电路板系统的ESD大电流。

同时对于复位信号,也需要根据实际情况进行相应的布局优化,防止走线长度过长的问题以及可以使用电阻或者电容来增加某条电路的整体阻抗,以防干扰信号过大。

0

0