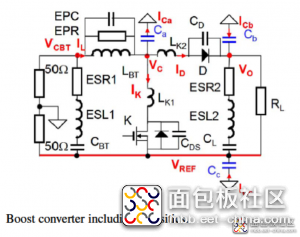

考虑寄生参数的Boost变换器共模噪声路径以及关键点波形如下所示:

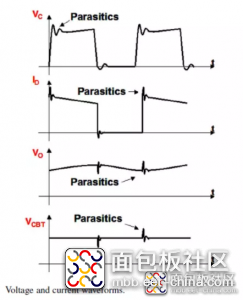

如果将图中某些支路替换为上图右侧的电流源或电压源,那么boost EMI模型如下图所示:

上图可见,变换器的EMI噪声主要来自C点的dv/dt(电压跳变最大,所以影响最大),以及E点和D点的dv/dt,然后通过其与地端的寄生电容流经LISN。

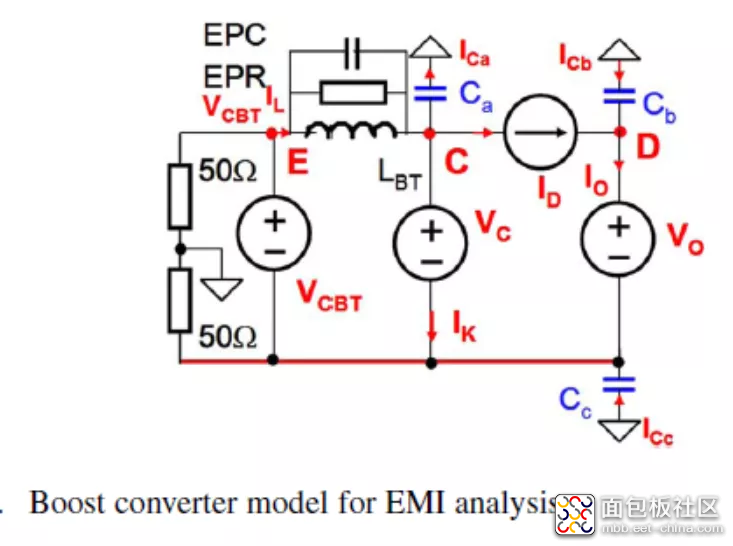

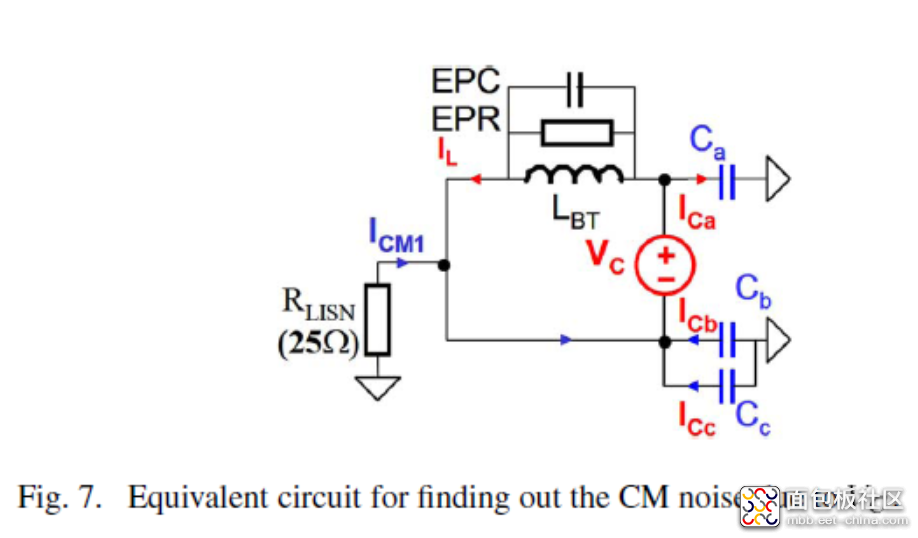

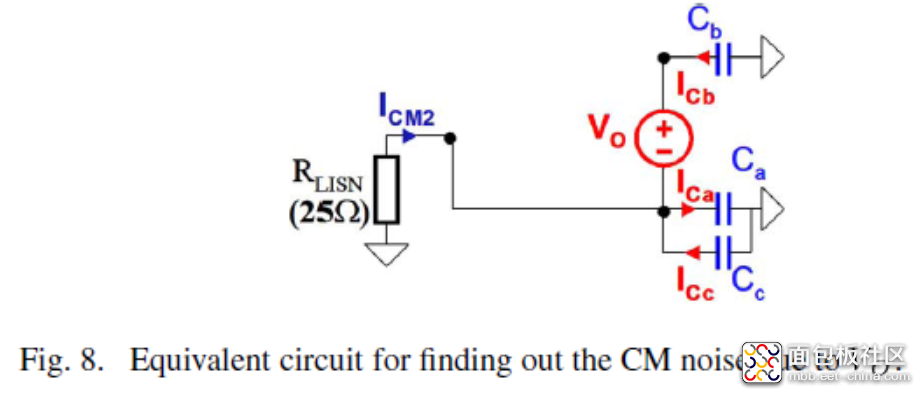

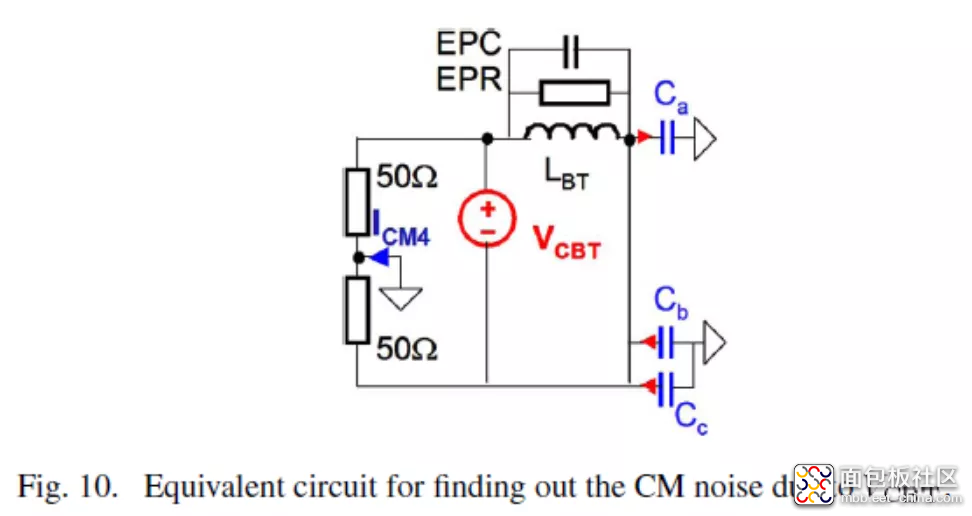

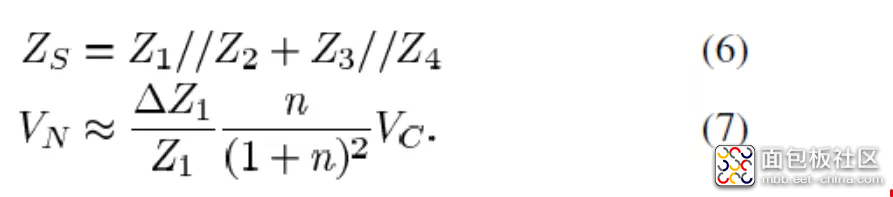

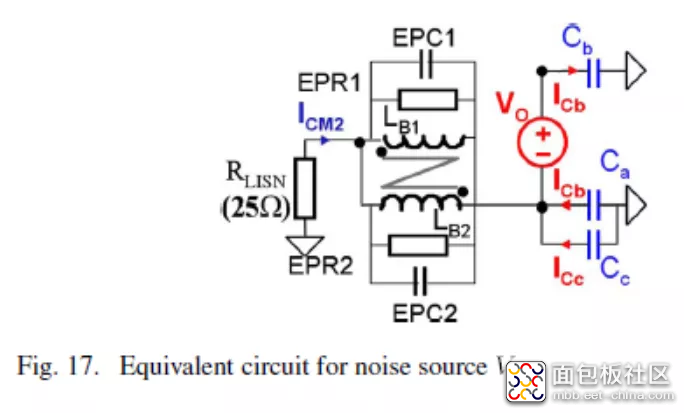

考虑Vc、Vo、Vcbt影响时的共模噪声路径分别如下所示:

值得注意的是,在考虑Vcbt的影响中,其等效电路中的三个寄生电容都是并联在LISE的一端,所以LISN的两条支路是不平衡的,所以就会使得一部分共模噪声产生差模噪声。

如何减小Vc产生的共模噪声?

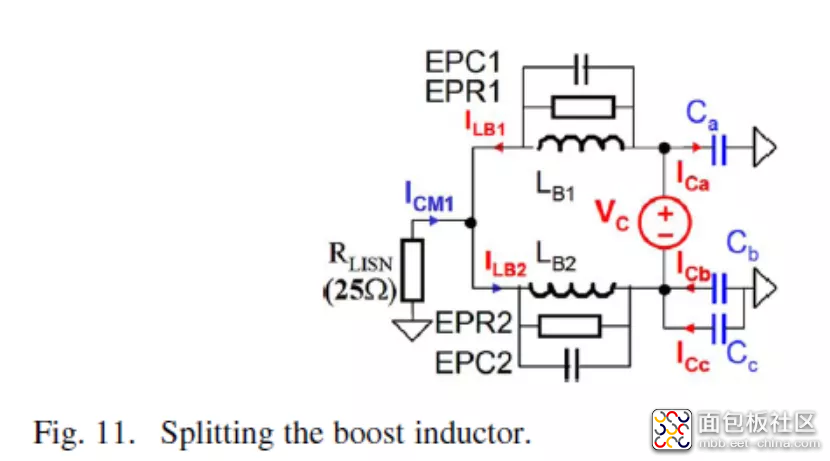

为了减小Vc对共模噪声的影响,文章采用噪声平衡的策略,将电感分为两个电感如下图所示:

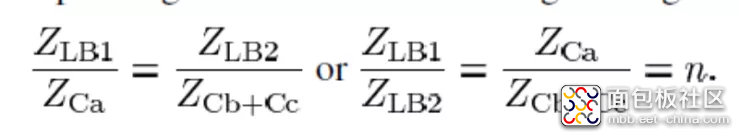

根据惠斯通电桥原理,只要保证下式成立,就能够使得Vc产生的共模噪声抵消:

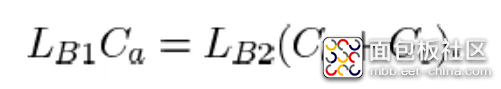

式中ZLB1和ZLB2为两个电感的阻抗。在低频段,电感的寄生电容和寄生电阻的效应并不明显,所以上式又可简化为如下所示:

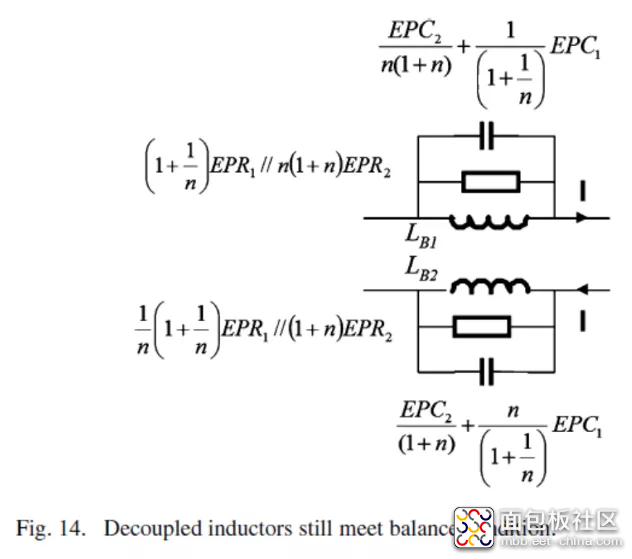

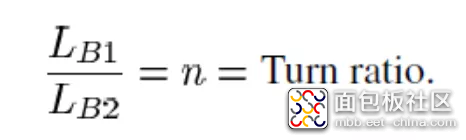

但是在高频下就要考虑电感的寄生参数的影响,为了实现电桥平衡就需要保证高频段电感寄生参数也要满足电桥平衡条件。因此就要用到耦合电感(如果是全耦合,可以认为LB1/LB2=ZB1/ZB2),耦合电感的解耦模型如下所示:

首先考虑耦合电感是全耦合的情况,如果LB1/LB2=n,那么ZLB1/ZLB2=n。可以证明,如果电感的匝比为n,那么两个电感的比值也为n。

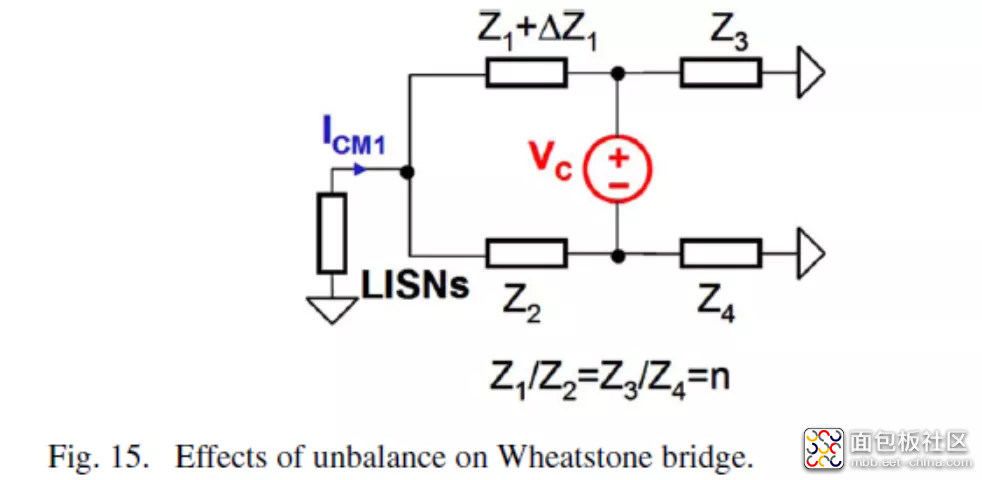

但是一般情况下耦合电感并非全耦合,非全耦合情况下的惠斯通电桥如下所示,假设z1,z2,z3,z4仍是平衡的,当其中一个阻抗变化Δz1,来计算其对共模噪声的影响大不大。

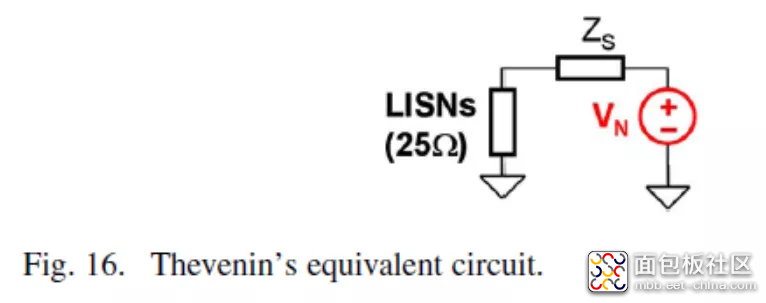

根据戴维南等效原理,可将上图等效如下:

其中

从上式看出,阻抗的不平衡度可以表示为Δz/z,且等效的共模噪声源是与阻抗的不平衡度成正比的。所以对于Vc产生的共模噪声,考虑不平衡的影响,n越大,不平衡对共模噪声产生的不利影响越小。

如何减小Vo产生的共模噪声?

经过将一个电感改为耦合电感之后,输出电压的共模噪声路径如下图所示,因为反向耦合电感的并联阻抗依然为0,所以对输出电压的共模噪声耦合路径基本没有影响。减小Vo对共模噪声的影响可以通过以下路径,1. 尽量减小输出电容的ESL和ESR;2. 尽量使Cb尽量小,

如何减小Vcbt对共模噪声的影响?

使用共模电感之后,共模噪声路径如下图所示,因为LISN的两路阻抗是一致的,所以为了使Vcbt产生的共模噪声最小,应该保证共模电感的匝比为1:1。使用具有更小ESL和ESR的电容也能够减小Vcbt产生的共模噪声。

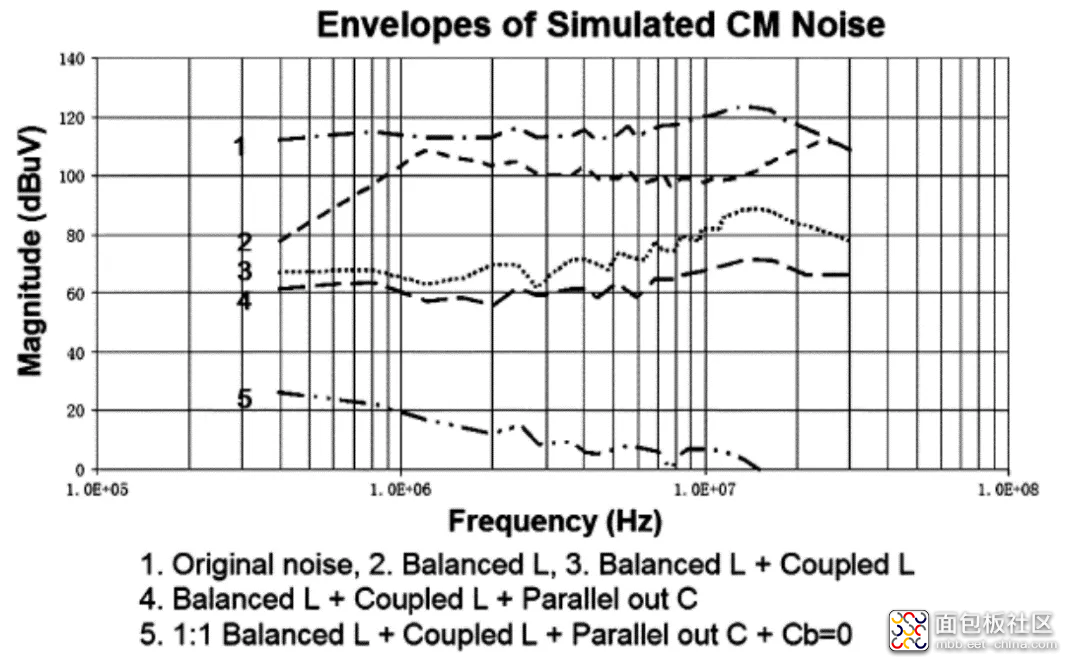

如下图是采取不同措施时共模噪声的幅值(仿真):

曲线2为将电感分为两个独立的300uH和100uH的电感,可以看出这样对低频段共模噪声有很大的改善,但是对高频段的作用却有限,这是因为高频段不能忽略电感寄生参数的影响。曲线3为加入耦合电感时的效果,自感分别为225uH和25uH,互感为75uH,即解耦电感也分别为300uH和100uH,从而高频段的噪声大大改善。曲线5为使用的是两个自感相同的耦合电感,即匝比为1:1,另外使用了80pF的电容与Ca并联,同时Cb设置为0,但实际中Cb不可能为0(这里文章介绍的所有措施都用上了,所以效果最好)。

实验:

在实验中,不太可能直接测量出Cb和Cc的值,但可以间接推算出来。可以采用两种方式:1. 调整耦合电感的匝比,直到获得最小的共模电感值,这时就处于阻抗平衡的状态,因为耦合电感变比已知,所以Cb+Cc可以计算出来;2. 首先确定电感的变比,然后通过并联Ca或Cc知道获得最小的共模噪声幅值,这时处于阻抗平衡的状态,Cb+Cc就可以从阻抗平衡的条件推算出来。

内容转载自应用电子笔记,仅供学习交流使用,如有侵权,请联系删除。

/1

/1