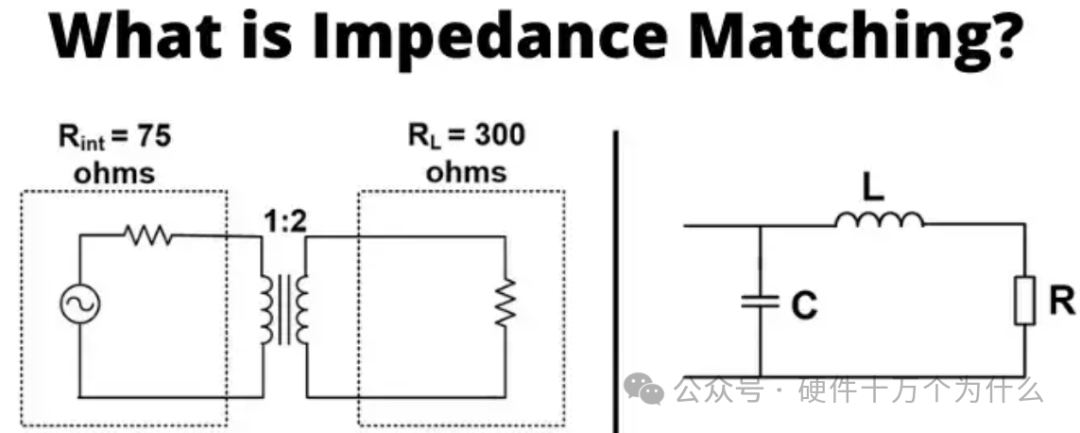

一、什么是阻抗匹配?

阻抗匹配指通过调整输入阻抗和输出阻抗来使得电子器件满足一定条件,通常该条件是使得系统传输功率最大或者使得信号反射最小。例如,再无线传输系统中需要匹配射频发射设备和接受天线的阻抗以此来实现传输功率最大化。

二、为什么要阻抗匹配?

1. 阻抗匹配作用

-

最大功率传输:对信号源和负载进行阻抗匹配,可以实现传输功率最大化,提高能量转换性能;

-

最小反射损耗:匹配阻抗可以减少信号在电路中的反射,提高信号质量和传输效率;

-

优化系统性能:阻抗匹配可以确保信号在系统中的稳定传输,避免信号失真和性能下降。阻抗匹配对于获得理想的 VSWR(电压驻波比)非常重要。

功放和喇叭的阻抗匹配以及高速电路的阻抗匹配虽然都涉及阻抗匹配的概念,但它们的具体应用和目的有所不同。

功放和音喇叭的阻抗匹配

在音频设备中,功放和喇叭的阻抗匹配是为了确保最佳的功率传输和音质。功放的输出阻抗和音箱的输入阻抗需要匹配,以确保最大功率传递到音箱上,并且不损坏设备。常见的匹配阻抗值是4欧姆、8欧姆等。如果功放的输出阻抗和音箱的输入阻抗不匹配,可能会导致功放无法提供足够的功率,音质变差,甚至可能损坏功放或音箱。

高速电路的阻抗匹配

在高速电路中,阻抗匹配主要是为了减少信号反射和确保信号完整性。高速信号传输线(如PCB走线、同轴电缆等)的特性阻抗需要与信号源和负载的阻抗匹配,以减少由于阻抗不匹配引起的信号反射和串扰。在数字电路中,常见的特性阻抗值有50欧姆、75欧姆等。

功放和音箱的阻抗匹配与高速电路的阻抗匹配是两个不同领域中的概念,尽管它们都涉及“阻抗匹配”,但其具体含义和实现方式有很大区别。

功放和音箱的阻抗匹配

功放(功率放大器)和音箱(扬声器):在音频系统中,功放负责将音频信号放大,并传输到音箱来输出声音。功放和音箱的阻抗匹配指的是功放的输出阻抗与音箱的输入阻抗之间的关系。

-

优化功率传输:为了保证最大功率传输,功放的输出阻抗应该与音箱的输入阻抗相匹配。常见的音箱阻抗值有4欧姆、6欧姆、8欧姆等。

-

保护设备:阻抗匹配能够防止功放在过载或失真情况下工作,延长设备的使用寿命。

-

选择合适的设备:选择阻抗匹配的功放和音箱。

调节输出阻抗:一些功放允许手动调节输出阻抗,以匹配不同的音箱阻抗。

功放和喇叭的阻抗匹配并不是简单地指它们的阻抗相同,而是指它们的阻抗之间具有适当的关系,以实现最佳的功率传输和系统性能。

理想阻抗匹配

最大功率传输:为了实现最大功率传输,功放的输出阻抗应当与喇叭的输入阻抗相匹配。在实际应用中,这意味着功放的设计通常是为了适应特定阻抗值的喇叭,如4欧姆或8欧姆。

功放和喇叭阻抗匹配的注意事项

设备标注的阻抗值:大多数功放和喇叭都会在设备上标注其额定阻抗值,例如“4Ω”、“8Ω”等。在选择设备时,确保功放的输出阻抗与喇叭的输入阻抗相匹配。

阻抗范围:许多功放可以处理一定范围内的阻抗。例如,一些功放可能标示可以支持4-8欧姆的喇叭,这意味着这些阻抗范围内的喇叭都可以与该功放匹配。

实际应用中的阻抗:在实际使用中,喇叭的阻抗会随着频率的变化而变化,因此标注的阻抗值通常是一个近似值。设计好的功放会考虑到这种变化,确保在大部分情况下都能实现良好的匹配。

示例

如果你有一个额定为8欧姆的喇叭,那么理想情况下,你的功放也应该支持8欧姆的输出负载。这种情况下,功放和喇叭的阻抗是匹配的,可以实现最佳的音频表现和功率传输。

功放和喇叭阻抗不匹配的影响

功率传输效率降低:如果功放的输出阻抗与喇叭的输入阻抗不匹配,可能导致功率传输效率降低。

设备损坏风险:严重的不匹配可能会导致功放过载,出现失真,甚至可能损坏功放或喇叭。

总的来说,确保功放和喇叭的阻抗匹配是音频系统设计和选择的重要环节,有助于实现最佳音频效果和系统可靠性。

高速电路的阻抗匹配

高速电路:在高速数字或射频电路中,信号以极高的频率传播。阻抗匹配主要涉及传输线(如同轴电缆、印刷电路板上的传输线)与负载之间的阻抗关系。

-

防止信号反射:在高速电路中,如果传输线的特性阻抗与负载阻抗不匹配,会导致信号反射,影响信号完整性和传输效果。

-

保证信号完整性:阻抗匹配能够减少信号失真和噪声,提高信号的质量和传输效率。

-

设计传输线:确保传输线的特性阻抗与负载阻抗一致。例如,使用50欧姆的同轴电缆时,负载阻抗也应该是50欧姆。

-

终端匹配电阻:在电路设计中使用终端匹配电阻,以匹配传输线的特性阻抗和负载阻抗。

关联

-

基础原理相同:两者都是为了实现阻抗匹配,以优化系统的性能。

-

具体实现不同:功放和音箱的阻抗匹配更多关注音频信号的传输效率和设备保护;高速电路的阻抗匹配主要关注信号完整性和反射问题。

总结来说,尽管功放和音箱的阻抗匹配与高速电路的阻抗匹配在基本原理上有相似之处,但它们在具体应用和实现方法上存在显著差异。

-

PCB场景

-

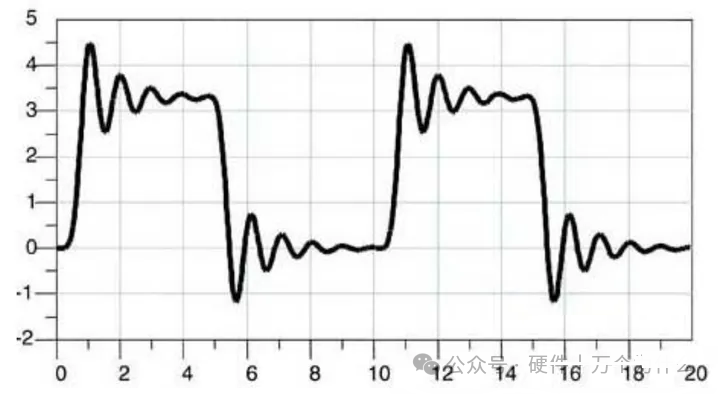

减少高频噪声以及边沿过冲。如果一个信号的边沿非常陡峭,则含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。串联电阻与信号线的分布电容以及负载输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。

-

减少高频反射以及自激振荡。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。

-

并行阻抗匹配又叫“终端阻抗匹配”,一般用在输入/输出接口端,主要指与传输电缆的阻抗匹配。例如,LVDS与RS422/485使用5类双绞线的输入端匹配电阻为100~120Ω;视频信号使用同轴电缆的匹配电阻为75Ω或50Ω、使用篇平电缆为300Ω。并行匹配电阻的阻值与传输电缆的介质有关,与长度无关,其主要作用也是防止信号反射、减少自激振荡。

-

低频和高频场景:

-

当信号传输中如果传输线上发生特性阻抗突变也会发生反射。

-

波长与频率成反比,低频信号的波长远远大于传输线的长度,因此一般不用考虑反射问题,也就是说低频电路做不做阻抗匹配也不会出现什么大问题。

-

在高频领域,当信号的波长与传输线长出于相同量级时反射的信号易与原信号混叠,影响信号质量,通过阻抗匹配可有效减少 消除高频信号反射。所以高频电路一定要做阻抗匹配。

1

1