掌握锁存器原理及应用

-

基本SR锁存器

-

钟控SR锁存器

-

钟控D锁存器

-

钟控D锁存器的动态参数

掌握触发器原理及应用

-

主从触发器

-

维持阻塞触发器

-

其它功能的触发器

一、基本SR锁存器

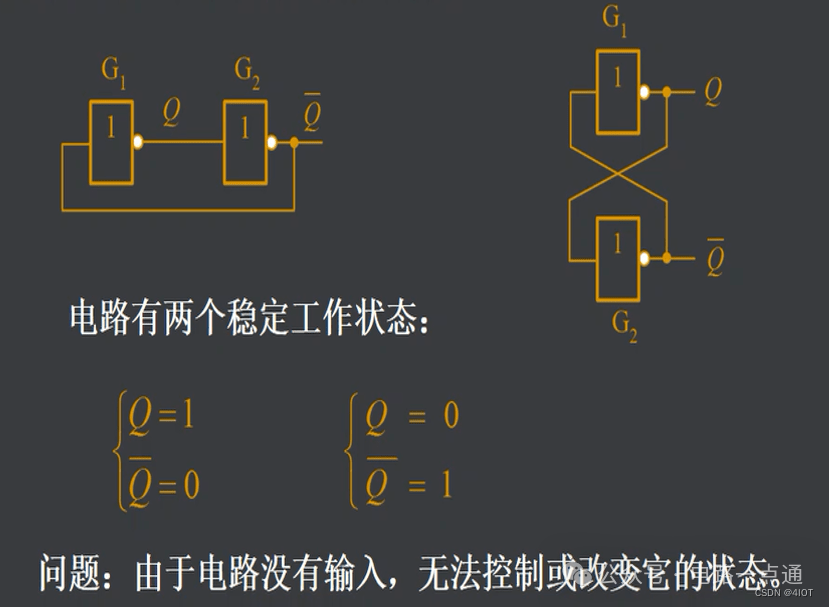

1、双稳态电路(Bistate Elements)

双稳态电路常见两种画法都是一样的,是由两个非门电路串联而成。

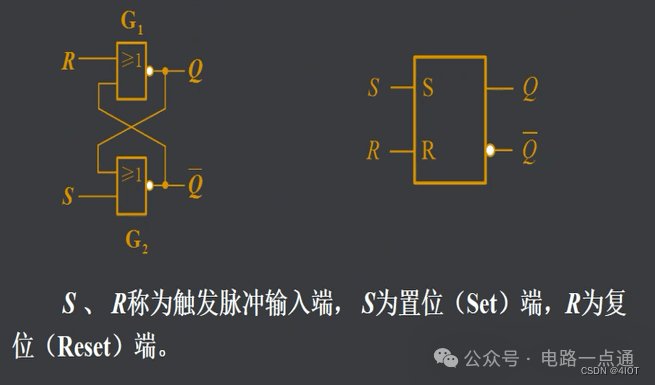

2、由或非门构成的基本SR锁存器

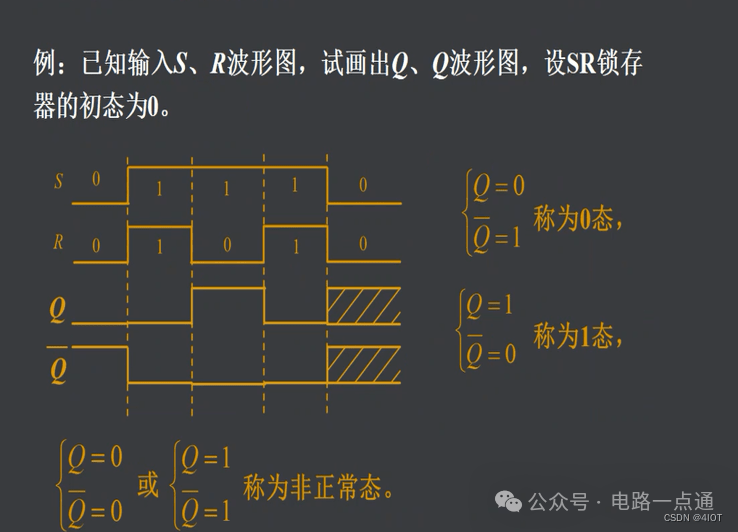

通过真值表分析输入和输出的关系。例:己知输入S、R波形图,试画出Q、Q波形图,设SR锁存器的初态为0。对于由或非门构成的基本SR锁存器采用正脉冲触发(S=1的时候触发)。

通过真值表分析输入和输出的关系。例:己知输入S、R波形图,试画出Q、Q波形图,设SR锁存器的初态为0。对于由或非门构成的基本SR锁存器采用正脉冲触发(S=1的时候触发)。 当Q和Q反=0或Q和Q反=1称为非正常态

当Q和Q反=0或Q和Q反=1称为非正常态

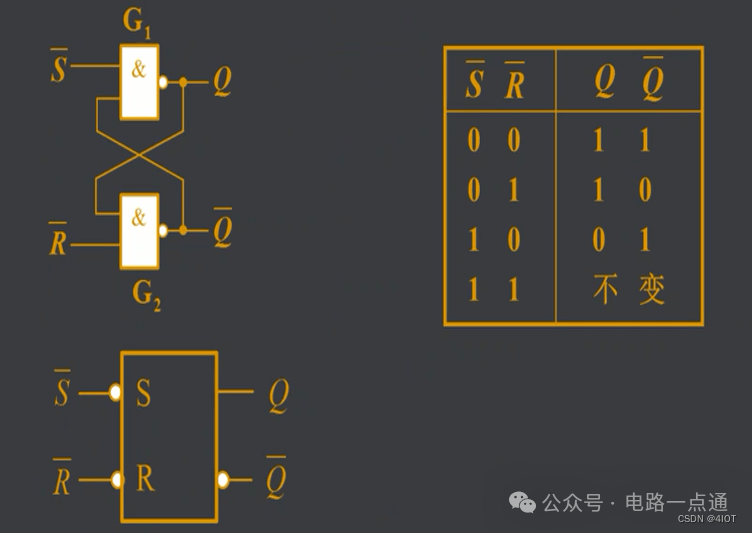

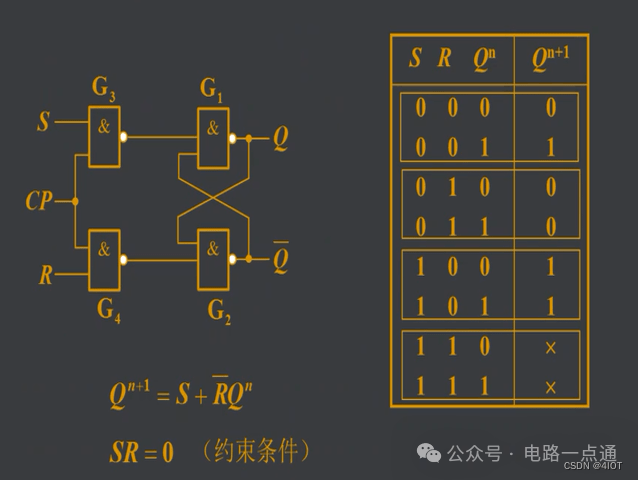

3、由与非门构成的基本SR锁存器

(1)电路结构和符号以及输入输出关系

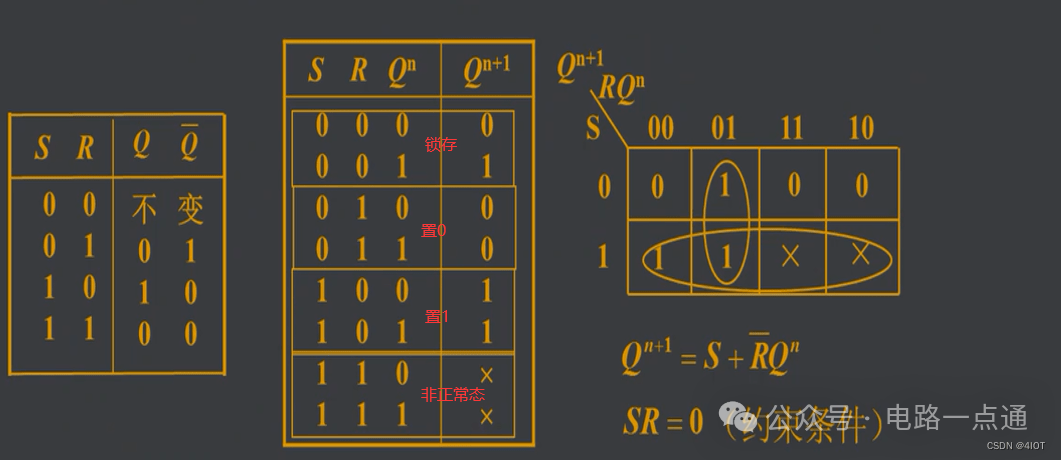

4.锁存器的特性表和特性方程

现态(Present State):锁存器在接收信号之前所处的状态,用Q^n表示;次态((Next State):锁存器在接收信号之后建立的新的稳定状态,用Q^(n+1)表示。特性表 驱动表 卡诺图 锁存器的约束条件是,S与R相与不能等于1 。

锁存器的约束条件是,S与R相与不能等于1 。

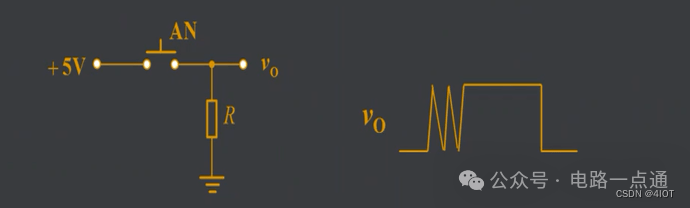

5、基本SR锁存器的应用

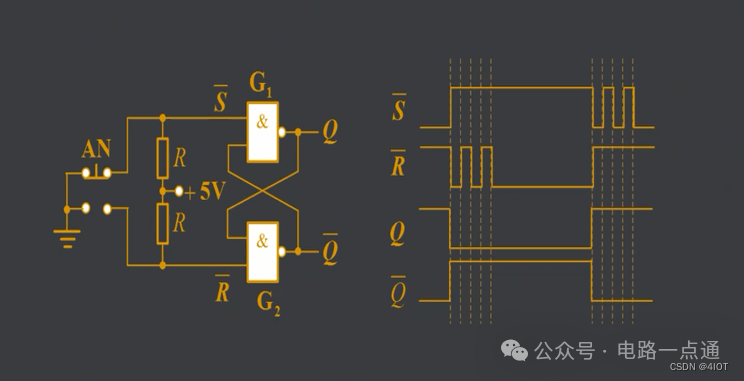

(1)作为存储单元,可存储1位二进制信息。(2)其它功能触发器的基本组成部分。(3)构成单脉冲发生器。(实际按键检测中,按下瞬间有抖动,通过锁存器可以解决)例:以下电路无法产生单脉冲: 按键Vo会输出一段抖动的电压。由基本SR锁存器构成的单脉冲发生电路,每按动开关一次,只输出一个正脉冲。

按键Vo会输出一段抖动的电压。由基本SR锁存器构成的单脉冲发生电路,每按动开关一次,只输出一个正脉冲。 锁存器分别都接入了1个电阻,5V的上拉。如果S=1,R有抖动,R也是1 的时候,我们是锁存状态,我们的输出Q反属于干净的波,还是一个钟状态,从而达到了消抖的目的。

锁存器分别都接入了1个电阻,5V的上拉。如果S=1,R有抖动,R也是1 的时候,我们是锁存状态,我们的输出Q反属于干净的波,还是一个钟状态,从而达到了消抖的目的。

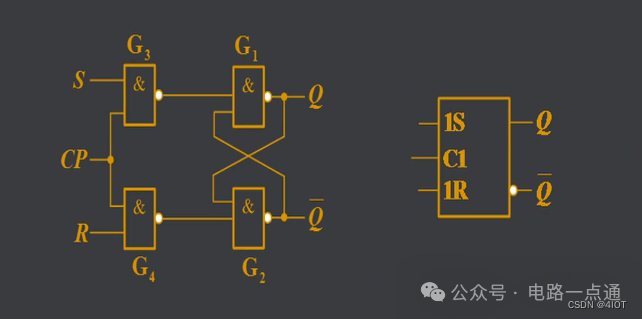

二、钟控SR锁存器

1、电路结构和逻辑符号

- CP=0:基本SR锁存器输入端均为1,状态保持不变,锁存状态

- CP=1:S、R通过与非门作用于基本SR锁存器

- 一是锁存器的抗干扰能力下降;

- 二是限制了锁存器的使用范围。

- 主从触发器

- 维持阻塞触发器

- 利用传输延迟触发器

- SR触发器

- D触发器

- JK触发器

- T触发器

- T'触发器

2、逻辑功能

S=0、R=0 锁存态,保持原来状态不变R=1 置0S=1 置1S、R同时等于1,不稳定状态。

S=0、R=0 锁存态,保持原来状态不变R=1 置0S=1 置1S、R同时等于1,不稳定状态。

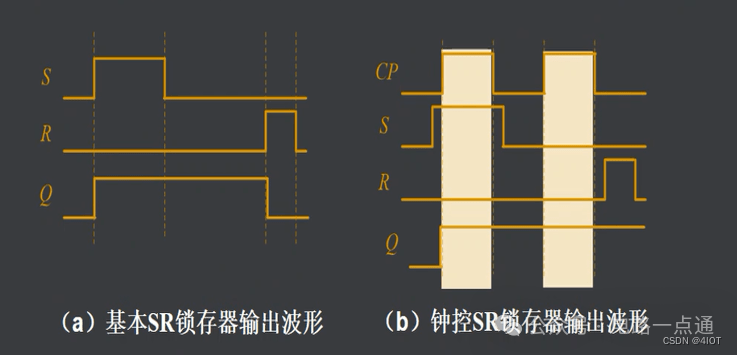

3、基本SR锁存器与钟控SR锁存器的区别

结论:钟控SR锁存器只在CP高电平期间接收输入信号,基本SR锁存器任何时候均能接收输入信号。CP相当于时钟线,只在高电平的时候采集数据。

结论:钟控SR锁存器只在CP高电平期间接收输入信号,基本SR锁存器任何时候均能接收输入信号。CP相当于时钟线,只在高电平的时候采集数据。

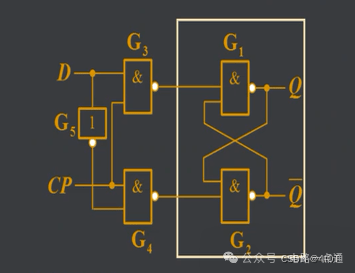

三、钟控D锁存器

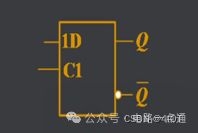

1、电路结构和逻辑符号

本质上是SR锁存器,CP时钟信号,一个输入引脚D,通过非门,输出一个D和一个D反。

本质上是SR锁存器,CP时钟信号,一个输入引脚D,通过非门,输出一个D和一个D反。

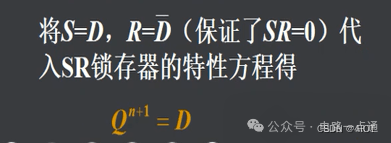

2、特性方程

3、特性表

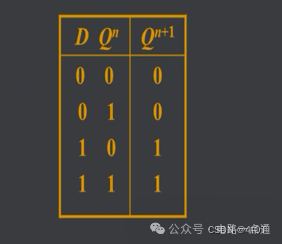

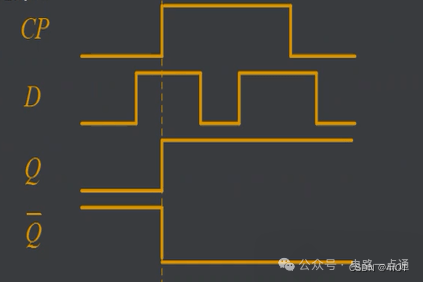

D和Q^n+1保持一致例:在钟控D锁存器输入如图所示的CP和D波形,试画出输出波形。假设锁存器初始状态为0。

D和Q^n+1保持一致例:在钟控D锁存器输入如图所示的CP和D波形,试画出输出波形。假设锁存器初始状态为0。 Q不在时钟脚下的时候,状态是保持不变的。“透明”锁存器(Transparent Latch),透明性表现在D和Q^n+1保持一致,锁存器在接收信号之后建立的新的稳定状态

Q不在时钟脚下的时候,状态是保持不变的。“透明”锁存器(Transparent Latch),透明性表现在D和Q^n+1保持一致,锁存器在接收信号之后建立的新的稳定状态

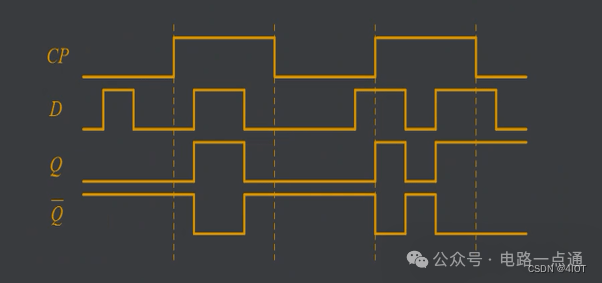

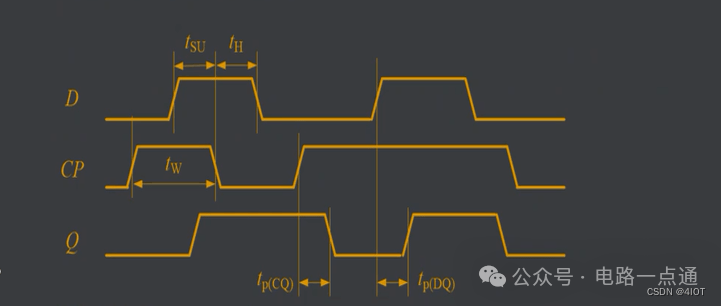

4、钟控D锁存器的动态参数(重点)

建立时间(Setup Time)——tSU(很多面试考题和芯片手册都会用到)

建立时间(Setup Time)——tSU(很多面试考题和芯片手册都会用到)数据信号D在时钟信号CP下降沿到来之前应稳定的最小时间保持时间(Hold Time)——tH

数据信号D在时钟信号CP下降沿过去以后应稳定的最小时间时钟信号和锁存器输出之间的延迟时间tp(CQ)

相对于CP信号由低电平变为高电平的时刻,Q的变化将会有一定的延时。输入数据信号和锁存器输出之间的延迟时间tp(DQ) 相对于D的变化,Q的变化将会有一定的延时。

5、钟控锁存器存在的空翻现象(缘由)

在一个CP脉冲周期内,锁存器状态变化多于一次的现象称为空翻。空翻带来两个问题:

在一个CP脉冲周期内,锁存器状态变化多于一次的现象称为空翻。空翻带来两个问题:

6、为什么钟控锁存器会存在空翻现象?

主要原因是锁存器对输入信号的敏感时间太长。触发器采用了不同的电路结构,只有在CP脉冲的上升沿或下降沿时刻接收输入信号(Q才会动),一个周期内最多翻转一次,防止了空翻现象。我们在做单片机的时候,输入模式和中断有很多种方式,我们可以高电平检测、低电平检测、上升沿检测、下降沿检测。触发器是应用于上升沿或下降沿监测,防止了空翻现象。

四、触发器的分类

3种不同结构的触发器

5种不同功能的触发器

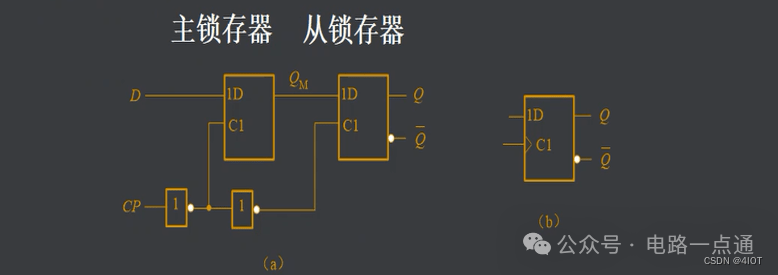

五、主从D触发器

1、主从D触发器电路结构及逻辑符号

2、工作原理

当CP=0时,QM跟随D变化(钟控D锁存器),从锁存器保持不变(截止)当CP=1时,主锁存器保持不变,从锁存器跟随Qm变化主从D触发器的状态只有在CP上升沿时刻才会改变3、主从D触发器的特性方程

上图中:D从0->1,如果CP时钟引脚不在高电平的时候,我们Q是不变化的,当CP引脚高电平的时候,我们检测到了D的上升沿,这时候我们Q也是高电平,随后我们D的变化与Q无关。主从D触发器的状态只有在CP上升沿时刻才会改变演变的另一个触发器,增加了2个外部输入具有直接置0端和直接置1端的主从D触发器

上图中:D从0->1,如果CP时钟引脚不在高电平的时候,我们Q是不变化的,当CP引脚高电平的时候,我们检测到了D的上升沿,这时候我们Q也是高电平,随后我们D的变化与Q无关。主从D触发器的状态只有在CP上升沿时刻才会改变演变的另一个触发器,增加了2个外部输入具有直接置0端和直接置1端的主从D触发器 直接置1端和直接置0端不受CP脉冲控制,用于设置触发器的初始状态,正常工作时,应置高电平。

直接置1端和直接置0端不受CP脉冲控制,用于设置触发器的初始状态,正常工作时,应置高电平。

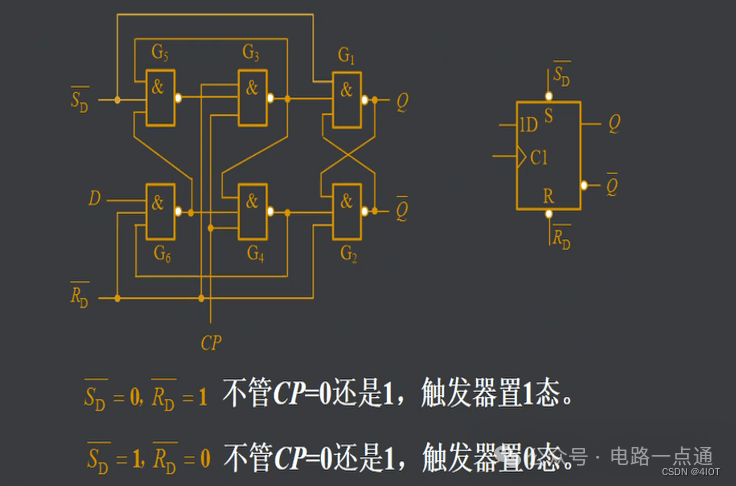

六、维持阻塞D触发器

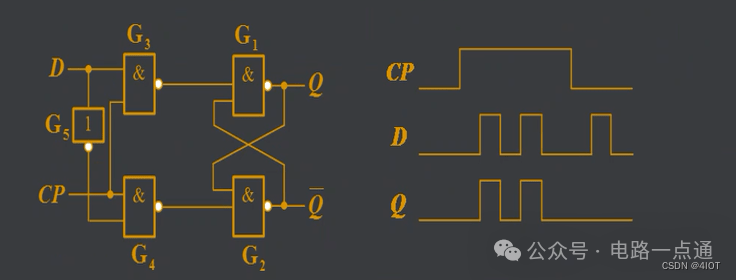

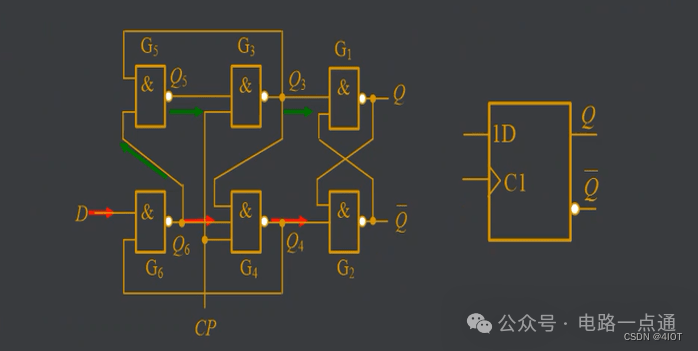

1、电路结构和逻辑符号

G1、G,2构成了基本SR锁存器。

G1、G,2构成了基本SR锁存器。G3、G4、G5、G6构成了D信号的输入通道。

2、工作原理分析

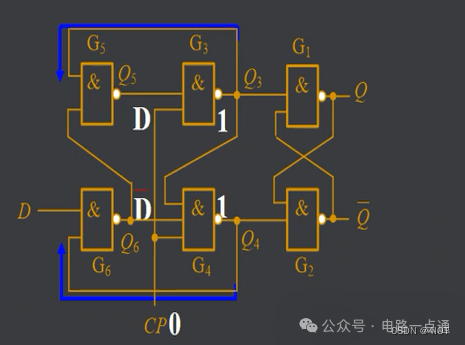

当CP=0时:

当CP=0时:(1)触发器维持原状态不变;

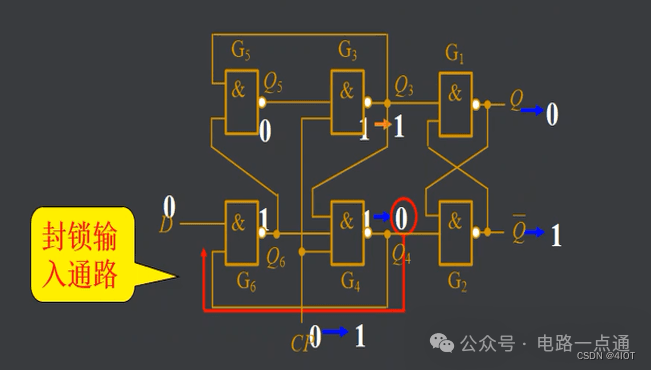

(2)输入信号D到达G4、G3的输入端,等待送入。当CP由0->1时,如果D=0,

Q^(t+1)=D=0,并立即封锁输入通路。

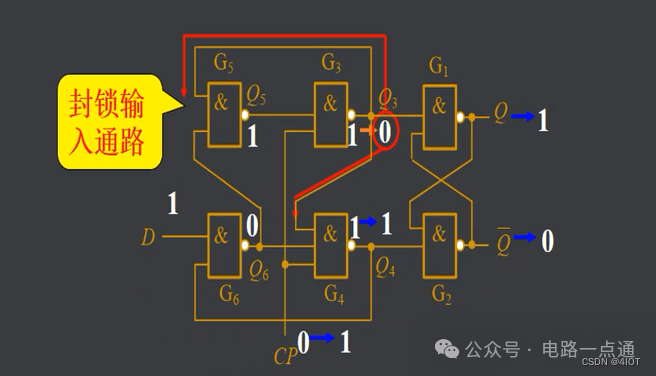

当CP由0->1时,如果D=1,

当CP由0->1时,如果D=1,则Q^(n+1)=D=1,并立即封锁输入通路。

结论:在CP上升沿接收输入信号,Q^(n+1)=D。

结论:在CP上升沿接收输入信号,Q^(n+1)=D。

3.具有异步置位、复位端的维持阻塞D触发器

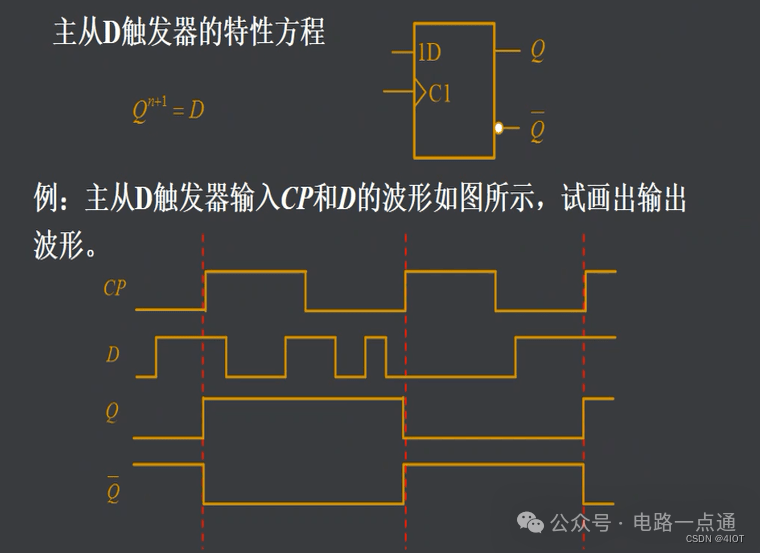

七、五种不同功能的触发器

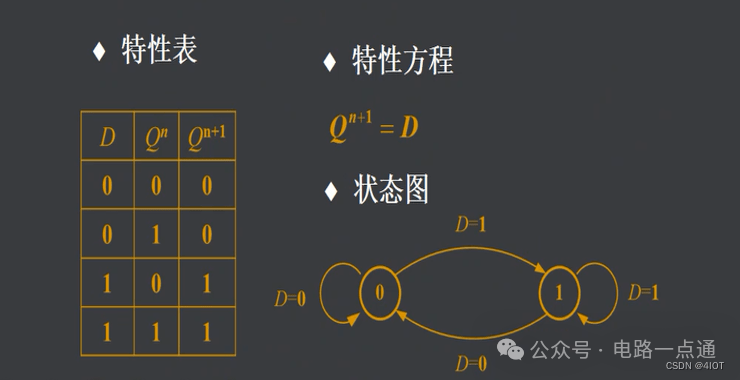

1、D触发器

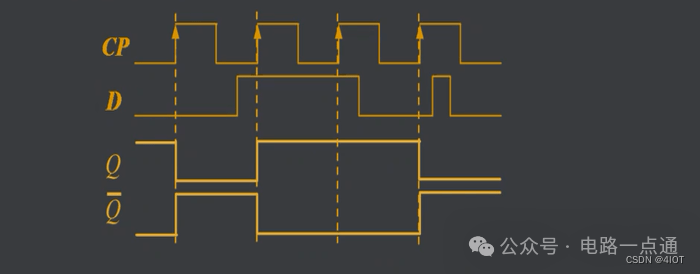

D触发器可以采用不同电路结构,但功能符号是一样的。在分析和设计时序逻辑电路时,并不需要考虑触发器的内部电路结构,而只需关心触发器的逻辑功能和触发方式。 例:一上升沿触发的D触发器,设初态为1,试在给定CP、D下,画出输出波形。

例:一上升沿触发的D触发器,设初态为1,试在给定CP、D下,画出输出波形。 边沿触发器只有CP的上升沿或下降沿瞬间才能接受控制输入信号,改变状态,因此在一个时钟脉冲下,触发器最多只能翻转一次,从根本上杜绝了空翻的现象。

边沿触发器只有CP的上升沿或下降沿瞬间才能接受控制输入信号,改变状态,因此在一个时钟脉冲下,触发器最多只能翻转一次,从根本上杜绝了空翻的现象。

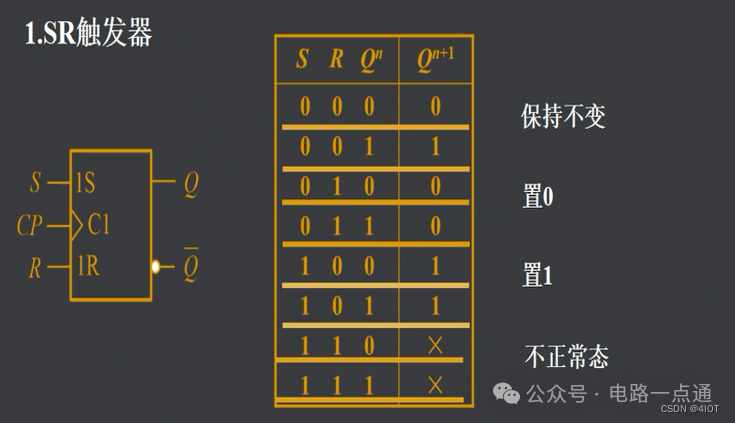

2、SR触发器

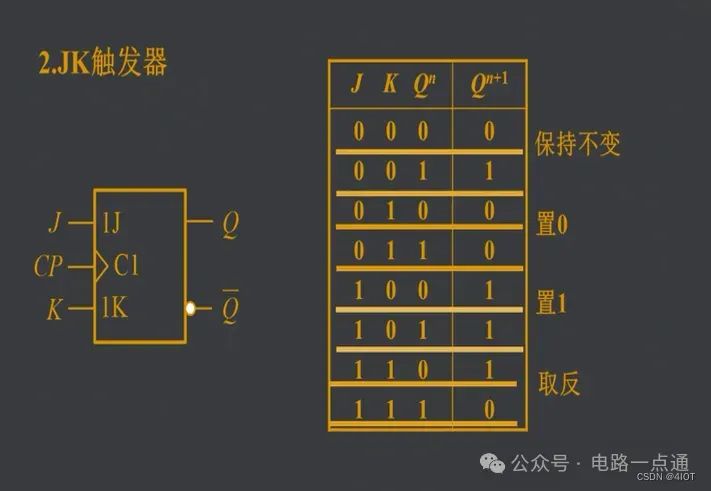

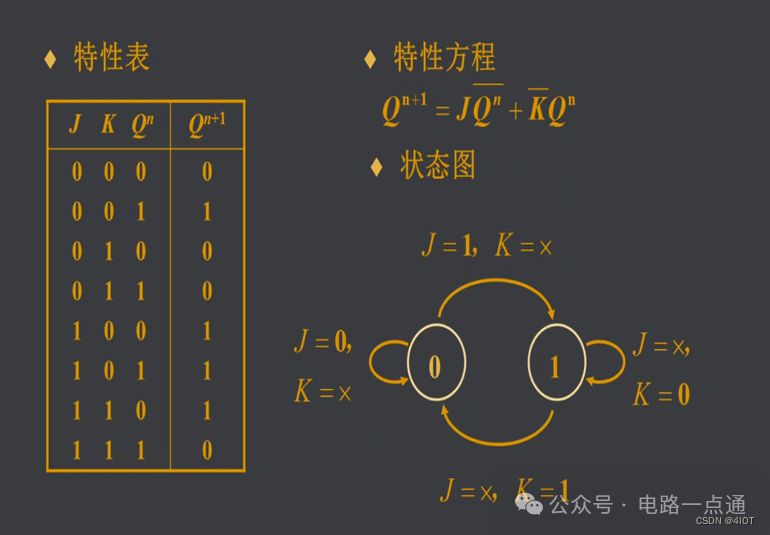

3、JK触发器

与SR相比,在不稳定状态下,Qn由0变1,Qn+1由1变0。把不稳定状态设计成了反转,可以用来计数

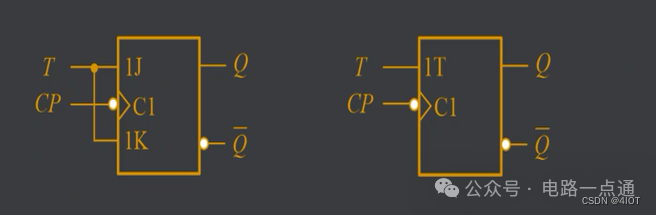

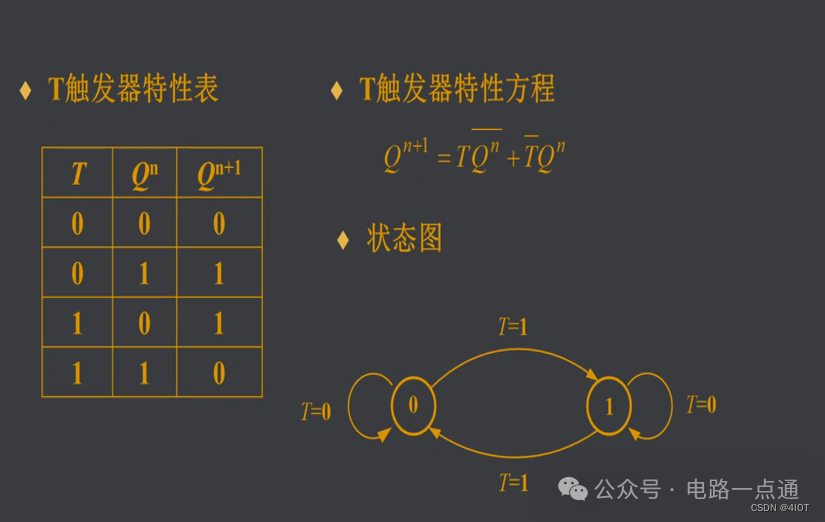

4、T触发器

如果将JK触发器的J、K端连接在一起,并将输入端命名为T,就得到T触发器。也可以用来计数的功能

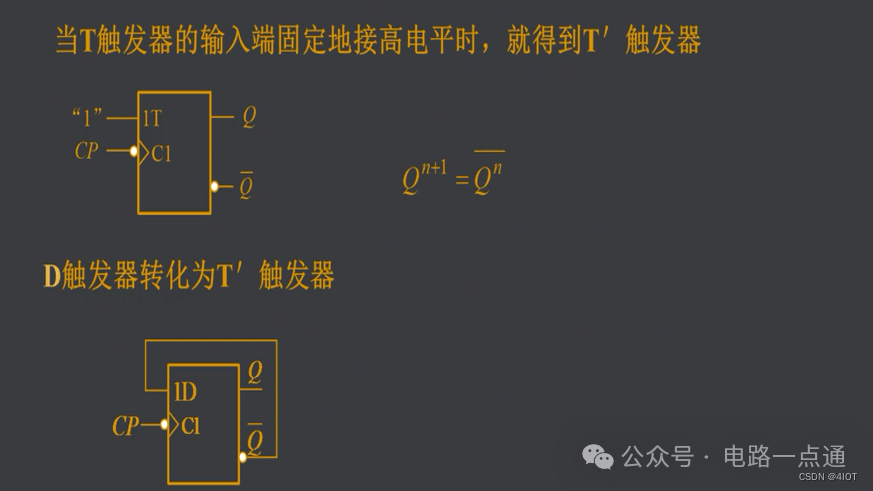

5、T'触发器

当同时为1的时候,取反。可以利用D触发器转换为T'触发器。

本文链接:https://blog.csdn.net/m0_60718520/article/details/127701668

分享

0

0