为什么要进行采样点测试?

为什么要进行采样点测试?

为了保证有效的通信,对于一个只有两个节点的CAN网络,其两边距离不超过最大的传输延迟和每个节点的时钟容差能够正确地接收和解码每个传输的消息,这需要每个节点都能对每个位正确采样。

CAN总线的每一帧可以看作一连串的电平信号。大多数设备使用单点采样,也就是在一个位时间内从采样点的位置读取一个电平信号,以此确定这个“位”的显隐性。在CAN网络中,当每个节点的采样点位置不一样时,由于总线过长引起的通信延迟或现场对总线的干扰,就容易发生读取的电平不一致现象,产生CRC错误报文。为了提高CAN网络的通信成功率,各节点的采样点应设置一致。

如何计算采样点?

如何计算采样点?

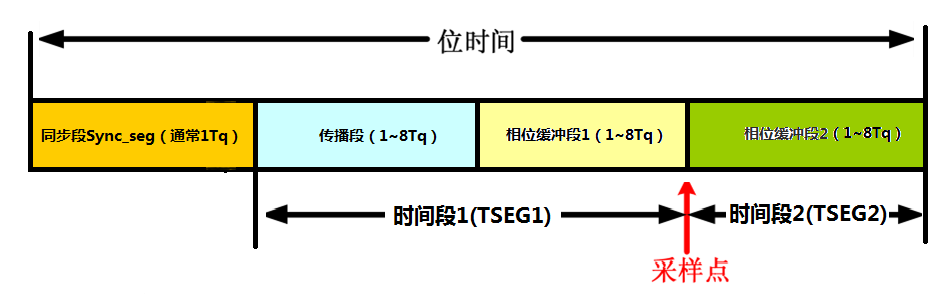

在讲采样点之前,我们先了解一下位时间的相关定义。一个位时间可以看作一条水平的时间轴,一般分为四个段,如图1:

图1 位时间图

-

同步段:通过此段实现时序调整,一个位的输出从同步段开始;用于同步总线上的各个节点,跳变沿产生在此段内;通常为1Tq;

-

传播段:用于补偿信号通过网络和节点传播的物理延迟;传播段长度应能保证2倍的信号在总线的延迟;其长度可编程(1-8Tq);

-

相位缓冲段1和相位缓冲段2:重同步在此段作用,用于补偿细微的时钟误差。作用方式为加长相位缓冲段1或者缩短相位缓冲段2;

-

Tq:是指一个最小时间量子,来源于对系统时钟可编程的分频;

-

时间段1:为了方便编程,许多CAN模块将传播段和相位缓冲段1合并为一个时间段(TSEG1)。

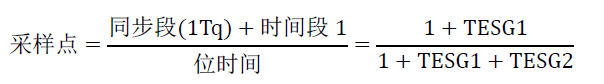

公式1

公式2

Prescaler:波特率分频系数

例:时钟频率为8M,Prescaler = 2,Tseg1 = 13,Tseg2 = 2;

由公式2可得:波特率 = 8M/((1+13+2)*2)=250K;

由公式1可得:采样点=(1+13)/(1+13+2)=87.5%;

图2 采样点配置

由图2可以看出:在同一波特率的条件下,Tseg1、Tseg2、Prescaler有不同的组合,不同的组合有不同的采样点配置,可自行配置适合采样点位置。

CANDT采样点测试的测试原理是什么?

CANDT采样点测试的测试原理是什么?

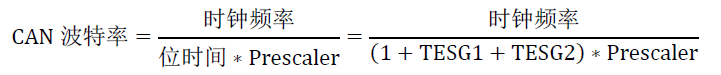

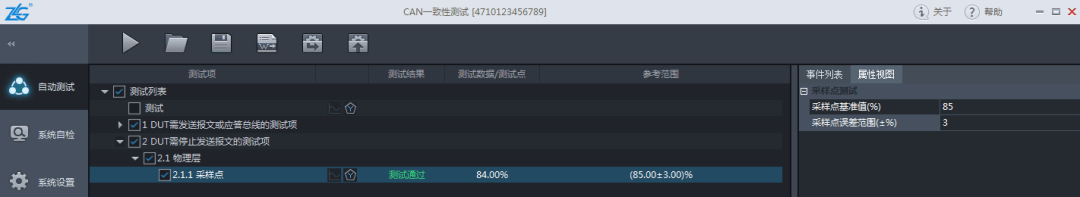

连接CANDT设备和电脑后,再在电脑上打开CANDT软件,选中“采样点”并设置好对应的参数,然后开始测试即可进行采样点的测试,如图3,最终的测试结果为:84%。

图3 CANDT测试结果

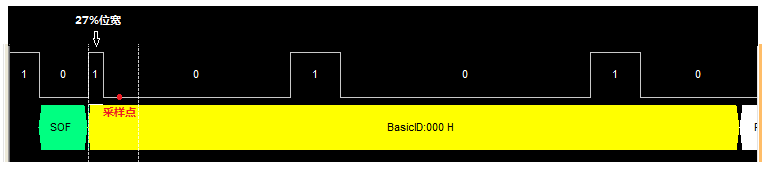

1、用CANScope发送ID 为0的报文100帧,在此报文的第一个ID位(1注1)的0%处施加一个宽度为27%位宽(2注2)的干扰(如图4),记录这100帧报文中出现的错误帧数,但由于此时距离采样点位置较远,暂时不会出现错误帧。

图4 干扰1

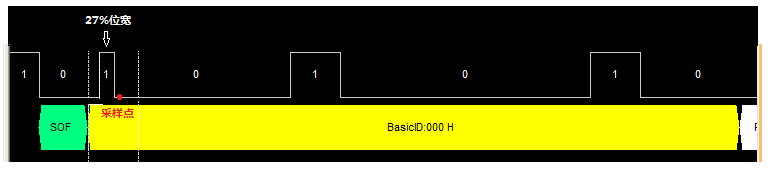

2、27%位宽的干扰逐渐以1%位宽的步进向右移动,在干扰的右边沿快靠近采样点时(如图5),由于通信延迟的关系,此时采到的电平和CANScope发送的不一致了,导致DUT接收到的CRC校验和DUT计算的CRC校验不一致,DUT就会主动发出错误帧,把每一个不同干扰位置的错误帧数记录下来。从此刻开始,继续往右步进,错误帧数也会有所增加。

图5 干扰2

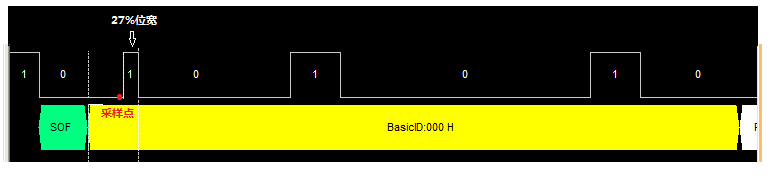

3、继续步进,当干扰的左边沿位置过了采样点后(如图6),此时DUT就不会再出现错误帧了。因此,最后一个出现错误帧的位置就是我们想要知道的采样点位置。

图6 干扰3

1、确保CAN总线上的终端电阻为60Ω。当CAN总线上终端电阻为120Ω或其他值时,虽然在正常情况下可以通信,但在采样点测试时,会对结果产生一定的偏差。

2、采样点测试过程中不允许DUT发送报文,因为采用的是发送100帧报文和检测错误帧的方法,DUT发送报文会造成判断的误差,影响测试结果的准确性。

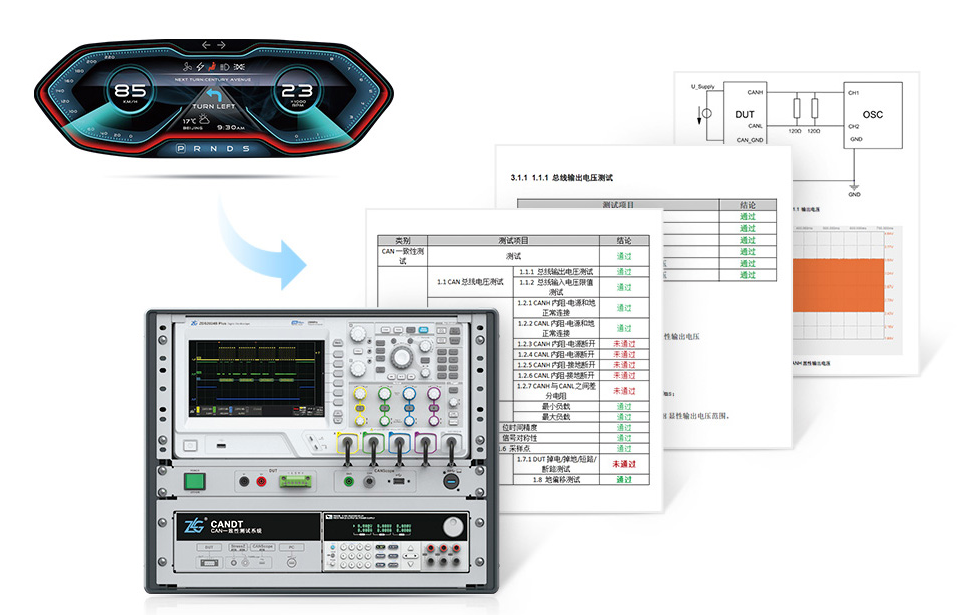

CAN一致性测试系统——CANDT

CAN一致性测试系统——CANDT

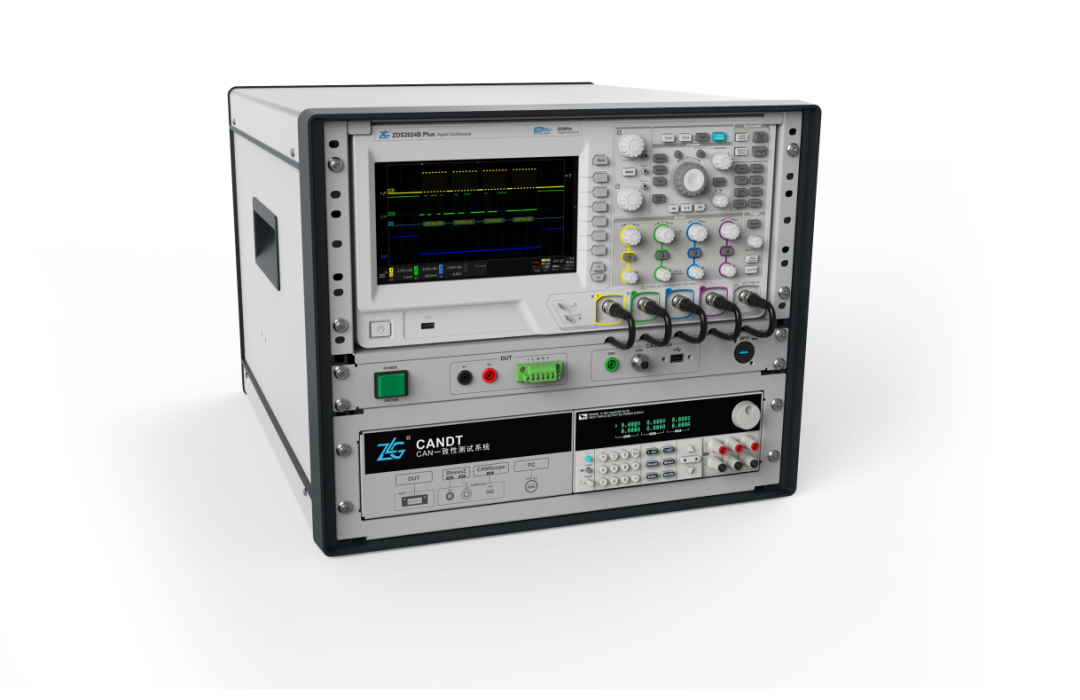

CANDT是基于CANScope强大的CAN总线底层测试分析基础,配备必要的电压源、PLC等核心外围设备,可自动化完成汽车零部件CAN节点物理层、链路层及应用层测试的CAN一致性测试设备。

物理层测试的目的是验证节点及测试系统在电路设计、物理电平特性等方面的性能,就是保证节点能够正确连入总线的基础,其测试内容包括电阻电容特性、节点差分电阻、故障容错测试、CAN线上的物理电平特性等等。

数据链路层的测试目的是保证每个节点的通讯参数能够保持一致性,所组成的网络能够正常有效的工作,内容包括位定时测试、采样点测试、SJW测试等等,节点测试完成后,可自动化导出详细CAN一致性测试报表,准确判断节点工作情况,一目了然。

图7 CANDT一致性测试系统

图8 一致性测试报表

本文源自微信公众号:ZLG致远电子,不代表用户或本站观点,如有侵权,请联系nick.zong@aspencore.com 删除!

0

0