TimeQuest Timing Analyzer是一个功能强大的ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)约束、分析和报告方法来验证你的设计是否满足时序设计的要求。本文采用一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。

2、T

imeQuest 时序分析的基本概念

TimeQuest需要读入布局布线后的网表才能进行时序分析,读入的网表是由以下一系列的基本单元构成:

-

cells:

Altera器件中的基本结构单元,如LE;

-

pins:

cell的输入输出端口,也可以认为是LE的输入输出端口,注意,pins不包括器件的输入输出管脚,代之以输入引脚对应LE的输出端口,输出引脚对应LE的输入端口;

-

nets:

同一个cell中,从输入pin到输出pin经过的逻辑。但需特别注意,网表中连接两个相临cell的连线不被看作net,被看作同一个点,等价于cell的pin,还需要注意,虽然连接两个相临cell的连线不被看作net,但是这个连线还是有其物理意义的,等价于altera器件中一段布线逻辑,会引入一定的延迟(IC-Inter-Cell);

-

ports:

顶层逻辑的输入输出端口,对应已经分配的器件引脚;

-

clocks:

约束文件中指定的时钟类型的pin,不仅指时钟输入引脚;

-

keepers:

泛指port和寄存器类型的cell;

-

nodes:

范围更大的一个概念,可能是上述几种类型的组合,还可能不能穷尽上述几种类型。

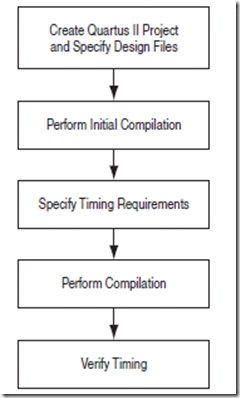

3、TimeQuest的基本操作流程

做为altera FPGA开发流程中的一部分,TimeQuest执行从验证约束到时序仿真的所有工作。Altera推荐使用下面的流程来完成TimeQuest的操作。

-

建立项目并加入相关设计文件

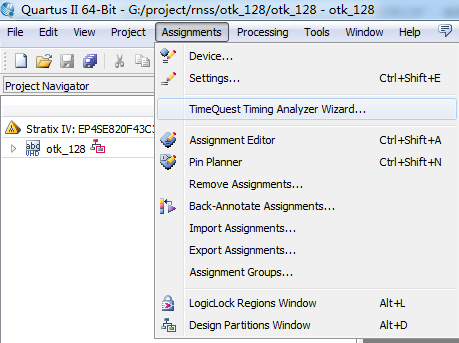

无论做什么事情,都需要有目标或者说对象。我们用TimeQuest做时序分析,对象就是我们的设计。首先是建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。需要注意的是,这里的设计文件,包含逻辑设计相关的文件和已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。关于 sdc文件,可以使用Quartus的向导来建立,在生成sdc文件后,可以再在此sdc文件上自己修改,如下图所示,Assignments->TimeQuest Timing Analyzer Wizard...

-

对项目进行预编译(initial compilation)

项目建立以后,需要对项目进行预编译。这里的预编译是对应于全编译(full compilation)来讲的,可以理解为预编译是对项目进行部分的编译,全编译是对项目进行完整的编译。进行预编译的目的是为了生成一个initial design database,然后我们可以根据这个database用Timequest采用交互的模式生成时序约束。事实上,对于小的设计,编译时间并不是很长的话,完全可以不区分预编译和全编译,需要编译的时候,全编译就可以了,如果做全编译,可以生成一个post-fit的database,完全可以给TimeQuest使用。

-

向设计中添加时序约束

在用TimeQuest做时序分析之前,必须要指出对时序的要求,即时序约束。这些约束包括时钟,时序例外(timing exceptions)和输入/输出延时等。默认情况下,Quartus II 软件会给所有没有被下约束的时钟都设定为1GHz。没有任何的时序例外,即所有的timing path都按1T去check。所有的输入/输出的延迟都按0来计算。这显然不符合绝大多数设计的时序要求,所以有必要根据设计的特性,添加必要的时序约束。如上所述,时序约束主要包括三类:时钟,时序例外和输入/输出延迟。其中时钟和输入/输出延迟可以认为是在某种程度上增强时序设计的要求。时序例外可以认为是在某种程度上降低时序设计的要求。比如,仅仅设定一个时钟的频率为100MHz,这个时钟域里所有timing path都需要能工作在100MHz下。显然,这是增强了时序设计的要求。可是如果在这个时钟域下,有部分timing path是不需要做1T的check的,就可以通过添加时序例外来避免对这些timing path做1T的check,即降低了时序设计的要求。在用TimeQuest做时序分析时,如果非常熟悉设计的构架和对时序的要求,又比较熟悉sdc的相关命令,那么可以直接在sdc文件里输入时序约束的命令。而通常情况下,可以利用TimeQuest GUI提供的设定时序约束的向导添加时序约束。不过要注意的是,用向导生成的时序约束,并不会被直接写到sdc文件里,所以如果要保存这些时序约束,必须在TimeQuest用write sdc的命令来保存所生成的时序约束。

-

执行完整的编译

如果没有添加时序约束,那么软件在编译的时候,会按照默认的时序约束对设计进行优化,对于绝大多数的设计,都会报出来时序的问题,但因为默认的时序约束与设计本身的要求在绝大多数情况下,都是不同的,所以这些时序的问题也并不是设计本身的问题,并没有太多的参考价值,而且很多初学者也不会注意到这个问题。这样就把设计中很多潜在的时序问题给隐藏起来了,最终带来的可能就是系统运行的不稳定,甚至是完全不能运行。

-

验证时序

当完成编译以后,我们就可以用TimeQuest来验证时序了。在时序分析的过程中,TimeQuest会分析设计中所有的timing path,计算每一条timing path的延时,检查每一条timing path是否满足时序约束,最后按照positive slack或negative slack来报告时序分析的结果。其中negative slack就表示对应的timing path不满足时序约束的要求(timing violation)。

如果遇到有不满足时序要求的情况,则可以根据对应的时序报告分析设计,确定如何优化设计使之满足时序约束。时序约束有任何变化的话,都需要重新编译设计。这个反复的过程可以让我们解决设计中的时序问题。

4、时序参数说明

-

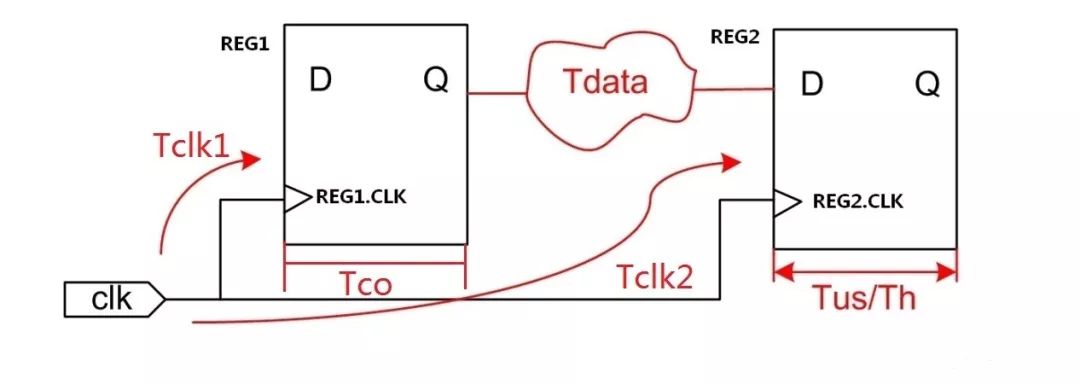

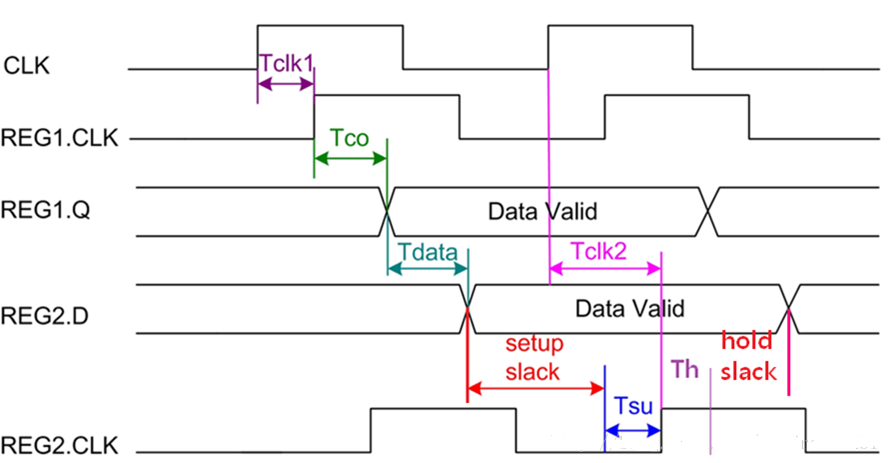

Setup Time与Hold Time

Setup Time 定义为数据信号必须在时钟信号边沿出现前准备好的的最短时间。用Tsu表示;则正确的数据出现的时间点要比时钟信号边沿时间点Tedge提早Tsu以上,才会在时钟边沿触发点抓到正确数据。

Hold Time定义为数据信号必须在时钟信号边沿出现后维持住的最短时间。用Th表示;则正确的数据出现的时间点要比时钟信号边沿时间点Tedge之后Th时间以上才能变换数值,才会在时钟边沿触发点抓到正确数据。

-

Slack

Slack是一个区间,可以判断是否时序符合要求。Slack值为正值,代表综合出来的时序需求为符合,反之,不符合。

-

Setup Slack 与 Hold Slack

Setup Slack 为正值,代表正确的数据到达时间点都能满足数据准备时间的需求 。

Hold Slack 为正值,代表正确的数据到达时间点都能满足数据保持时间的需求 。

4. Data Arrival Time

Data Arrival Time 定义为输入端时钟上升沿触发的时间点 加上Tclk1 加上Tco加上Tdata。

0

0