SMT论坛上有这么一个帖子,大概的问题是锡膏工艺后PCB上的晶振无法起振,排除虚焊、短路问题,在晶振回路区域用洗板水擦洗或者烙铁焊一下之后,晶振即恢复正常,而且问题可双向复现——

这已经是2011年的一个帖子了,现在到论坛上还能看到江湖上各位同行为解决该问题提出的各种建议。很遗憾,抛出这个帖子的工程师最后没给出他的实验结论,然而综合各种说法,该问题基本锁定在焊锡过炉工艺不良导致的质量问题!

大部分的研发人员所熟悉的锡膏、过炉工艺管控基本停留在锡膏存储、炉温不良所带来的虚焊、假焊问题,这些问题所呈现出来的现象通常在生产现场就能得以暴露并进行纠正,如塌陷、锡珠、歪斜、空洞等现象。

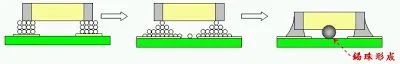

炉温升温太快导致气体挥发外带锡膏形成的锡珠

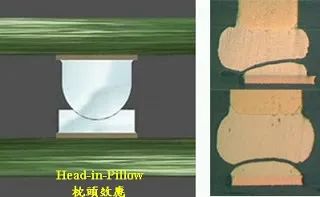

管脚与焊盘温度不平衡导致虚焊

零件两端锡膏湿润不平均导致歪斜

除却焊接不良问题,隐秘的角落:锡炉温度和走板速度搭配不当可能带来未知的隐患问题。这样的不良无法使用肉眼识别,通常等到我们发现异常的时候,一整批板子已经坐等上线组装甚至已经外发到用户终端。

锡炉温度和走板速度搭配不当,会导致助焊剂残留无法完全分解,活性极强的助焊剂容易在过锡缸后留下一些固态或粉状残留物。这些残留物会吸收空气中的水分,使潮气侵入芯片或零件管脚的金属化层,当电路板表面产生一个薄潮气层时,会降低电路板表面包括焊脚与焊盘之间的绝缘电阻、改变其中的寄生电容。

隐患 1

前文提到的晶振不良问题在使用洗板水擦洗或烙铁焊之后可恢复正常的问题,极大可能就是残留物吸收湿气之后导致晶振与板子之间的寄生电容产生与通用理论值较大的差异,如果晶振振荡回路设计冗余量较低,则容易出现晶振无法起振的问题(参考)。

隐患 2

在带有高压电设计的PCB中,助焊剂残留物、薄潮气层会降低电路板表面的绝缘电阻,绝缘阻抗降低会导致高压电容易出现放电击穿现象,笔者曾碰到的一个类似问题就是在一款强电产品中,由于波峰焊过炉速度太快,锡膏助焊剂挥发附着在板材上降低强电绝缘度,存储、运输过程中吸附空气中的水汽之后,绝缘度进一步降低,这直接导致了在生产车间老化后的产品无问题,但在整机产品到达客户手中,第一次上电时就概率性出现火花放电,类似爆炸的现象。

隐患 3

在低功耗产品中,电路板的薄潮气层会造成电路板腐蚀或生成金属枝晶,当枝晶出现在线路或焊区之间桥接时,会出现漏电问题。对于低功耗产品,漏电问题将直接导致产品使用寿命缩短。

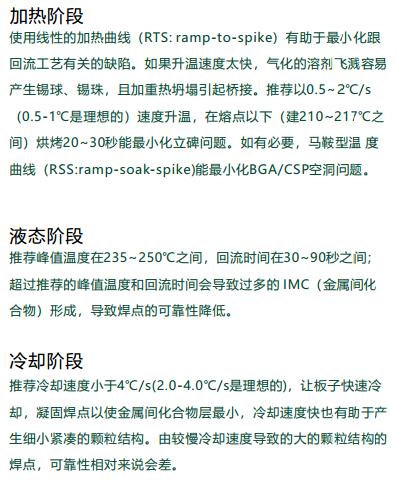

如下是适普SF710无铅锡膏的一个过炉曲线,

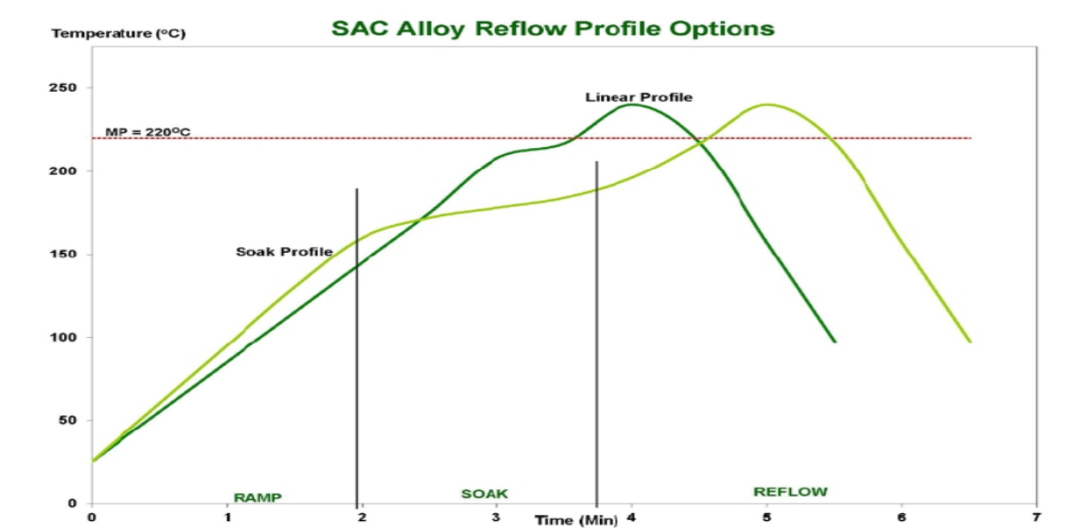

这其中包括加热阶段、液体阶段、冷却阶段的相关推荐说明——

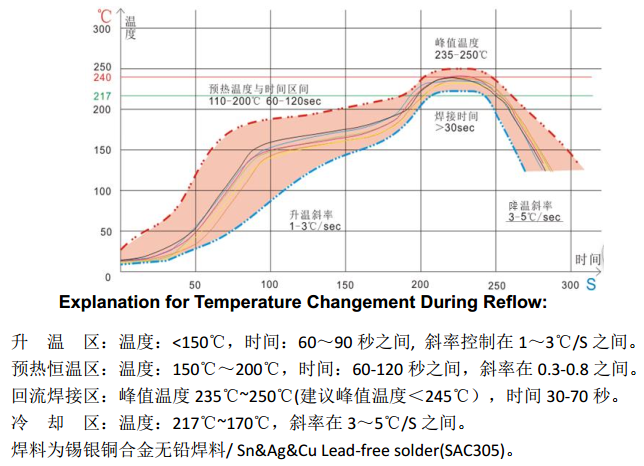

对于器件,特别是CPU,规格书中所提供的回流焊曲线可能会被很多工程师所忽略,其实这样的一个曲线可以作为SMT时炉温调试的一个参考,如下:

因此,严瑾的生产过程中,你最好要清楚锡膏、器件所推荐的炉温与过炉速度,在试产阶段,工程人员务必将锡膏型号、SMT过炉曲线进行记录、存档,后续的量产尽量保持一样的生产条件。为避免助焊剂残渣、湿气腐蚀,在成本可控的情况下还需要进行PCBA清洗、涂覆三防漆操作,这样的管控虽然繁琐,但可以让PCBA避免掉隐秘角落里的很多质量隐患!

0

0