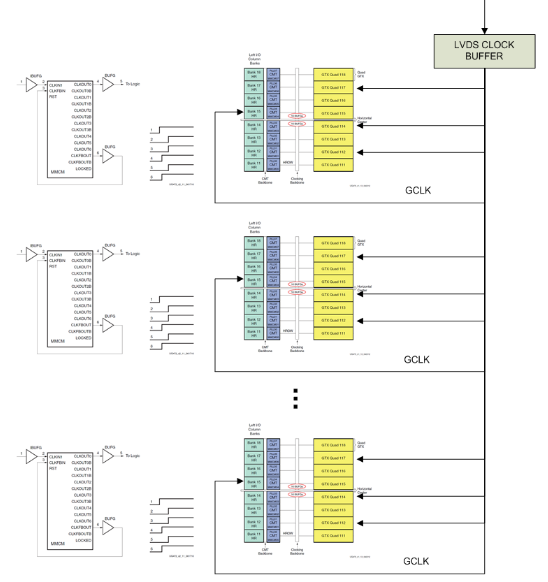

这里介绍一种利用MMCM实现多芯片相位对齐的串行收发器纠偏方法:

1) 利用图1所示电路实现多芯片间的全局时钟相位对齐。该电路通过单板上的low Skew时钟分配器分发同相位时钟到多个相同的芯片的相同全局时钟管脚上,再由MMCM实现零延迟BUFG电路,实现到每个GT的USRCLK/2的延迟差最小,达到全板GT的USRCLK/2同相位的目的。

图1. 时钟架构图

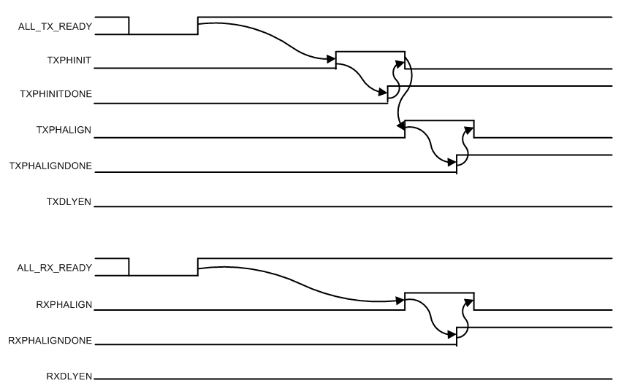

2) 利用7系Tranceiver的Phase_Aligner实现TX/RXBUFFER Bypass。

7系列GT(GTX,GTH,GTP)支持TXBUFFER/RXBUFFER Bypass功能,该功能将Tranceiver内部的XCLK的相位调整到与TXUSRCLK或RXUSRCLK同相(误差小于1UI)。这样,由于整个单板的所有通道的TXUSRCLK和RXUSRCLK同相位(由时钟架构保证。即使有误差,也可以重复并在设计中校准)。具体Phase_Aligner控制时序见图2.

图2. 全局时钟作为TXUSRCLK/RXUSRCLK的Phase_Aligner控制时序图

应用案例:某公司需要一个2048通道,且延迟差在250pS内的解决方案。系统分解到8块单板实现,每块单板支持128通道。通过背板设计,可以保证到达每块单板的100MHz高质量时钟的相位是同相的。这样,只要单板内的各通道延迟差能控制在200pS内,就可以实现该要求。XILINX采用上述解决方案,实现了该需求,且在实际的系统中满足了系统要求

0

0