今天讲的是四位二进制计数器74LS161,主要分为以下几个方面:

一、74LS161简介

二、74LS161引脚说明

三、74LS161使用方法

四、74LS161典型应用电路

五、总结

一、74LS161简介

74LS161芯片又叫同步四位二进制计数器,是常用TTL型的四位二进制可预置的同步加法计数器,可以灵活的运用在各种数字电路,以及单片机系统中实现分频器等很多重要的功能。

计数器:统计时钟脉冲的个数,也可用于分频、定时、产生节拍脉冲等。

图 1 74LS161实物图

二、74LS161引脚说明

图 2 74LS161引脚说明

【引脚1】CR——:控制74LS161的输入信号复位,低电平有效

【引脚2】CP:时钟脉冲输入端,上升沿有效

【引脚3\4\5\6】A\B\C\D:输入(预置)端,可预置任意一个4位二进制数

【引脚7】CTP:计数控制端,与CTT两脚同时为高电平时芯片计数;任意一脚为低电平时计数器保持原数据

【引脚8】GND:接地

【引脚9】LD——:控制74LS161的置数功能,低电平有效

【引脚10】CTT:计数控制端,与CTP两脚同时为高电平时芯片计数;任意一脚为低电平时计数器保持原数据

【引脚11\12\13\14】QD\QC\QB\QA:输出端数字信号

【引脚15】RCO:进位输出端(满16进一),高电平有效

【引脚16】VCC:电源正

三、74LS161使用方法

表 1 74LS161功能表

通过从功能表分析:

第一行:当CR——(低电平有效)为0时,此时无论其他引脚是什么,都是复位置零功能。也说明CR——不需要等CP的时钟信号,即异步清零。

第二行:当CR——为1,LD——为0时,在CP时钟信号为上升沿时刻,输出等于输入,即同步置数,相当于寄存器作用。

第三、四、五行:当CR——和LD——都为1(无效)、CTP和CTT中任意一个为0时,此时输出端保持原数据不变。

第六行:当CR——、LD——、CTP和CTT都为1时,为计数功能。当CP时钟信号上升沿来临时计数加一。

四、74LS161典型应用电路

(1)16位进制计数器

(2)任意进制计数器

任意进制的实现有两种方法:

1、反馈清零,即将数据输出端Q接上与非门后接回清零端CR——(图中为MR)。

例如实现12进制(0000~1011共12个状态)就将12+1(0000~1100共13个状态)的1(即Q3Q2端)与非后接回清零端CR——(低电平有效)。

那么,为什么要在需要的进制加1后再接回清零端CR——呢?前面我们说过74LS161有异步清零的性质,即当CR——为0时,CR——不需要等CP的时钟信号即可实现清零功能。

若使用1011做12进制,当Q3Q2Q0为1时经过与非后立即使CR——为0(有效),此时立即触发清零功能,1011这一状态不会被保存,当然也不会被算在计数里。所以要使用1011+1即1100。

图 3 反馈清零法实现12进制

2、反馈置数,即将数据输出端Q接上与非门后接回并行启用控制端LD——(图中为LOAD)。

因为使用了并行启用控制端LD——,所以我们也要用上数据输入端A0~A3(仿真图中为D0~D3),如果输入端什么都不接,就无法判断是多少进制。

例如12进制:

若A端给0000(0000~1011共12个状态),当Q端为1011时(Q3Q2Q0为1)经过与非后使LD——为0,此时还需再等一个CP时钟信号将A端的0000送到Q端,即同步置数(0000~1011共12个状态)。该接法下1011这一状态是稳定的。

若A端给0001,则Q端最终为1100。(0001~1100共12个状态);

若A端给0100,则Q端最终为1111。(0100~1111共12个状态);Ps:我们知道当Q端为1111时会产生进位,此时RCO端会为1。所以我们可以直接将RCO端接非门后接回并行启用控制端LD——。

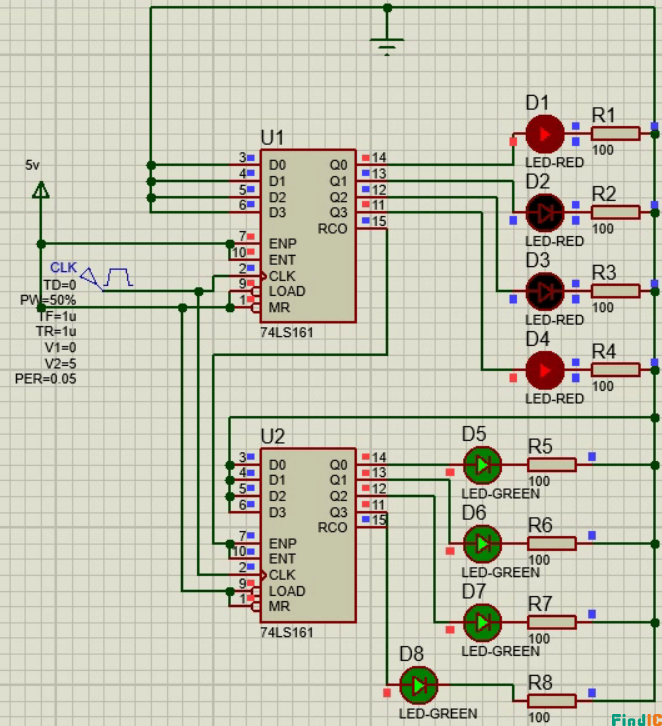

图 4 反馈置数法 A端给0100实现12进制

若需要的进制大于16,就需要多块74LS161来实现了。方法是将低位的进位端接入高位的CTP、CTT端(仿真图中为ENP和ENT)。芯片要共用CP时钟信号。这里放出32进制的仿真,若需要其他大于16进制的计数,参考上面反馈清零和反馈指置法。

图5 两块74LS161实现32进制

五、总结

总的来说,74LS161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器,两片74LS161可以组成32进制的计数器。

想了解更多关于74LS161的资料,可以点击:

0

0