MIPI的简单介绍

MIPI是Mobile Industry Processor Interface的缩写,按照标准描述,MIPI是MIPI联盟发起给移动应用处理器制定的一个开放标准。既然主要是面向移动应用处理器,那我们能看到的MIPI应用场合肯定多少都是移动应用处理器的应用场合,比如我们手机显示的传输就走MIPI协议,摄像头数据传输就走MIPI。

介绍了LCD显示屏的设计,里面讲了显示数据传输走RGB并行数据传输,至少用到31根信号线才能传输,31根数据线,想想在手机那么小的空间中肯定是没机会放下,加上现在手机分辨率那么高,用单端方式来传输信号,走线长的话,信号质量也是 个问题,所以最佳的方法是使用差分信号传输。但是对于常规显示屏,如果分辨率高,如1920x1080 60帧,常规使用LVDS方式传输都是2 Port LVDS,这样信号线就有20根,还是很多,显然使用常规显示LVDS方式也不适合,所以就针对性的把MIPI就提出来了,我们来看MIPI的各版本速率如下,下面的per lane表示一对差分信号。

|

Standard |

Version |

Adopted |

Data Rate(per lane) |

|

D-PHY |

1.0 |

Sep 2009 |

1.0 Gbit/s |

|

1.1 |

Dec 2011 |

1.5 Gbit/s | |

|

1.2 |

Sep 2014 |

2.5 Gbit/s | |

|

2.0 |

Mar 2016 |

4.5 Gbit/s | |

|

2.1 |

Apr 2017 |

4.5 Gbit/s | |

|

3.0 |

Sep 2021 |

9 Gbit/s |

可以看到,如果使用MIPI传输,对于刚才说的1920x1080走60帧,计算下来使用 V1.0 走4 Lane基本就可以进行完整传输,但对于使用常规2 Port LVDS的传输方式直接少了一半的信号线,所以对于移动设备来说是非常友好的,如果CPU支持更高版本的MIPI协议,那还可以使用更少的Lane。

MIPI信号构成和电路设计

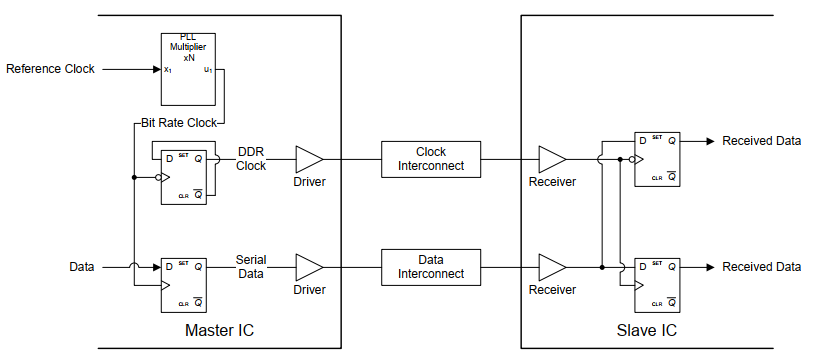

MIPI的信号线构成比较简单,主要由时钟+数据线构成,实现原理框架如下。时钟用于同步数据在接收端被接收,数据线就是刚才说的多Lane组成,无论在显示还是摄像头中,多数都是时钟+2 Lane、时钟+4 Lane这样的组合方式。

图1. MIPI实现原理框架

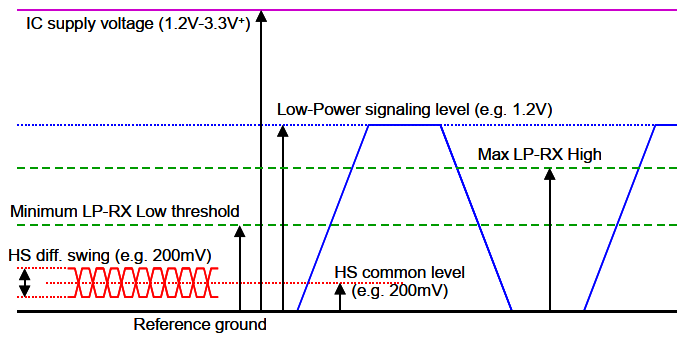

MIPI的信号线有HS模式和LP模式,HS模式时信号为差分信号,用来传输数据,LP模式时主要用来传命令或者状态表示,为单端信号,比较直观的信号表示如下。

图2. MIPI的信号电平

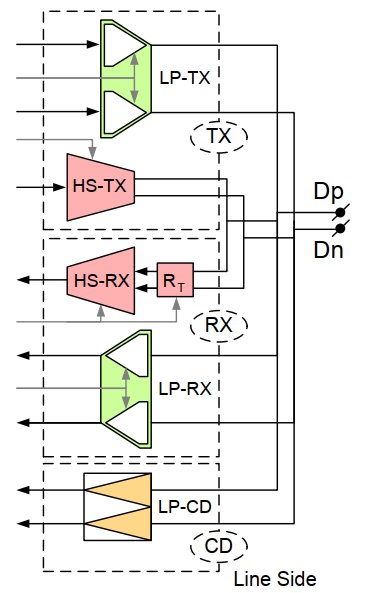

但不管分HS还是LP,集成芯片一般都把相关处理电路集成在芯片中,对外仅引出一对差分信号Dp和Dn,如下。

图3. MIPI HS和LP实现原理

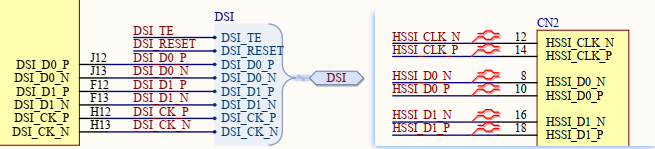

因为芯片已经把相关复杂处理电路集成起来,所以对于MIPI的电路设计也比较简单,设计中只需把主从端的信号一一连接起来即可,即时钟接时钟,Lane 0接Lane 0,以此类推,注意极性Dp对Dp,Dn对Dn。这里以上篇文章的STM32F7X为例,STM32F7X集成了MIPI DSI,最大支持30帧的720p分辨率显示输出,使用2 Lane数据线进行数据传输,摘取ST官方评估板的设计如下。

图4. STM32F7中的 MIPI电路设计

可以看到,电路设计时就是刚才说到一一把信号连接起来即可,Layout时注意差分阻抗管控100Ω±10%,差分对长度差约束最大值5mil,差分对之间约束最大长度差50mil。

0

0