半导体制造工艺流程通常分为三段,即前段(FEOL)、中段(MEOL)和后段(BEOL)。

前段(FEOL):一般有浅沟槽隔离(STI)模块,阱(Well)形成模块,以及器件(Device)模块等。

中段(MEOL):主要指接触孔(Contact)模块。

后段(BEOL):主要指金属互连线模块。

STI:Shallow Trench Isolation

浅沟槽隔离是指利用氧化硅填充沟槽,在器件有源区之间嵌入很厚的氧化物用于隔离不同的晶体管或器件,以防止它们之间的相互干扰。

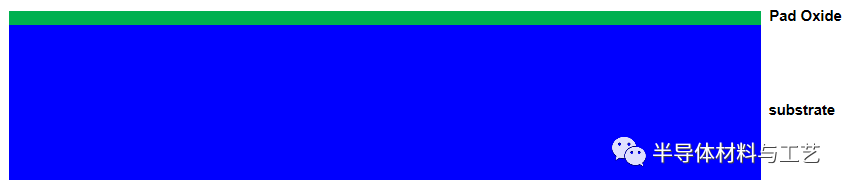

1.Pad Oxide Deposition

首先对晶圆表面进行清洗,主要是remove PA和native Ox.然后用炉管的方式长一层100A左右的Pad Oxide,其目的是为了缓解Si和后面Dep Nitride之间的应力。

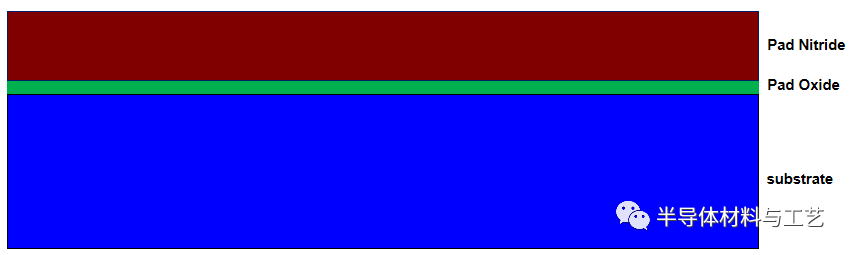

2.Pad Nitride Deposition

沉积氮化硅层大约1000A左右,起到硬掩模(Hard Mask)的作用,以及后面HARP CMP的停止层。

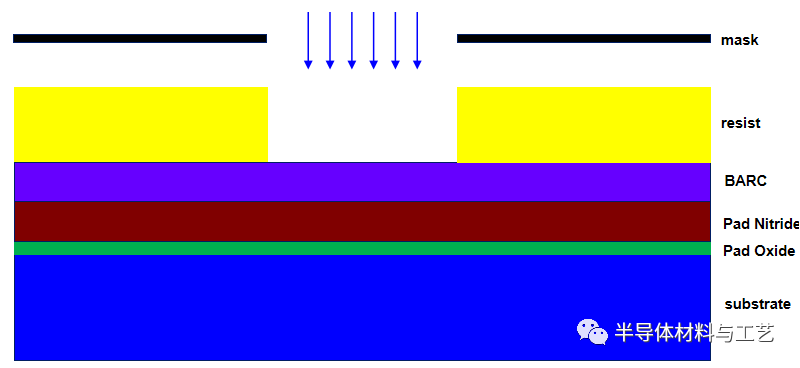

3.旋涂抗反射涂层(BARC)和光阻

曝光显影,定义出STI的区域。

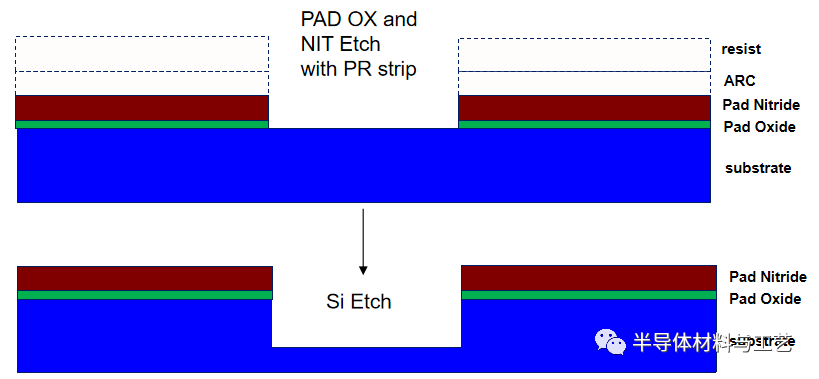

5.STI刻蚀

将光阻上的Pattern转移到氮化硅层和氧化硅层上并进一步往下刻蚀衬底,大概3000A左右。

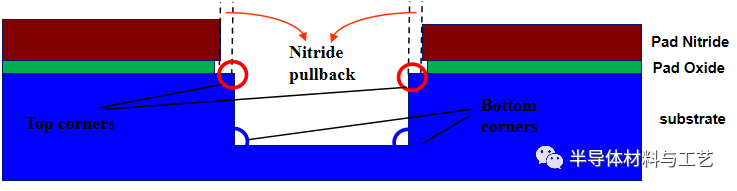

6.Nitride Pullback

这一步Nitride Pullback主要目的有:

1.Enlarge HARP gap-fill window.

2.Round sharp corner.

3.Improve STI divot.

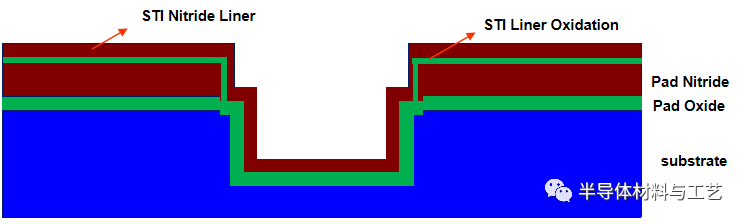

7.Liner Oxidation /Liner Nitride DEP

这里的Liner Ox主要作用

-

Corner rounding,

2.Trench Si surface damage relief。

Liner Nitride作用

1.Release oxide to Si stress

2.Reduce leakage

3.Improve STI divot

注:Liner Nitride这一层非必需层,主要是对应力比较敏感的器件需要加这一层。

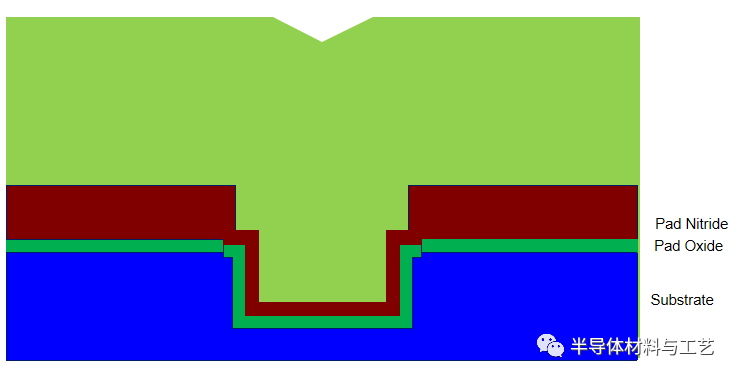

7.STI 填充

一般到65nm工艺时候,STI通常用HARP(High Aspect Ratio Process)工艺在浅沟槽内填充二氧化硅.像存储芯片常用SOD(Spin On Dielectrics)的方式填充STI,主要是应力和填充能力方面考虑。

8.蒸汽退火(Steam anneal ):消除二氧化硅层中的seam/void.

9.氮气退火(N2 anneal ):使二氧化硅层densification.

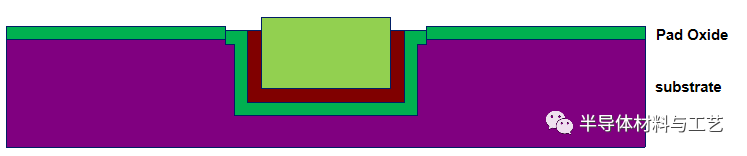

10.STI CMP(Chemical Mechanical Polishing)

STI CMP 停止在氮化硅层(Pad Nitride),一般都会Over polishing.

11.去除氮化硅层(Pad Nitride Remove)

使用热磷酸去除Pad Nitride,留下Pad Oxide作为后续IMP screen Oxide。(也有拔掉Pad Oxide,再长一层牺牲氧化层--Sacrifice Oxide)

有的工艺在去除氮化硅层(Pad Nitride Remove)前会加一道Oxide Etch 工艺,主要是通过HF去吃Ox,同时可以更好的control step height.

总结一下:前段STI 模块比较Care的点有:

1.STI ETCH→ CD,depth & SWA

2.SiN Pullback→divot issue

3.STI CMP→ Ox residue

4.STI SiN Remove→Step height control.

0

0