TSMC的Design Rule中,在Semiconductor Process的Front-End Features部分,可以看到STI这个词。那么什么是STI呢?STI全称Shallow trench isolation,浅槽隔离。

STI浅槽隔离作用是什么?Design Rule中提到,STI是Used for active isolation to reduce active pitch (OD pitch),也就说STI是用于隔离Active(如TSMC中是OD),以减小Active(OD)的Pitch。减少了OD的Pitch,从而可以提高器件的集成度。

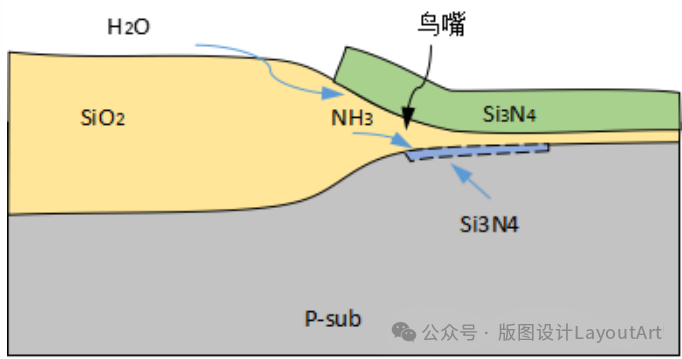

在早期的工艺中,主要采用LOCOS(Local Oxidation of Silicon 硅的局域氧化)隔离技术。LOCOS隔离是通过热氧化技术,在器件有源区之间嵌入很厚的氧化物,从而形成器件之间的隔离,这层厚厚的氧化物就是场氧[1]。而场区氧化层横向形成鸟嘴,会引起鸟嘴效应,如下图。

鸟嘴效应导致氧化层伸入有源区,减少器件有效宽度,降低器件速度。而且最先进的LOCOS隔离技术的最小隔离距离大概是0.6um,LOCOS鸟嘴效应导致氧化层向两边有源区伸入0.3um,所以最小的器件与器件的距离是1.2um,严重影响集成电路的集成度[1]。

为了提高器件集成度,新的隔离技术——STI浅槽隔离技术产生。在0.25μm及以下工艺中,STI浅槽隔离技术被广泛应用[1],已经代替了LOCOS隔离技术。

STI是采用浅沟槽结构,然后通过HDP CVD(High Density Plasma CVD)的方式沉积SiO2。再通过CMP平坦化技术对STI平坦化,去除多余的氧化层[1]。该隔离技术没有LOCOS的鸟嘴效应。比如TSMC 0.18um工艺中,有源区OD是Dark区域,通过刻蚀不是OD区域的硅衬底,保留器件的OD区域,在形成有源区OD的同时,也形成了STI的浅槽。STI在提高集成度的同时,可以有效隔离NMOS和PMOS,降低Latch up风险。因为STI隔离槽进入硅中的深度,比任何生长氧化层都要深,载流子必须在向下的弧区运动,才能到达相邻器件。载流子通路的增长,器件之间的相互作用减弱[2]。

STI也带来了一些坏处。STI沟槽中填充的氧化物与硅的热膨胀系数不同,在制造过程中,STI与硅的膨胀和收缩不同,STI导致的应力,改变MOS管的电气特性[3],这就是STI Stress Effect(STI应力效应),也称为LOD(Length of Diffusion)Effect(LOD效应)。

参考资料[1]《集成电路制造工艺与工程应用》温德通 著[2]《模拟电路版图的艺术》(第二版)Alan Hastings 著[3]《模拟CMOS集成电路设计》(第2版)毕查德•拉扎维 著

本文由JK_chenwen原创,微信号: JK_LayoutArt

文章中可能有些素材源于网络,若有侵权请读者提醒,作者会在第一时间进行更正。

2

2