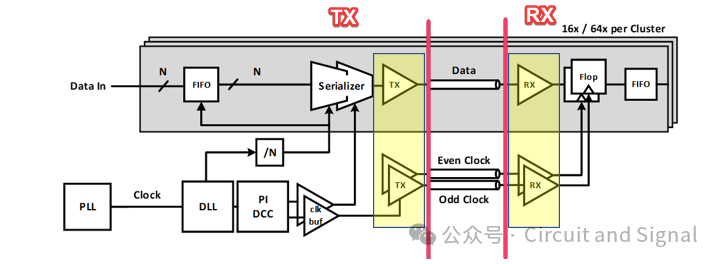

上一篇我们介绍了UCIe的基本概念(Chiplet Series(1): What is UCIe?),这一篇我们介绍和Tx有关内容,依然是物理层的说明。这是系统整体简易拓扑结构,包括TX, 通道和RX:

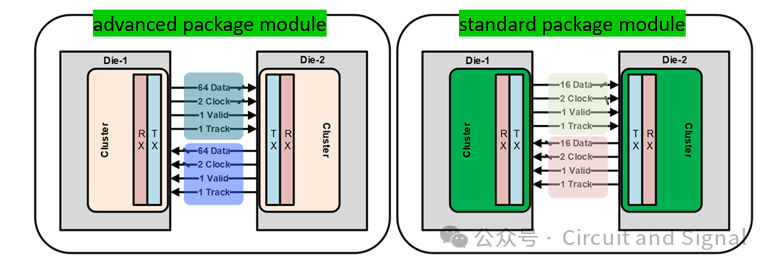

前面讲到先进封装单向最多有64根数据线,标准封装单向最多16根数据线,如下图所示:

但在实际应用中,先进封装的单向数据线有64+4=68根,多余的4根是冗余线,用于数据的修复等;标准封装则没有冗余备份数据线,这在前一篇已经介绍过。此外,可以看到TX端的源同步时钟包括锁相环(PLL),延迟锁相环(DLL),还包括相位控制的DCC,这些内容我们在时钟部分再详细介绍。

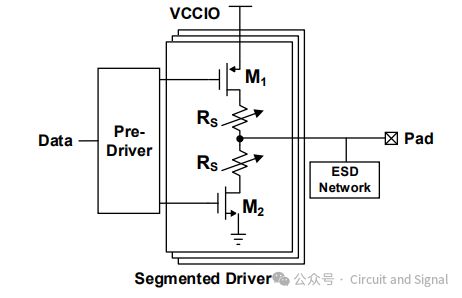

- Driver 结构

驱动器的结构如下图:

UCIe的Tx驱动具有以下特征:

- 典型的分段驱动器;

- 基于CMOS工艺实现;

- Tx的输出阻抗基于最佳眼图张开度,而不是匹配 T-Line 的阻抗进行设计;

- 带宽和上升/下降时间受Rterm 和 Cpad影响;

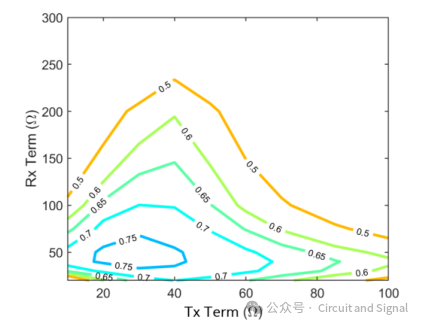

这里需要说明的是:UCIe的Tx端阻抗并不永远都要和channel的阻抗匹配,由于高密封装的影响,非50欧姆的Tx端口输出阻抗可能更合适,如下图所示:

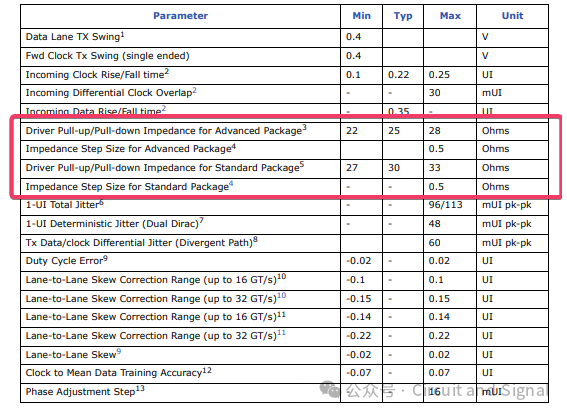

较低的Tx输出阻抗有利于更高的电压输入通道,进而增加RX端的电压摆幅和信号裕度;当然,TX端较大的阻抗不匹配将导致反射,所以这是一个折中选择。上图中显示,在特定情况下最佳的TX输出阻抗大约是30 Ω。对于较低数据速率和较短通道的情况,可以对端接进行调整,换取更大的信号裕度。下表是TX端的电气参数要求:

- Tx端均衡

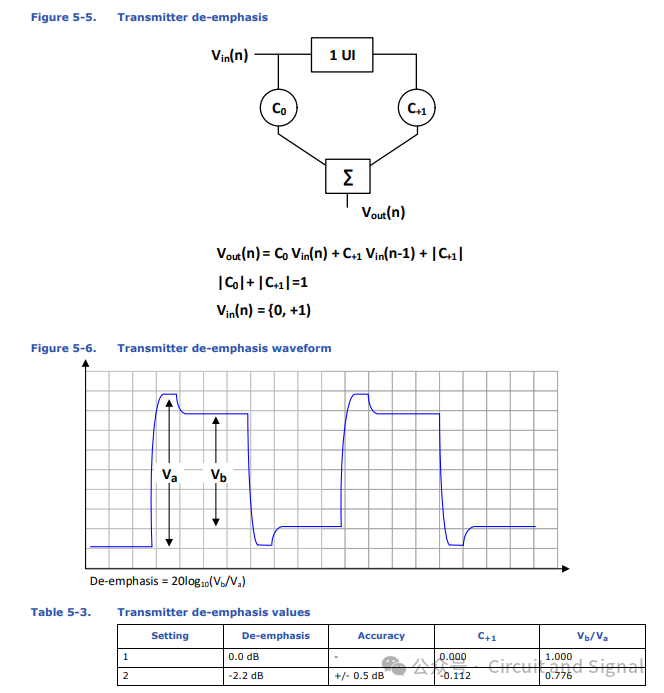

为了增强信号质量,UCIe的规范建议在Tx端使用1 tap的De-emphasis,如下图所示:

规范要求TX端的De-emphasis在24G/32的数据速率下必须要有,但1taps的能力有限,在具体电路实现上可能会有差别。以上就是Tx物理层主要特性的介绍,

0

0