因为数字电路,所以有大量的数字电路输出的“0”“1”翻转导致,需要大量的去耦电容。

图中开关Q的不同位置代表了输出的“0”“1”两种状态。

假定由于电路状态转换,开关Q接通RL低电平,负载电容对地放电,随着负载电容电压下降,它积累的电荷流向地,在接地回路上形成一个大的电流浪涌。

随着放电电流建立然后衰减,这一电流变化作用于接地引脚的电感LG,这样在芯片外的电路板“地”与芯片内的地之间,会形成一定的电压差,如图中VG。同样的对于电源端,每次信号翻转,都会引入了电压差。

当N多的翻转出现的时候,我们需要运用去耦电容,去耦电容可以防止这种噪声向外传播,所以我们放一些电容靠近器件的电源管脚。

由于去耦电容一般对电容器的精度没有很严格要求,选用时可根据设计值,选用相近容量或容量接近的电容器就可以。

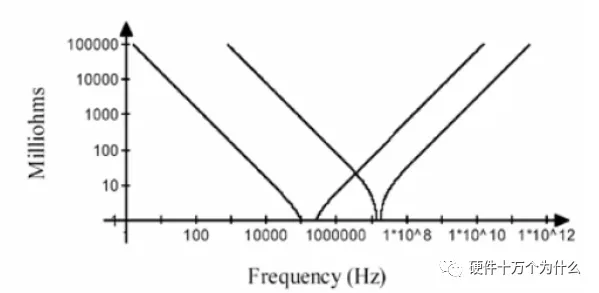

实际的电容存在寄生电感与等效串联电阻。由于单个电容的ESR、ESL相近,他们的阻抗特性也是相近的,单个电容与多个特性相同的电容并联阻抗特性图

容值不同的电容

所以在这个场景中,我们需要一种:

1、1nF~10uF容量,精度要求不高;

2、由于用量比较大(电源管脚比较多),成本比较低、相同容量情况下体积比较小的电容;

3、ESR、ESL比较小的电容。(需要去耦的信号频率比较高,并保证去耦效果)

多层片陶瓷电容(MLCC)就显得非常合适。

如下图所示:容值越小的去耦电容越靠近电源管脚放置!

容值小的电容,有最高的谐振频率,去耦半径小,因此放芯片近一点,容值大的电容,其谐振频率低,去耦半径大,可以稍远一点,电容的等级大致遵循10倍关系,以此在有效频段出现低阻抗通道。

电源系统的去耦设计的一个原则,就是在需要考虑的频率范围内,使整个电源分配系统的阻抗最低。

由于芯片特别是CPU、FPGA、DSP等,多IO、大功率芯片作为电路的核心,这些芯片的电源管脚也比较多,所以去耦电容的用量就比较大。

一般我们芯片由于速率越来越高,所以接口电平也就越来越低,导致我们的电路板上会有多种电压值的电源,早期数字电路电源以5V、3.3V为主,现在数字电路电源越来越丰富:2.5V、1.8V、1.5V、1.1V、1.0V、0.9V,可调可控电源等等。所以这些开关电源的输入电容和输出电容也需要大量使用。

在 PCB 布局设计中,去耦电容(decoupling capacitors)的放置要求非常讲究,尤其是容值较小的去耦电容需要靠近用电器件(如芯片、IC等)。这是基于以下几个重要的原因:

1. 去耦电容的作用和频率特性:

去耦电容的主要作用是滤除电源电压中的高频噪声或脉动信号,提供平稳的电压给敏感的用电器件。电容的作用与频率密切相关:

-

容值越小的电容,频率响应越高:容值小的电容在高频下表现更好。它能够快速响应高频噪声,因为它具有较低的阻抗(Z = 1/(2πfC)),能在高频信号上起到更好的去耦作用。

由于高频信号的波长很短,因此小电容需要在尽可能短的距离内提供去耦作用,否则信号会在电路中传播较远,导致去耦电容的效果降低。

2. 电流路径和寄生效应:

-

小电容的 ESR 和 ESL 影响较大:小容值电容的等效串联电阻(ESR)和等效串联电感(ESL)相对较大,特别是在高频时,这些寄生效应对去耦效果有较大影响。如果电容离用电器件较远,信号通过PCB的寄生电阻和电感时,电容的去耦效果会受到衰减,尤其是在高频区域。

-

信号的传输延迟和电流路径:电流需要通过PCB的导线、接地平面等,才能到达电容。如果电容离用电器件太远,信号传输路径就会增加,导致电流路径中的噪声更加严重,电容就难以有效地滤除噪声。更小的电容尤其需要短的路径,以便快速响应高频噪声。

3. 寄生电感和电流传递速度:

-

小电容器由于容值小,其带宽较宽,因此在高频下需要更低的电感来保证有效去耦。如果电容太远,PCB导线的电感会抵消电容器的去耦效果,导致去耦作用大大减弱。

-

电流在电路板上通过导线的传播速度有限,因此容值较小的电容需要直接、快速地与用电器件连接,以减少信号衰减和延迟。

4. 短路径能减小噪声:

-

在高速电路中,信号的快速变化容易产生电磁干扰(EMI)或噪声。为了减少这种噪声,去耦电容需要尽可能地靠近用电器件,提供低阻抗的电流路径,确保电源的电压稳定,避免产生高频噪声。

容值小的电容可以更有效地应对这些快速的电压波动,离用电器件更近有助于更快响应和消除干扰。

总结:

容值小的去耦电容需要靠近用电器件的原因,归结于电容器的工作频率特性、寄生效应、电流路径和噪声传输等因素。在高频应用中,电容与用电器件之间的距离越近,去耦效果越好。容值小的电容器需要减少电流路径中的寄生电感和电阻,才能高效地去除电源噪声,保证系统的稳定运行。

0

0