以太网链路

以太网链路包含MAC控制器、PHY芯片、网络变压器和RJ45接头组成,有的系统会有DMA控制。一般的系统中CPU和MAC以及DMA控制器都是集成在一块芯片上的,为了节省空间简化设计,很多时候网口的变压器和RJ45的接头集成在一起。

什么是以太网PHY

PHY是物理接口收发器,IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。

什么是以太网MAC

MAC就是媒体接入控制器。以太网MAC由IEEE-802.3以太网标准定义。它实现了一个数据链路层。最新的MAC同时支持10/100/1000Mbps速率。通常情况下,它实现MII/GMII/RGMII接口,来同行业标准PHY器件实现接口。

常见以太网PHY-MAC接口的模式有哪些?

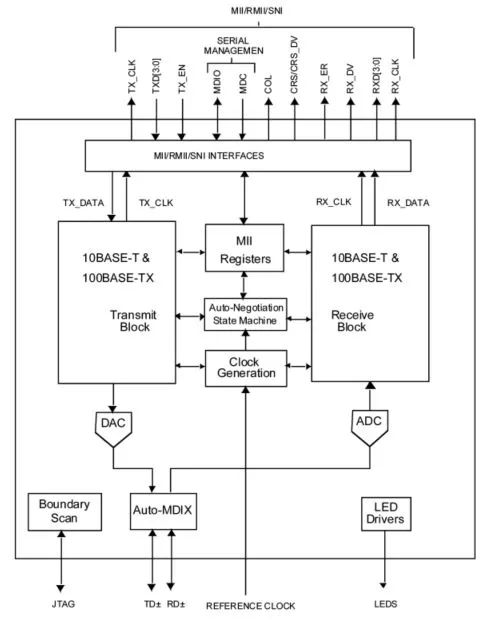

芯片内部包括MII/RMII/SNI 接口、发送模块、接收模块、MII寄存器、自动协商机制、时钟发生器、ADC、DAC、(Auto-MDIX)自动交叉线等模块,具体如下图所示:

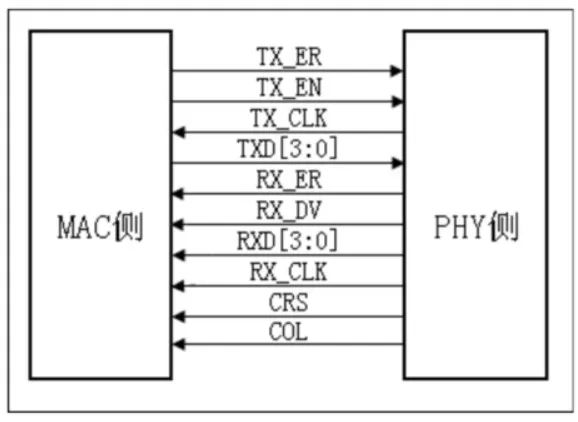

MII(Medium Independent Interface)即媒体独立接口。它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。

在IEEE802.3中规定的MII总线是一种用于将不同类型的PHY与相同网络控制器(MAC)相连接的通用总线。网络控制器可以用同样的硬件接口与任何PHY 。

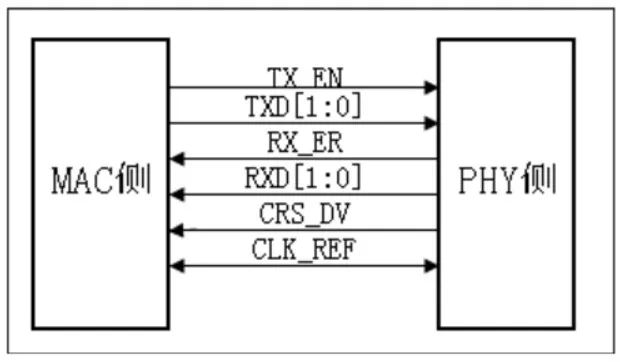

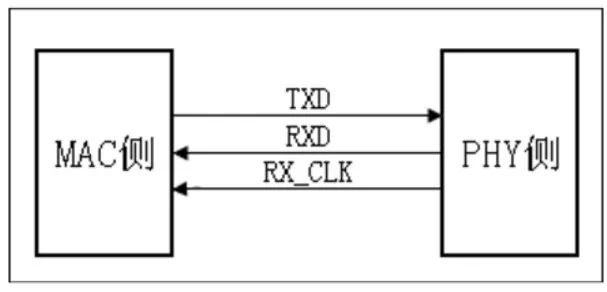

RMII:MAC和PHY芯片之间的接线图,数据线相比MII减半,时钟为50MHZ,还是需要注意TX_CLK是由phy芯片发出,如果是需要自适应10/100M。

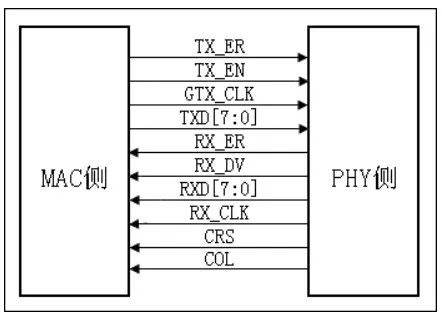

GMII:对应为千兆网;要实现1000Mb/s、100Mb/S、10Mb/S自适应必须加上TX_CLK(PHY输出)。

MII口是用4根线来传输数据的,RMII口是用2根线来传输数据的,GMII是用8根线来传输数据的,GMII和RMII都是并行传输并需要随路时钟。

SGMII(Serial Gigabit Media Independent Interface)

SGMII是PHY与MAC之间的接口,类似与GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟。另外SGMII是有8B/10b编码的,速率是1.25G。

0

0