本文将主要讨论SGM6132降压开关电源PCB布板时的相关注意事项,这部分内容在datasheet里面是一点也没有涉及的;觉得有点奇怪呢,因为布板对于开关电源性能影响也是比较显著的。当然,像这种简单的DCDC,对性能要求不高时,怎么布板都是可以干活的,只是会有风险吧。糟糕的布板,通常会伴随这样的问题:芯片的SW引脚的震荡电压可能超过它的额定最大值导致芯片损坏,糟糕的EMI特性,输出电压精度差,效率差,散热差等等。

其实布板很简单,依据的原理不复杂,但是它对于产品的可靠性来说是非常重要的;印制电路板PCB是可以理解为产品上面的一个关键元器件的,它对电路应当是尽量透明的。所以花些时间再整理下布板注意事项也是挺值得的。

首先,我们看下布板需要注意的几点吧,这是在TI电源工程师培训中学到的,特别容易记住。布板时需特别注意的的就是“关键路径”和“关键节点”。另外,为了缩短篇幅,所以公式原理等就不再这里展开了,文末会列出我看过的非常好的相关文档,里面都有详细推导和数例,这里不再重复。

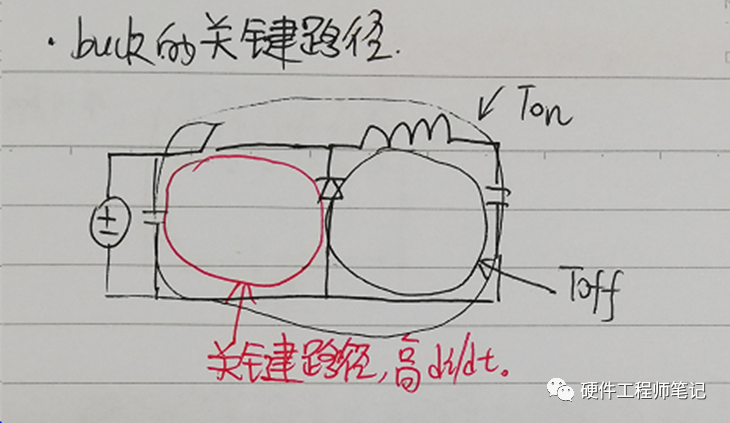

关键路径,即高di/dt回路,这条回路上的电流是断续的脉冲电流。所以这条回路需要尽量短,包围面积尽量小;高频开关频率建议底层铺一层完整的地层(注:一定要比关键路径面积大很多才管用。它的原理跟共模电感滤除共模噪声类似,共模电流产生的磁力线抵消,因此自感大幅度减小;这个我是测过的,sw引脚下面铺铜对于减小自感效果非常明显)。无论是缩小关键路径面积甚至底层铺一片大地,都是为了减小自感L,V=L*di/dt,这就是为什么需要减小L的缘故了;否则自感产生的感应电动势如果超过芯片额定最大值就会损害芯片了。关键路径跟拓扑有关,不同拓扑的关键路径都是不一样的。图1为buck的关键路径,其他拓扑的关键路径识别方法是一样的。

图1

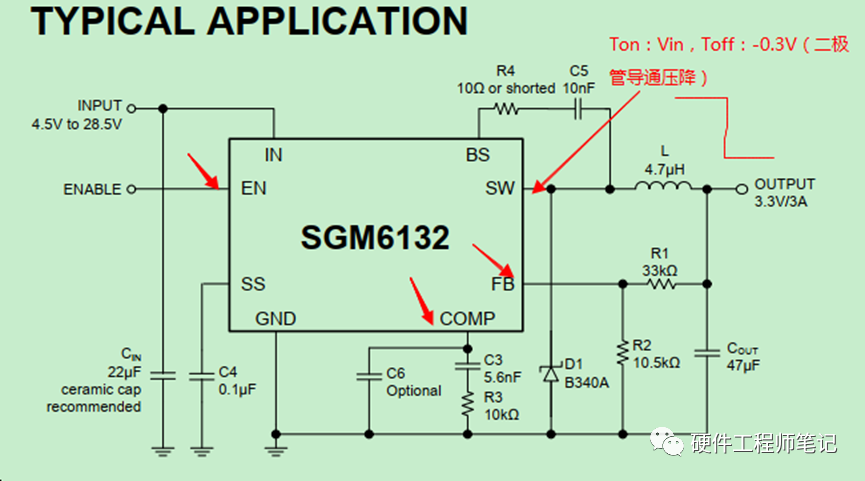

关键节点,即干扰节点高dv/dt节点,和易受干扰的节点如高阻抗节点等。图2为 SGM6132的关键节点。所以如果板卡上有多个分布电源时,需要注意下彼此不能干扰。以及高dv/dt节点的铺铜面积不要太大,减小干扰源,实际上除了GND的铺铜面积可以非常大,其他网络的铺铜面积都不能无节制的大的,如Vin、Vout铜面积不能太大,以免拾取噪声(V=C*dv/dt)。

图2

小信号地和功率地分开,在电源芯片的GND引脚上单点接在一起,可保证设置的输出电压精度。当然还有很多注意事项,不过这三点是最基础的了。

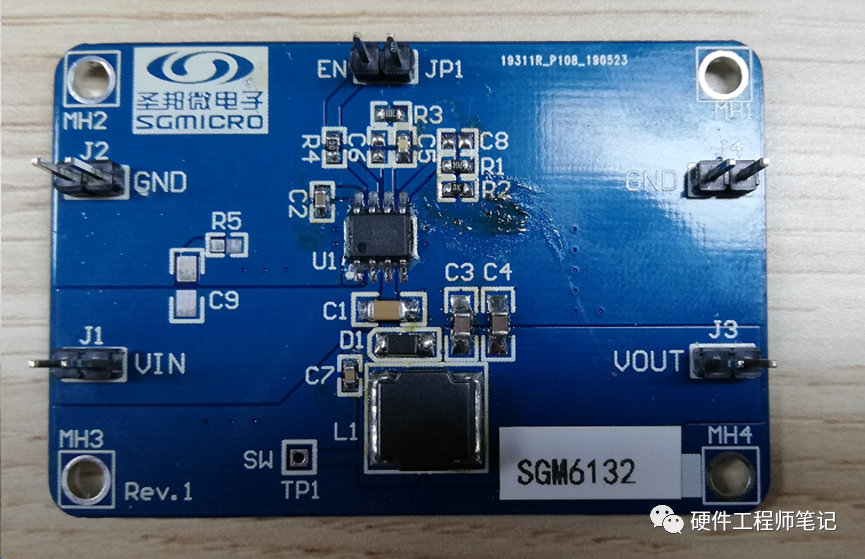

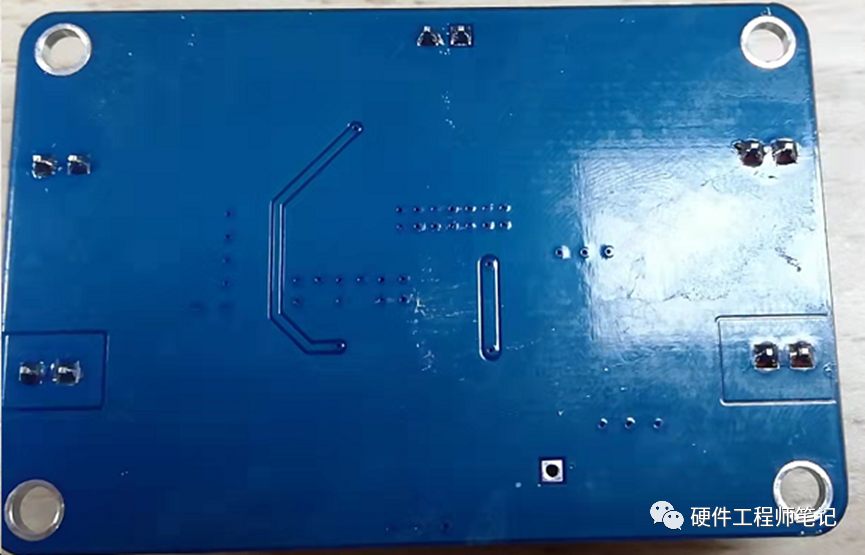

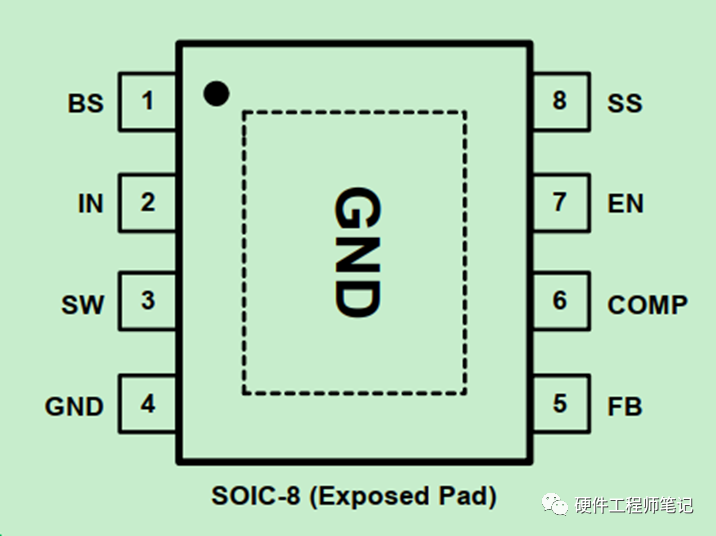

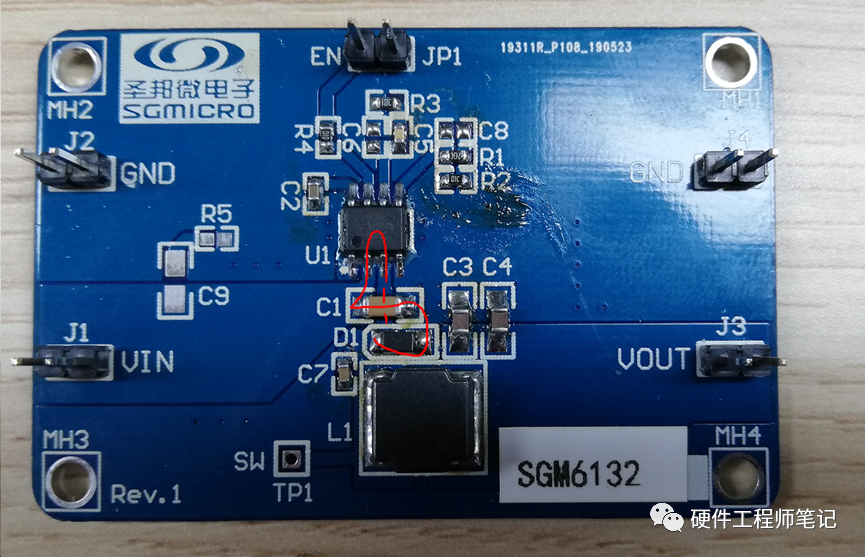

知道了上面这三点后,我们就可以布板了。实际上这三点也是非常容易记忆的,很多相关文档特别长,可能看完我们都不知道哪些是重点了。下面先看看圣邦微EVM(两层板)的布板吧,见图3和图4,图5是它的引脚分布。

图3

图4

图5

我们先看下圣邦微的EVM是怎么处理关键路径的,见图6,从图4中可看到,关键路径下面都是铺地处理的。

图6

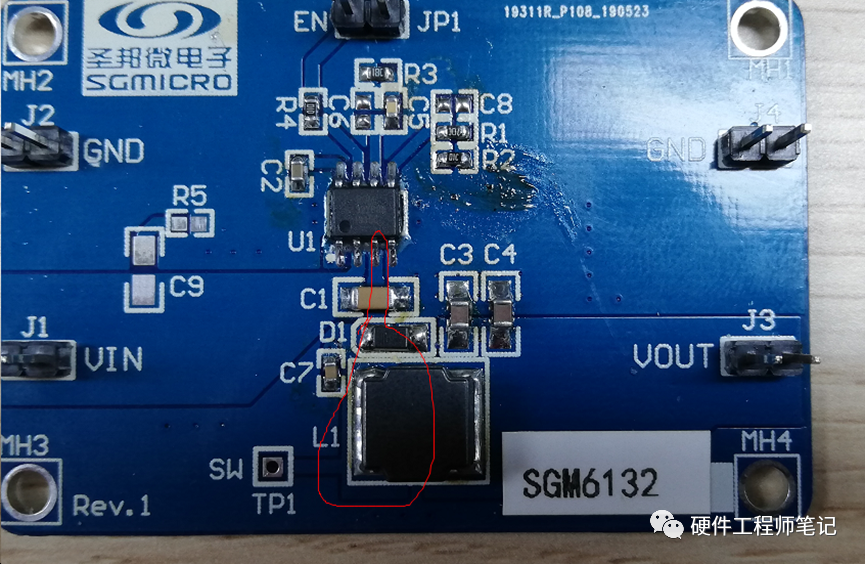

关键节点高dv/dt节点,他们铺铜面积也不是很大的,参加图8

图8

图8中的R1、R2是设置输出电压的分压电压,R2是下面的电阻,一端接地。他们把小信号地和功率地全部铺在一起了,没有做分开处理。不过我测试评估板的输出电压调整率时发现精度还是很高的,可能他们有别的考虑吧。

R1其中一端是接到Vout节点采集输出电压,同样的,他们也是打过孔(这条线左右和上面都是地,这就是所谓的包地处理吧)而后接到了经过C3、C4滤波后的输出电压;因为滤波后的输出电压是稳定的电压。

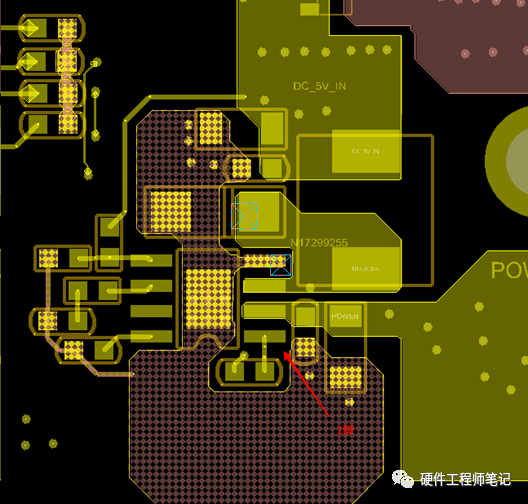

然后再看下我的布局吧,我的布局没有跟圣邦微的EVM一样,因为布局时候,他们的评估板还没到呢。参见图9。不过,基本需注意的点也都考虑到了,中间裸露的焊盘也是打孔到地层的,目的是为了散热,这里没有显示出来。

图9

以上就是关于布板内容的全部了,完成了糟糕的布板会有哪些风险,“关键路径”和“关键节点”的初步讨论,以及基于SGM6132的布板实例(参考他们的评估板)。

主要参考资料:

非隔离式开关电源的布局考虑

ADI电源大师课-中级布板相关内容

精通开关电源-布板一节

电源工程师培训初级-boost一节

电源设计基础(TI电源书籍,最后一节)

运算放大器权威指南布板相关章节

0

0