对学电子的人来说,在电路板上设置测试点(test point)是在自然不过的事了,可是对学机械的人来说,测试点是什么?

基本上设置测试点的目的是为了测试电路板上的零组件有没有符合规格以及焊性,比如说想检查一颗电路板上的电阻有没有问题,最简单的方法就是拿万用电表量测其两头就可以知道了。

可是在大批量生产的工厂里没有办法让你用电表慢慢去量测每一片板子上的每一颗电阻、电容、电感、甚至是IC的电路是否正确,所以就有了所谓的ICT(In-Circuit-Test)自动化测试机台的出现,它使用多根探针(一般称之为「针床(Bed-Of-Nails)」治具)同时接触板子上所有需要被量测的零件线路,然后经由程控以序列为主, 并列为辅的方式循序量测这些电子零件的特性,通常这样测试一般板子的所有零件只需要1~2分钟左右的时间可以完成,视电路板上的零件多寡而定,零件越多时间越长。

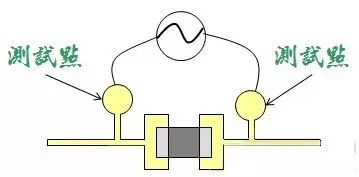

但是如果让这些探针直接接触到板子上面的电子零件或是其焊脚,很有可能会压毁一些电子零件,反而适得其反,所以聪明的工程师就发明了「测试点」,在零件的两端额外引出一对圆形的小点,上面没有防焊(mask),可以让测试用的探针接触到这些小点,而不用直接接触到那些被量测的电子零件。

早期在电路板上面还都是传统插件(DIP)的年代,的确会拿零件的焊脚来当作测试点来用,因为传统零件的焊脚够强壮,不怕针扎,可是经常会有探针接触不良的误判情形发生,因为一般的电子零件经过波峰焊(wave soldering)或是SMT吃锡之后,在其焊锡的表面通常都会形成一层锡膏助焊剂的残留薄膜,这层薄膜的阻抗非常高, 常常会造成探针的接触不良,所以当时经常可见产线的测试作业员,经常拿着空气喷枪拼命的吹,或是拿酒精擦拭这些需要测试的地方。

其实经过波峰焊的测试点也会有探针接触不良的问题。 后来SMT盛行之后,测试误判的情形就得到了很大的改善,测试点的应用也被大大地赋予重任,因为SMT的零件通常很脆弱,无法承受测试探针的直接接触压力,使用测试点就可以不用让探针直接接触到零件及其焊脚,不但保护零件不受伤害,也间接大大地提升测试的可靠度,因为误判的情形变少了。

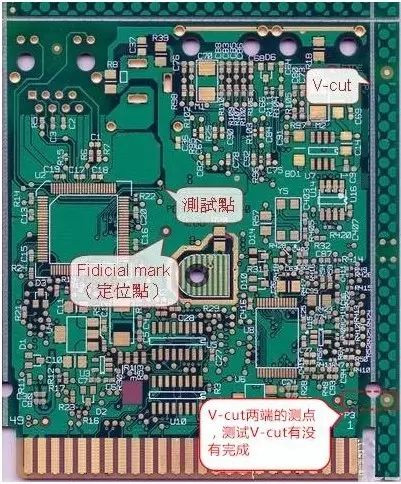

不过随着科技的演进,电路板的尺寸也越来越小,小小地电路板上面光要挤下这么多的电子零件都已经有些吃力了,所以测试点占用电路板空间的问题,经常在设计端与制造端之间拔河,不过这个议题等以后有机会再来谈。测试点的外观通常是圆形,因为探针也是圆形,比较好生产,也比较容易让相邻探针靠得近一点,这样才可以增加针床的植针密度。

1. 使用针床来做电路测试会有一些机构上的先天上限制,比如说:探针的最小直径有一定极限,太小直径的针容易折断毁损。

2. 针间距离也有一定限制,因为每一根针都要从一个孔出来,而且每根针的后端都还要再焊接一条扁平电缆,如果相邻的孔太小,除了针与针之间会有接触短路的问题,扁平电缆的干涉也是一大问题。

3. 某些高零件的旁边无法植针。 如果探针距离高零件太近就会有碰撞高零件造成损伤的风险,另外因为零件较高,通常还要在测试治具针床座上开孔避开,也间接造成无法植针。电路板上越来越难容纳的下所有零件的测试点。

4. 由于板子越来越小,测试点多寡的存废屡屡被拿出来讨论,现在已经有了一些减少测试点的方法出现,如 Net test、Test Jet、Boundary Scan、JTAG.。 等;也有其它的测试方法想要取代原本的针床测试,如AOI、X-Ray,但目前每个测试似乎都还无法100%取代ICT。

关于ICT的植针能力应该要询问配合的治具厂商,也就是测试点的最小直径及相邻测试点的最小距离,通常多会有一个希望的最小值与能力可以达成的最小值,但有规模的厂商会要求最小测试点与最小测试点间距离不可以超过多少点,否则治具还容易毁损。

0

0