在电源电路的设计中热设计是重要的,是和 PCB 设计同样重要的要素。设计完成以后发生了问题将花费很多时间和成本进行整改。因此,在 PCB 设计的初级阶段开始做好热设计的准备是必要的。在这篇应用笔记中,记载了 PCB 设计时降低热阻的关键点。

从现在开始改变 PCB 的关键参数,查看热阻的变化。以 JEDEC STANDARD JESD51 作为基准,记载了 1 层、2 层、4 层各个 实测热阻值。然后,确认上述实测值和仿真值的一致性,记载不符合 JEDEC 基准的 PCB 热阻的仿真值。

PCB 材料、布局、器件放置、封装形状、周围环境的影响热阻 值的变化,导致测量值与真实值不一致。因此,不要看数值的 绝对值,请参考热阻值的变化趋势。

铜箔面积

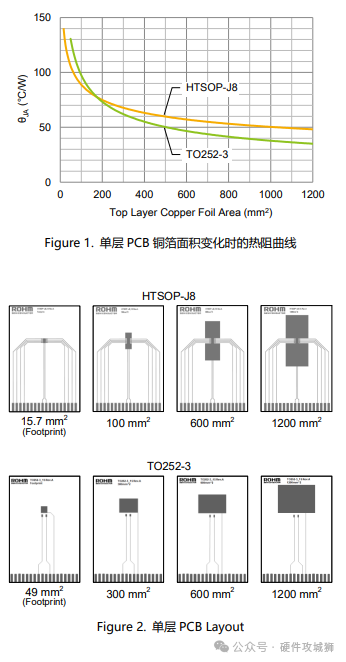

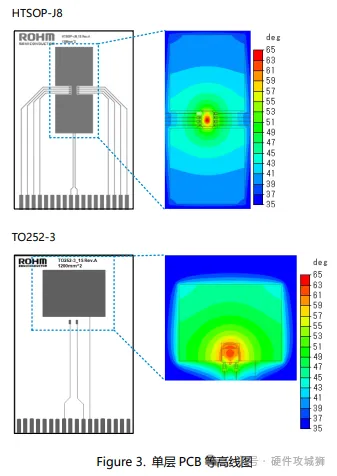

Figure 1 是单层 PCB 铜箔面积变化时的热阻曲线。如同 Figure 2 一样通过 PCB 布局改变铜箔的面积。随着散热 用的铜箔面积增大、热阻值降低。铜箔面积达到某种程度即使 再增大,也不能获得与面积相应的散热效果。Figure 3 是等高 线图,可以看出随着与热源距离的增加,相同温度区域增加, 散热效果降低。

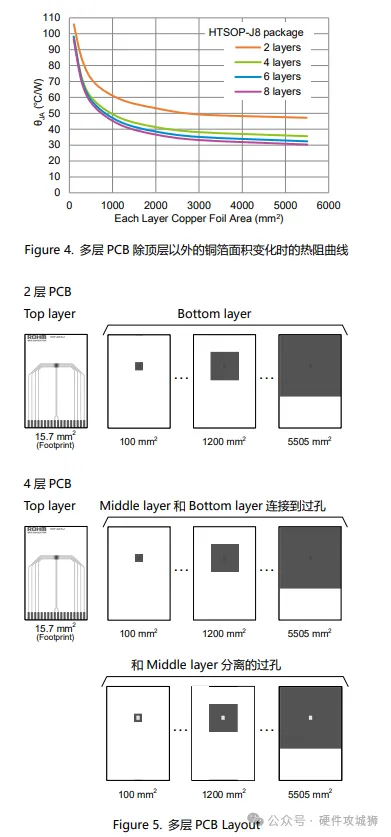

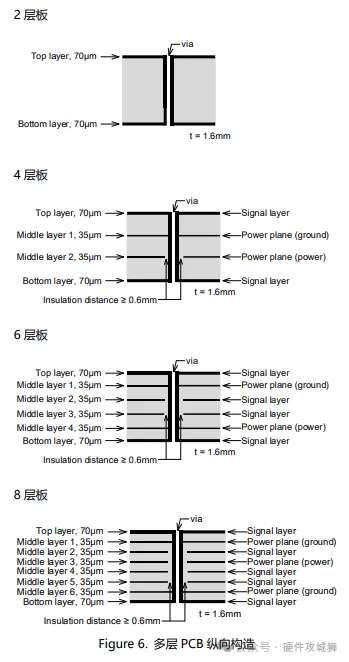

接着,我们来看一看多层板热阻的变化。Figure 4 是改变铜箔 面积时的热阻曲线。Figure 5 作为 Layout 代表的例子,展示 的 2 层板和 4 层板。6 层板和 8 层板以 4 层板作为标准。纵向 构造如 Figure 6 所示。通过散热孔把 PCB 从 Top layer 到 Bottom layer 贯通。中间层和散热孔是否连接取决于层数,因 此请参阅每个图。

多层板的热阻变化和单层板相同、随着散热用的铜箔面积的增 大,热阻降低。可是增大到某种程度以上,也不能获得和面积 相应的效果。

2 层板和 4 层板之间的热阻差异很大。由于过孔是纵向结构 (Figure 6),相对于 2 层板从热源开始通过 1.6mm 的过孔向 Bottom layer 传输热量,4 层板从热源开始,通过短距离的过 孔向 Middle layer 1 传输大量的热量。总之,从热源开始到最 近的散热铜箔之间,距离近的过孔的长度变短,热阻变低。由 于 6 层板和 8 层板的距离更短,热阻也相应的更低。

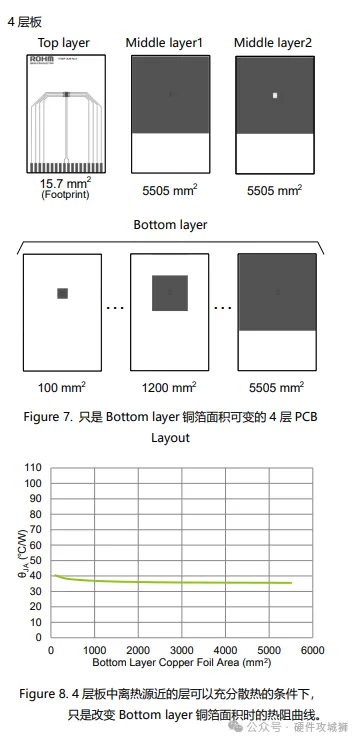

那么,让我们看一看热源向最近的散热铜箔传递大量热量的情 况。如图 Figure 7、用 4 层板,Middle layer 1 和 2 只进行 5505mm2 的大面积铜箔 Layout。但是、Middle layer 2 没有 和过孔连接。在这种情况下,改变 Bottom layer 铜箔面积时热 阻的变化如 Figure 8 所示。这样、可以判断离热源近的层能充 分散热、离热源远的层即使确保铜箔面积散热效果也是不明显的。

综上所述,通过优先增加靠近热源层的铜箔面积,可以有效降低热阻。

板厚 Figure 9 是 1 层板、改变板厚时的热阻曲线(PCB 参考 Figure 2)。纵轴是以板厚为 1.6mm 时的热阻作为基准(0)表示变化率。板子越厚,热阻就越低。单层板即使纵向热传导,因为下面是 传导率小的空气,导致散热困难,所以横向热传导占优势。板 子厚度变厚,横向的热阻抗变低。

Figure 10 是改变板厚时的热传导状态、可以看出板子越厚、热量传导越远。

在 Figure 9 中增大 Top layer 的铜箔面积时、相对于板厚热阻的变化变小。这是因为随着铜箔面积的增加,铜箔的热传导优势会增加,板厚对热阻的影响比率减小。

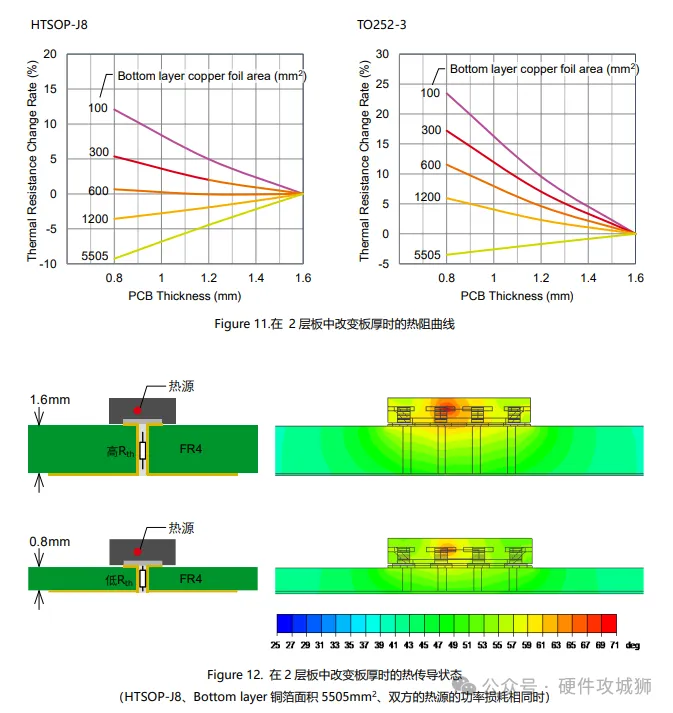

Figure 11 是在 2 层板经过散热孔向 Bottom layer 铜箔连接的 Layout 中,改变板厚时的热阻曲线(参考 Figure 5 和 6 的 PCB)。纵轴是以板厚为 1.6mm 时的热阻作为基准表示变化率。铜箔面积小的场合,和单层板一样:为了面向基板的热传导率 高,基板的厚度越厚,越来越倾向于热阻变低。随着铜箔面积增大,因为经过过孔向铜箔的热传导比率增加, 过孔的长度变短(过孔的热阻变低)。总之基板的厚度越薄,热阻越低。铜箔面积小横向热传导有优势,铜箔面积大纵向热传导有优势。这个界限是根据 PCB 的条件变化的。

在 Figure 12 表示基板厚度变化时的热传导的状态、在 Bottom layer 有充分散热用铜箔的条件下,可以判断厚度薄的基板能纵 向高效地进行热传导。

层数

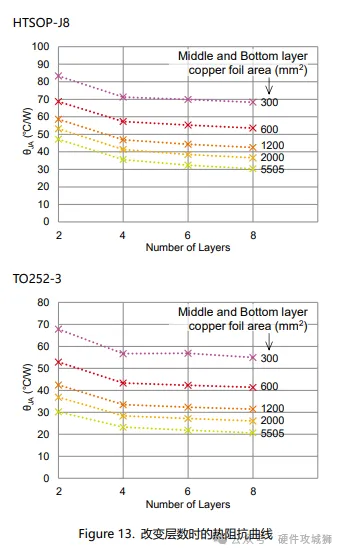

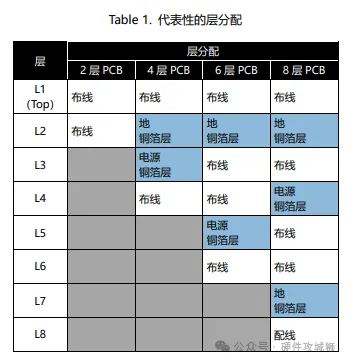

Figure 13 是改变层数时的热阻抗曲线(参考 Figure 5 和 6 的 PCB)。随着层数的增加热阻越来越低。这是因为可以导热的铜 箔面积增加了,在“铜箔面积”一项中有说明。从纵向结构 (Figure 6)来看,在板厚相同的情况下,层数越增加,热源到最 近的内层铜箔(平面)的距离越近,热阻越低。代表性的层分配如 Table 1 所示。一般情况下从 EMI 的观点出 发,与所有的布线层相邻放置的是低电阻的铜箔层(地或者电 源)。这样的放置在热设计中也是非常有效、Top layer(在这里 是 L1)的热源能垂直向内层平面 L2 高效地进行热传导。

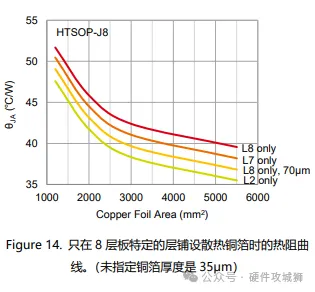

例如使用 8 层板、Top layer 的热源没有通过过孔向内层连接。由于纵向过孔的热阻增加,即使在 Bottom layer(这里是 L8) 配置大面积的铜箔、不能说是最合适的热传导。在这样的条件 下,增加 Bottom layer 的铜箔厚度,使其达到某种程度能降低 热阻。在多层基板中,在和热源相同的层或者相邻的层铺设大面积的 散热用的铜箔,能有效降低热阻。Figure 14 是只在 8 层板特定的层铺设散热铜箔时的热阻曲线。

可以判断随着远离 L1 热源热阻逐渐增大。

铜箔厚度

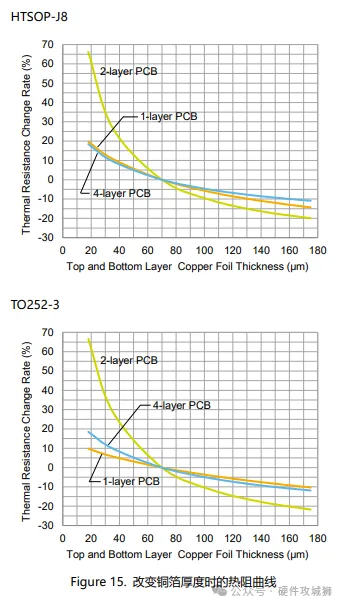

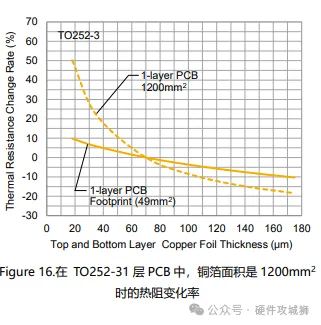

Figure 15 是改变铜箔厚度时热阻的变化曲线。铜箔厚度越厚, 热阻越低。这是因为作为热传导的路径铜箔本身的热阻很低。在曲线图中,以铜箔厚度为 70um 时的热阻作为基准表示热阻 的变化率。使 Top layer 和 Bottom layer 的铜箔厚度变化, Middle layer 固定在 35μm。根据 PCB 的层数的不同、热阻的 变化率不同。这是因为铜箔面积等 PCB 的构成不同,所以请作 为一个例子来看。这个曲线图的 PCB Layout 是 Figure2、5、6,Top layer 的铜 箔面积只是 Footprint,Middle layer 和 Bottom layer 分别是 5505mm2。由于 1 层 PCB 的铜箔面积只在 Footprint 部分,可以看到铜箔 厚度的影响很小。在 Figure 16 中,表示将铜箔面积扩大到 1200mm2 时的结果。可以看出,向铜箔的热传导增强了,铜箔 厚度的影响比率变大。2 层 PCB 的热阻变化率变大了,这主要时因为热传导路径是 Bottom layer 的铜箔,铜箔厚度的影响比率变大了。由于 4 层 PCB 向 Middle layer 传输很多的热量,Bottom layer 的铜箔厚度的影响比率比较小。

无论如何、铜箔的厚度越厚,热阻越低。

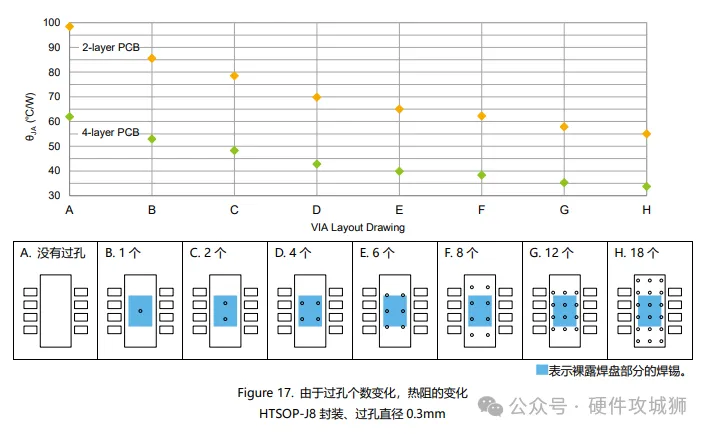

散热过孔

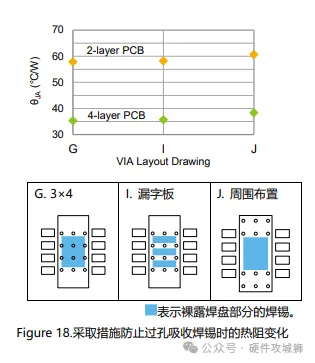

Figure 17 表示在安装了 HTSOP-J8 封装的 PCB 中,根据散热 过孔个数的不同,热阻的变化。过孔的个数越多,热阻越低。可以看出,仅仅一个过孔、散热效果也很明显。如果在裸露焊盘的正下方放置过孔,可能会在回流焊工序中吸 走焊料,并且降低融合率。为了回避这问题,设计了避开过孔 的漏字板(网板),或者在周围布置过孔的方法避开裸露焊盘。Figure 18 表示了各种方法的热阻变化。漏字板的方式(I)热阻 稍稍变差。可是向周围布置过孔的方式(J),热量一旦经过铜箔 传递到过孔,使铜箔的热阻被增加。因此,随着散热过孔的效 果与热源的距离增加而变小,尽可能放置过孔在热源的正下方。

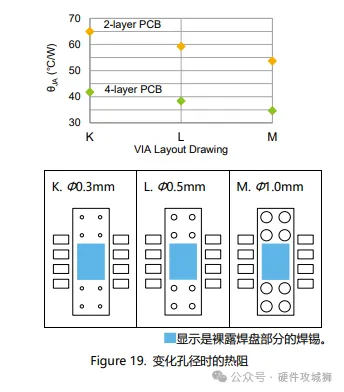

Figure 19 显示的是变化孔径时的热阻。孔径越大热阻越。这是 因为作为热传导路径的孔本身的热阻降低。在这个例子中,为了看孔径的影响全部在同一位置配置孔。实际 上,由于孔径越小能在较窄 pitch 上配置,所以 0.3mm、0.5mm 的热阻比这个例子低。Layout K (0.3mm)相当于前一页的 Layout J。当将孔配置在裸露焊盘或 FIN 正下方焊锡部分的情况下,为了 防止焊锡吸入推荐 0.3mm 以下的尺寸。

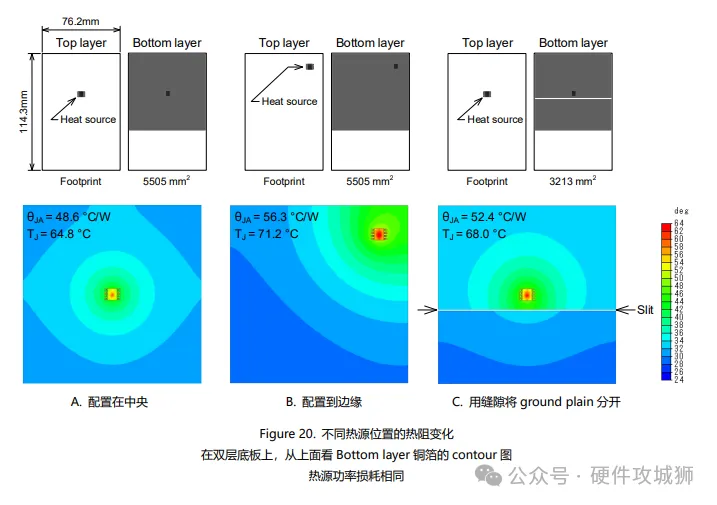

热源的位置

Figure 20 是根据基板上热源位置的不同热阻的变化。A 将热 源配置在基板的中央,因为是向全方向热传导,所以热阻最低。B 在基板边缘配置的状态下,由于能够热传导的体积变少,热 阻变高。C 是作为主要热传导目的地的铜箔表面被狭缝分割的 情况。为了防止电磁干扰和噪声,可以考虑在 ground plain 上开一条缝,将按功能分区分开。这种情况下主要导热处的铜箔 面积虽然减少了,但是因为有基板(FR4)等其他散热路径,所以 与放在边缘相比热阻上升变少。由于实机中存在多个元件,所以很难确保一个热源的铜箔面积 很宽,所以要以热源为中心,尽可能确保铜箔面积 360°均等, 这样的 Layout 非常重要。

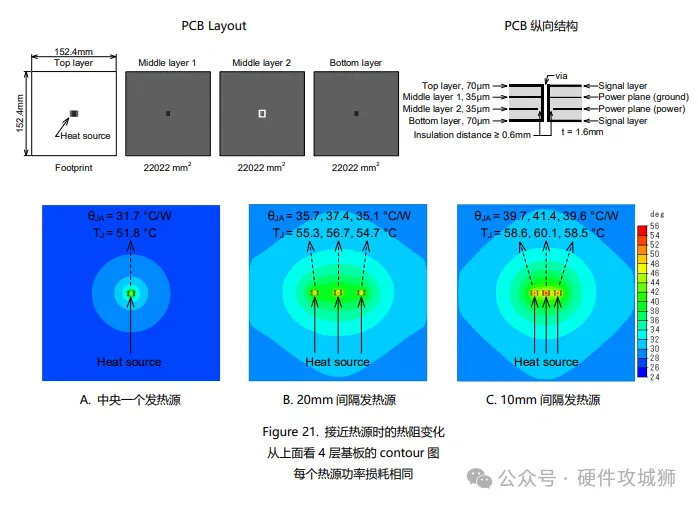

接近热源的情况下

Figure 21 是接近热源时的热阻变化。在这个例子中,B 和 C 接近 3 个功率损耗相同的热源,但与只有 A 一个热源时相比,热阻更高。这是因为各个器件都受到了热干扰,导致器件的周围温度上升。热源之间的距离越短,受影响越大。

像这样一个一个进行热设计时,即使设计目标值中有温度上升, 但如果三个同时工作,每个都受到热的影响,就必须考虑热干扰的现象进行热设计。多通道输出的电源、LED 驱动器、马达驱动器等,都有这样的情况。

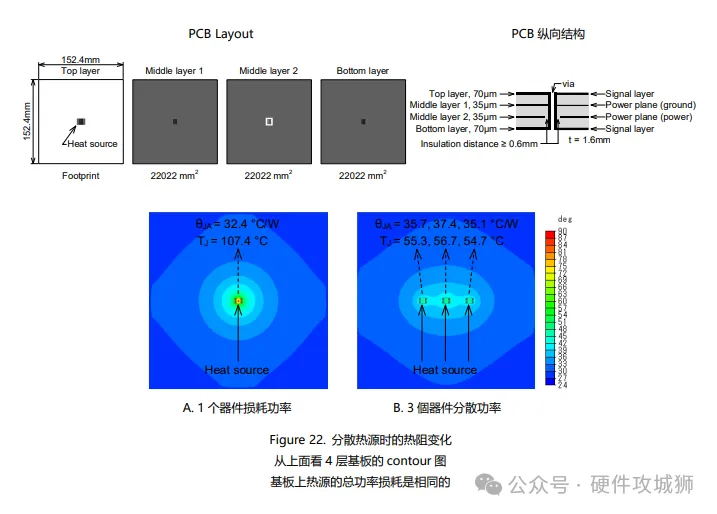

热源的分散

Figure 22 是分散热源时的热阻变化。A 是一个器件发生了功 率损耗的情况,接合温度是 107.4°C。B 是将 A 的功率损耗平 均分散到 3 个器件上的情况。虽然器件之间发生了热干扰,但分散热源可以减轻温度上升。这个是热传导面积增加导致热 阻降低。

像这样,分散热源(功率损耗)是降低一个器件温度的有效手段。这个例子以 IC 封装为例,电阻器等被动元件也有同样的效果。

考虑耐高温的被动元件

众所周知,电解电容器的温度越高,电解液就越容易蒸发,寿命也就越短,为了延长耐高温元器件的寿命,就需要降低过高的温度。被动元件从热源接受的路径有热传导、对流(热传递)、 热辐射三种。对流(热传递)是通过换气降低 箱体内温度。热辐 射要远离热源,或者用遮热板做好防热措施。因为热传导主要 是经由铜布线传热的,所以要远离热源,或者采取措施使铜布 线的宽度降到最低。

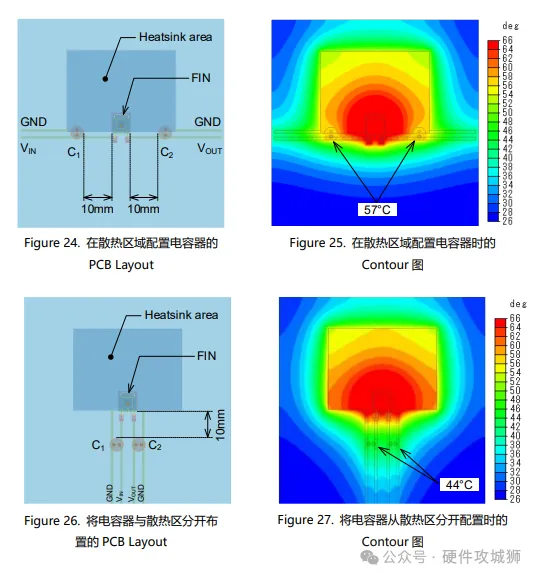

作为例子,在 Figure23 中示出 LDO 的电路,为了获得电气特 性,有时必须在热源装置附近配置电解电容器。在 3 引脚 LDO 中,像 TO252 封装那样同时使用散热用 FIN 和接地引脚配置 很多,在器件附近配置电解电容器 C1、C2 的话就会变成像 Figure 24 一样的 Layout 因为共用放热区域的铜箔和地布线 Figure 25 那样从放热 FIN 的热通过宽的铜箔向电容器传导。电容器引脚部的温度是 57°C。

作为对策,热源和电容器之间的距离是相同的,像 Figure 26 那 样,把布线宽度设定为电流容量能容许的最小尺寸,使热传导 最小,然后在那里配置电容器。Figure 27 是结果,电容器引脚 的温度降到 44°C。

这是因为与铜箔相比,基板(FR4)的热阻高,在相同的距离下也 很难导热。综上所述,如果只着眼于电气特性进行 Layout,可能会产生热 的问题,因此需要考虑热源器件和耐高温器件之间的位置关系。AC- DC 转换器等,用电解电容器平滑 AC 的纹波电压,不过, 由于大的纹波电流和电容器的内阻产生损耗功率,电容器自发 热。这种情况与前面提到的 Layout 相反,要加大布线面积,将 热量传导到布线上。

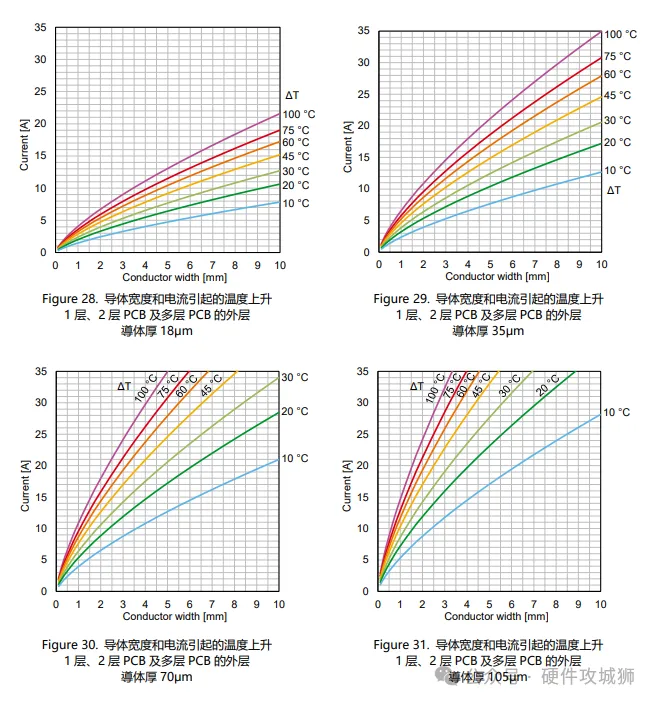

铜箔布线的温度上升

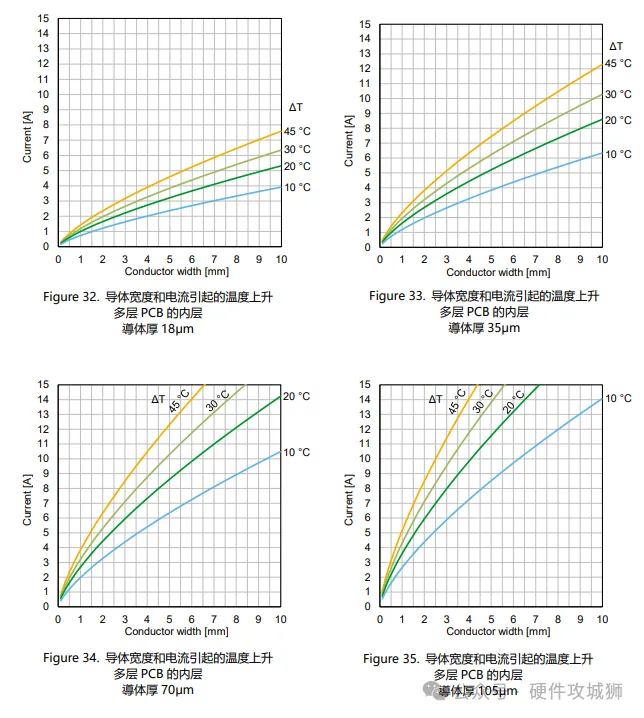

在大电流流过的导体(铜箔布线)中,最小宽度和厚度必须根据 所需的电流容量和最大允许导体温度上升来决定。如果不注意 这个,就会引起因温度上升引起的 PCB 的劣化和周围温度的上 升。最小导体宽度和厚度请参考下面的图表。这些图表是根据《IPC2221A, Generic Standard on Printed Board Design》中登 载的近似公式和图表,将单位换算成米制的。

Figure 28 到 31,在 1 层,2 层 PCB 和多层 PCB 的外层被适 应的温度上升,显示每导体厚度。同样 Figure 32 到 35 是适应 于多层 PCB 的内层的温升。

铜布线的温度上升和半导体封装的热阻一样,由于 PCB 材料、 Layout、元件配置、外壳形状、周围环境等的影响,其值也会 变化,所以请作为参考使用。

总结降低热阻的关键

铜箔面积

・随着铜箔面积的增大,热阻也随之降低。

・即使将铜箔面积增大到必要的程度,离热源越远,热传导效 率就会越差,就不能达到与面积相符的效果,因此铜箔面积应 采用适当的尺寸。

・在多层基板中,通过优先增大靠近热源层的铜箔面积,可以 有效地降低热阻。

板厚

・由于在 1 层底板上横向热传导占优势,所以如果增加板厚, 热阻就会降低。

・在多层基板中,散热用铜箔面积小的情况下,由于横向热传 导占优势,所以加厚板厚就会降低热阻。当铜箔面积大时,由于纵向热传导占优势,所以板厚越薄,热阻就越低。两者的边界线根据 PCB 的条件而改变。

层数

・随着层数的增加,热阻趋于降低,但在多层基板中,在与热 源相同或相邻的层上布置较大的散热铜箔面积,可以有效地降 低热阻。

铜箔厚

・铜箔越厚,热阻越低。铜箔面积越大,其效果越好。

散热孔

・孔数越多,热阻就越低,但离热源越远,热阻就越低,所以要 靠近热源。

・孔径越大热阻越低,但如果超过 0.3mm,在回流工艺中发生 焊锡吸入问题的可能性就越大,因此要注意。

热源的位置

・由于存在多个部件,所以很难确保一个热源的铜箔面积大, 但要注意以热源为中心尽可能确保铜箔面积 360°均等的 Layout。

热源接近的情况下

・在多个热源接近的情况下,设计时要考虑所有热源同时工作 的热干扰现象。

热源的分散

・分散热源(功率损耗)作为降低一个器件的温度的方法是有效 的方法。考虑耐高温的被动元件

・如果只关注于电气特性进行 Layout,有时会发生热的问题。

・需要考虑作为热源的器件和不耐高温的器件之间的位置关系。

・当热源装置位于附近时,布线宽度应达到所需的最低限度, 以防止热传导穿过低热阻的铜布线。

铜布线的温度上升

・在大电流流动的导体(铜箔布线)中,导体的最小宽度和厚度需 要根据所需的电流容量和最大允许导体温度上升来确定。如果 不注意这个,就会引起因温度上升引起的 PCB 的劣化和周围 温度的上升。

免责声明:本文转自网络,版权归原作者所有,如涉及作品版权问题,请及时与我们联系,谢谢!

0

0