RS485硬件电路设计解析

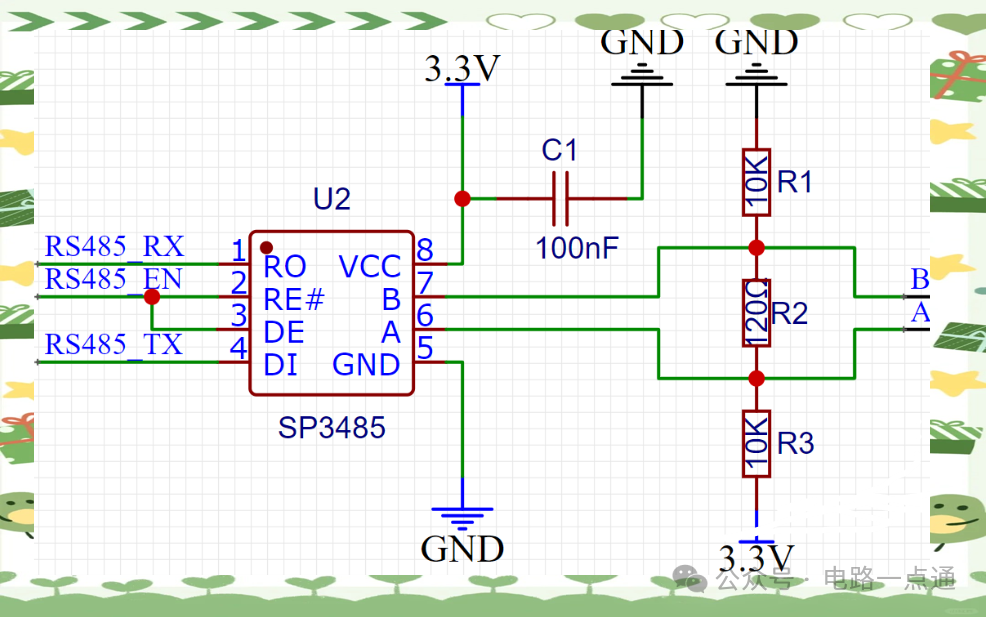

RS485电路设计主要分为隔离型和非隔离型两种类型。以非隔离型电路为例,B端通过接地实现下拉,而A端则通过上拉电阻维持高电平,这样确保了A和B之间的电压差超过200mV,从而满足RS485的逻辑判断需求。此外,电路中的DE和RE引脚分别用于控制发送和接收功能。当RE引脚置为低电平时,芯片处于接收使能状态;而DE引脚置为高电平时,芯片则进入发送状态。在实际应用中,这两个引脚通常通过一个IO口(如RS485_EN)进行统一控制。这样,芯片在任意时刻都只能处于接收或发送的一种状态。因此,在发送数据前,需要给RS485_EN信号置为高电平以启动发送功能,而在接收数据时则置为低电平以切换到接收模式。

RS485自动收发电路硬件设计详解

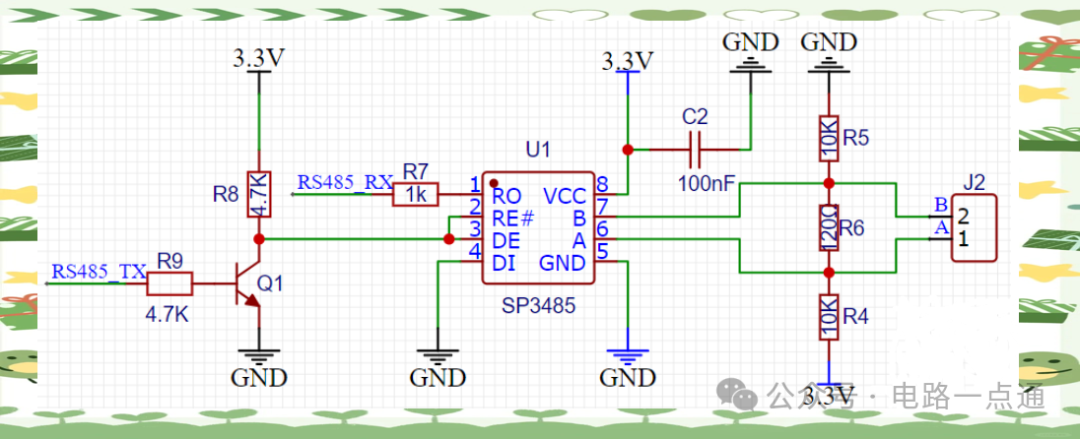

自动收发电路相较于普通的485电路,其关键差异在于增加了一个晶体管来控制485的使能引脚。设计中,R9限流电阻通常取值为4.7K,而R8上拉电阻也设定为4.7K,以确保在晶体管未导通时,使能引脚能够被有效上拉。这样的设计使得电路能够根据需要自动切换收发模式,提高了数据的传输效率与灵活性。

接收数据时,RS485_RX引脚作为接收数据引脚,负责接收外界数据。在接收过程中,RS485_TX引脚保持高电平,同时VGS也处于高电平,这使得NPN三极管Q1得以导通。通过晶体管的导通,RE和DE相连的引脚被下拉至GND,从而启动了接收使能,使电路进入接收状态。发送数据时,RS485_TX引脚作为发送数据引脚,负责向外界发送数据。当RS485_TX发送高电平(即1)时,晶体管导通,使得RE和DE的电平降低,从而关闭了RS485收发芯片。由于常态下485为高电平,因此此时发送的数据即为高电平。相反,当RS485_TX发送低电平(即0)时,晶体管不导通,这会使485收发芯片的发送使能变为高电平,同时DI引脚被持续下拉至GND,因此发送出去的数据为低电平。通过这种方式,电路实现了485的自动收发功能。此外,为了进一步增强电路的稳定性和耐久性,我们还设计了RS485接口的防雷电路。这一设计能够有效地保护电路免受雷电等外部干扰的影响,确保数据的传输安全与稳定。

接口防护电路

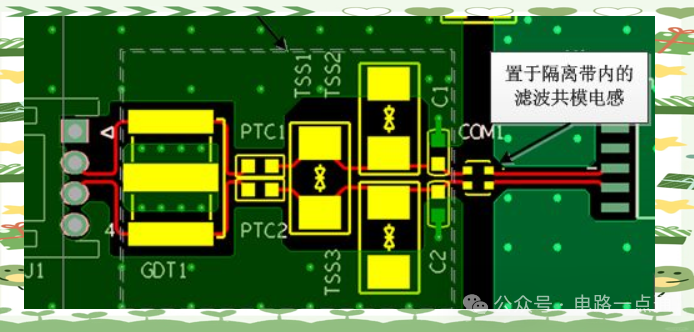

L1作为共模电感,其核心作用是衰减共模噪声并增强电路的抗干扰能力。在选择时,通常考虑120Ω/100MHz的规格。而C3电容则主要用于隔离接口地与数字地,以防止潜在的干扰,其值一般选为1000pF。为了确保电磁兼容性(EMC)达到高标准,即差模信号能够承受2kV的冲击,共模信号能抵御6kV的干扰,我们在接口处精心设计了由气体放电管、热敏电阻和TVS管共同组成的防护电路。在布局RS485接口电路的PCB时,需注意GND的设计。为确保防护效果最佳,虚线所示的防护器件应尽可能地靠近接口位置,且摆放要紧凑有序。通常,我们首先放置这些防护器件,然后再进行滤波器件的布局。

RS485接口电路设计涵盖了诸多关键要素,包括信号传输、电气隔离、噪声抑制、保护措施,以及电源和控制逻辑的设计等。在信号传输方面,通常选用一对双绞线作为差分信号线(A和B),并优先考虑使用屏蔽双绞线电缆,以最大程度地减少电磁干扰。同时,应确保A和B线的长度尽可能相等,从而减少信号延迟差异,进而保障信号的完整性。为了抑制共模干扰,需要在信号线入口处加入共模电感L1。推荐选用阻抗范围在120Ω/100MHz至2200Ω/100MHz之间的共模电感,以充分发挥其抑制作用。此外,还可能需要在电路中并联去耦电容和TVS管等元件,以进一步提升电路的抗干扰能力。在选择收发器芯片时,常见的选项包括SP3485、MAX485等,它们能够将TTL/CMOS逻辑电平有效地转换为RS485差分信号。同时,需要仔细关注RE、DE以及RO等控制引脚的连接逻辑,通常RE和DE可以通过单个控制信号进行连接,从而实现对发送/接收模式的统一控制。在偏置和终端电阻方面,A信号线可能需要上拉电阻(如10kΩ至4.7kΩ),以确保在空闲时的电压状态;而B信号线则可能需要下拉到GND。此外,在总线的两端或适当位置应放置120Ω终端电阻,以减少信号反射并改善信号质量。为了增强电路的鲁棒性,可以在信号线上添加TVS管和/或自恢复保险丝,以实现过压和浪涌保护。在高风险环境中,甚至需要加入6kV以上的防雷击保护电路设计。此外,良好的接地设计对于RS485接口电路的性能至关重要。特别是接口地的处理,有时可能涉及单板地与外壳的直接连接,并通过1000pF电容进行耦合。在电路板布局时,应确保电源和信号线的分离,以减少交叉干扰,并增加滤波和退耦电容的使用。最后,根据应用需求,可能需要设计相应的控制逻辑电路或使用MCU来控制发送使能信号,从而实现自动或手动的发送/接收切换。对于需要自动收发管理的电路设计,可能需要更复杂的逻辑来自动调节发送和接收状态,以适应不同的通信场景。

RS485接口电路设计并不仅仅是技术层面的考量,它还需要综合考虑电磁兼容性(EMC)、系统的可靠性以及安全性等多个方面,以确保在复杂的工业应用环境中能够保持稳定的通信性能。

0

0