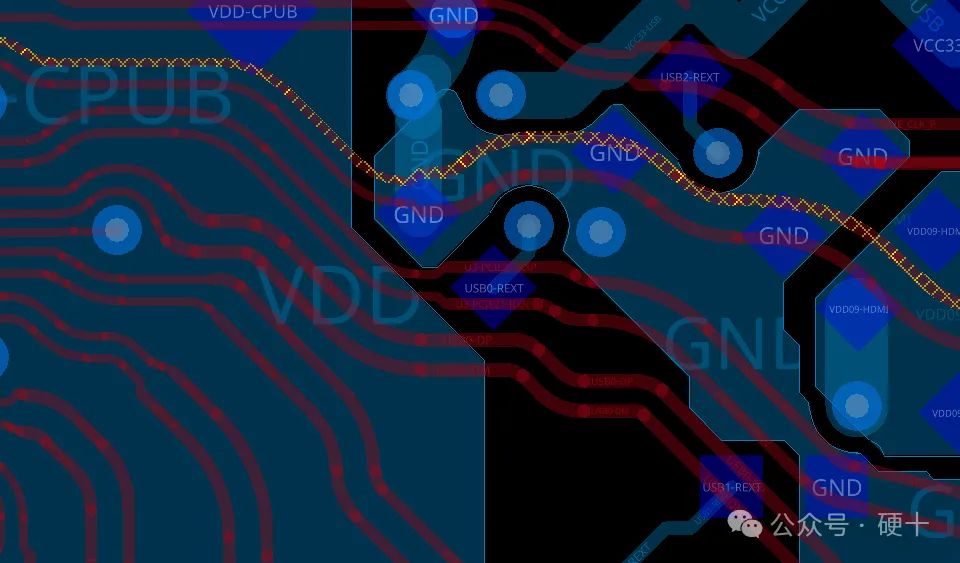

走线的宽度从3mil变成了4.5mil

在PCB设计中,”Necking(缩颈设计)”特指在受限布线区域(如BGA、连接器下方)通过临时缩小线宽/线距实现走线穿出的设计方法。这种设计虽能解决高密度互连难题,但若处理不当会引发系统性风险。以下从实际工程案例出发,剖析关键缺陷。

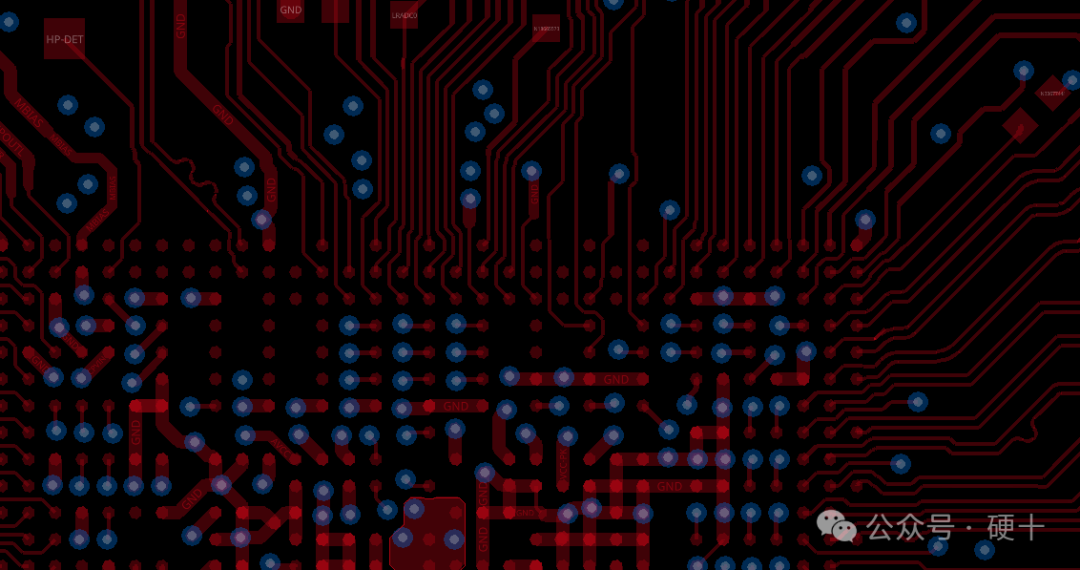

Necking设计的典型缺陷

-

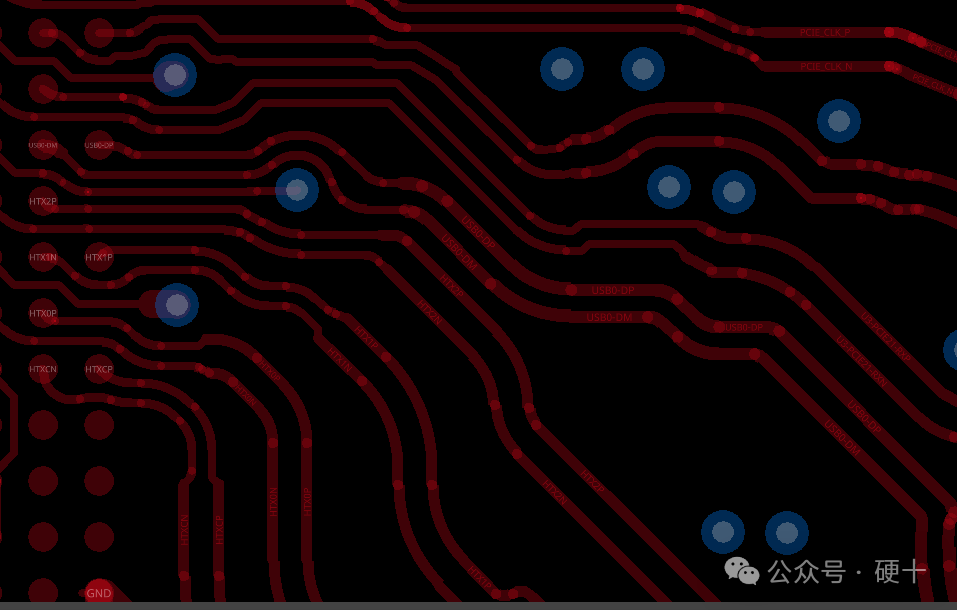

阻抗突变

-

某5G基站FPGA板卡案例:BGA区域采用4/4mil Necking设计(主通道6/6mil),导致28Gbps SerDes信号阻抗从85Ω突降至72Ω,眼图张开度下降40%。线宽w缩小20%引发阻抗变化超过15%,破坏信号完整性

电源走线的载流能力

-

新能源车控模块案例:电源线在BGA出口处从15mil缩至8mil,温升测试显示缩颈区域温度达98℃(超出安全阈值23℃)

-

线宽缩小导致截面积A减小,温升呈平方关系恶化

制造良率

-

某手机主板量产后发现:采用4mil Necking设计的BGA区域,ICT测试不良率是常规区域的5倍

-

微观分析:蚀刻因子(Etch Factor)<3时,4mil线宽侧蚀偏差达±1.2mil

一、全部走4.5mil,走不通

二、走NeckDesign,先走3mil,再走4.5mil,会有阻抗不连续、制造良率的问题。

三、全部走3mil?

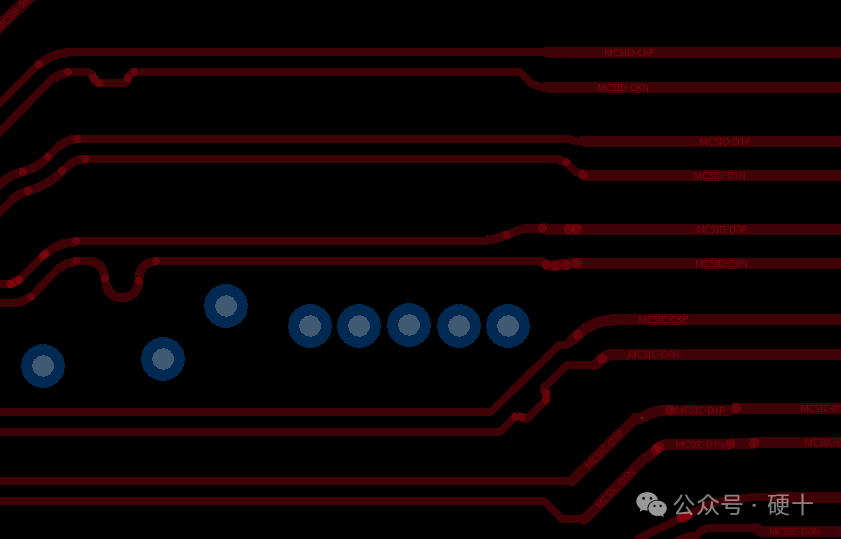

为什么BGA扇出时使用3mil,而后续走线加宽?为什么选择NeckDesign,而不选择一直走3mil呢?

因为3mil有很多缺点:

-

铜箔附着力临界值:当线宽降至3mil(约76μm),铜箔与基材的剥离强度骤降40%以上。根据IPC-6012标准,3mil线宽需配合特殊表面处理(如化学镀镍金),否则在热应力测试中易发生铜箔剥离

-

蚀刻工艺窗口:3mil线宽要求蚀刻侧蚀量控制在±0.5mil以内,相当于普通工艺精度的3倍。某台系PCB厂的良率数据显示,持续3mil走线的报废率比5mil走线高17.8%

-

阻抗失控区:在FR4板材(εr=4.2)上,3mil线宽对应50Ω特性阻抗需要1.2mil介质厚度。这种薄介质层会导致:

-

传输线损耗增加(@10GHz时插入损耗比5mil线宽高1.2dB/inch)

-

邻近效应加剧(相邻走线间距<6mil时串扰增加8-12%)

-

趋肤效应恶化:3mil线宽在5GHz以上频率工作时,有效导电截面仅剩中心42%区域,电阻率飙升导致温升超标

-

热机械应力:某手机SoC实测数据显示,3mil走线在温度循环(-40℃~125℃)中的断裂概率是5mil走线的3.2倍

-

电迁移风险:根据Black's方程推算,3mil线宽在3A/mm²电流密度下的MTTF(平均失效时间)仅为常规设计的1/5

-

维修可行性:返修台热风枪作业时,3mil走线的热容过低,极易发生相邻线路熔断

-

制造成本曲线:线宽每缩小1mil,PCB加工费增加15-20%。某通信设备商的成本分析显示,全程3mil走线会使四层板成本增加37%

-

测试成本飙升:飞针测试机对3mil线宽的测试速度下降40%,且需要更昂贵的微针头

设计决策:

当BGA间距≤0.8mm时,可接受局部3mil走线,采用NeckDesign,但需满足:

-

单板3mil走线总长<15%

-

避开电源/时钟等关键网络

-

在DFM报告中标注特殊管控区域

-

增加2oz铜厚补偿载流能力

-

可以采用梯度过渡的方式,3.5/3.5mil → 过渡段:4/4mil(长度≥20mil)→ 主通道:5/5mil

0

0