使用 Altium Designer 控制阻抗走线

受控阻抗是由 PCB 走线及其相关参考平面形成的传输线的特征阻抗。当高频信号在PCB 传输线上传播时,这很重要。在本文中,我们将使用 Altium Designer演示受控阻抗路由。

受控阻抗对于解决信号完整性问题很重要,信号完整性问题是信号在 PCB 走线上的无失真传播。

让我们带您完成以下步骤,以使用 Altium Designer 为单端和差分走线实现所需的阻抗:

1 使用 Altium Designer 创建受控阻抗路由的类

2 使用 Altium Designer 设置差分对(100 欧姆)布线的规则

3 使用 Altium Designer 为单端 (50 ohms) 线路设置规则

4 差分对布线使用 Altium Designer

5 使用 Altium Designer 的单端布线

6 试用 Sierra Circuits 的新阻抗计算器

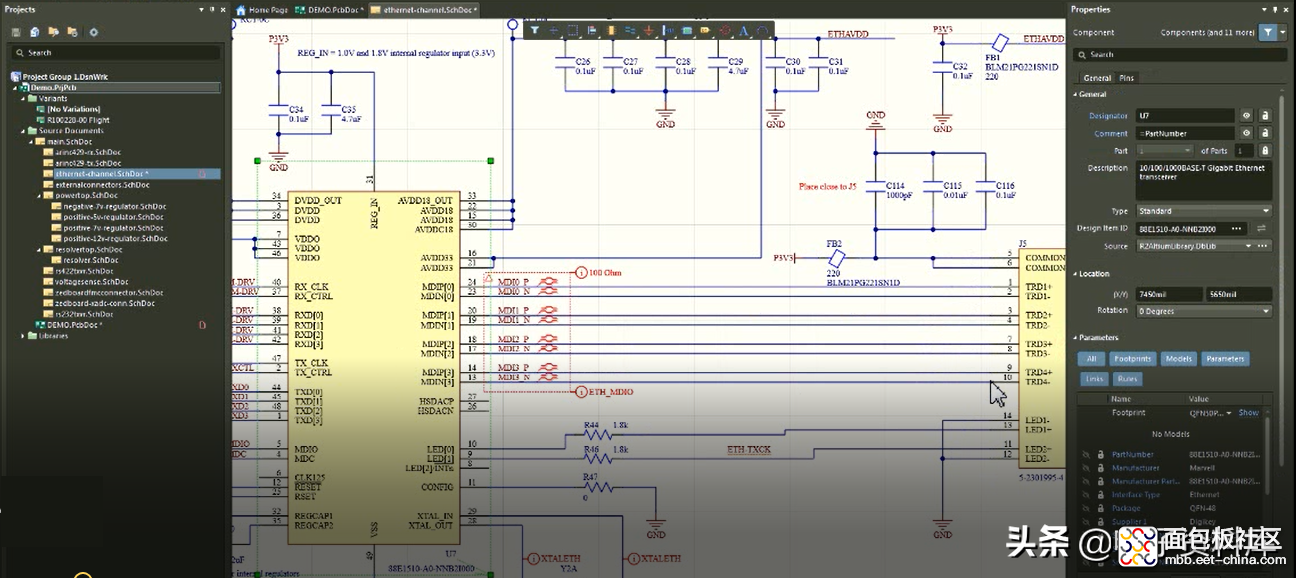

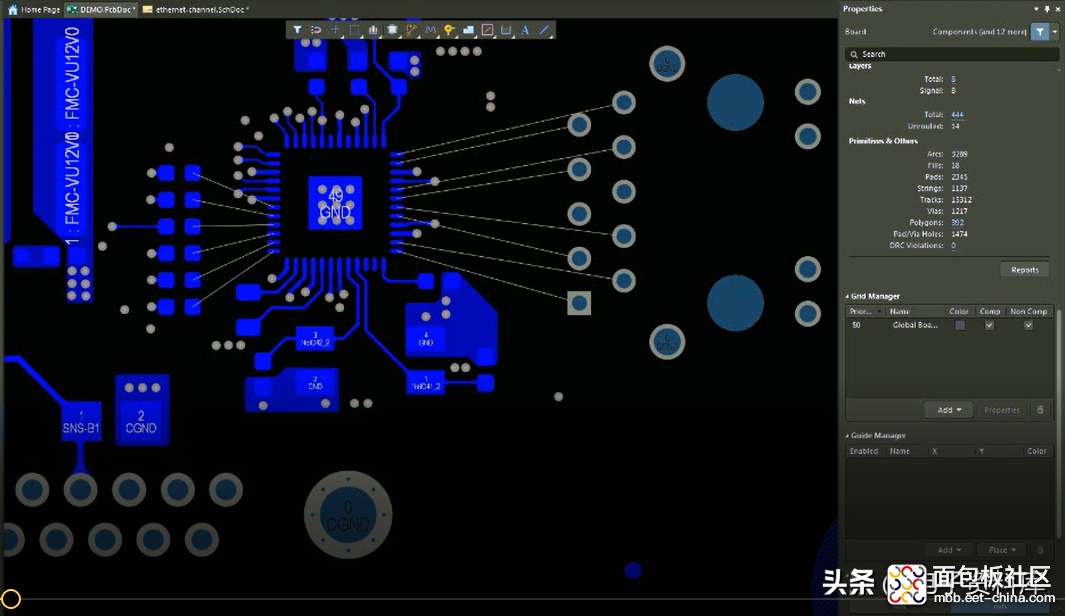

在本演示中,我们将向您展示如何布线100 欧姆的差分对和50 欧姆的单端线。在这里,这是带有以太网 IC和RJ45连接器的以太网部分。

带有以太网 IC 和 RJ45 连接器的以太网部分。

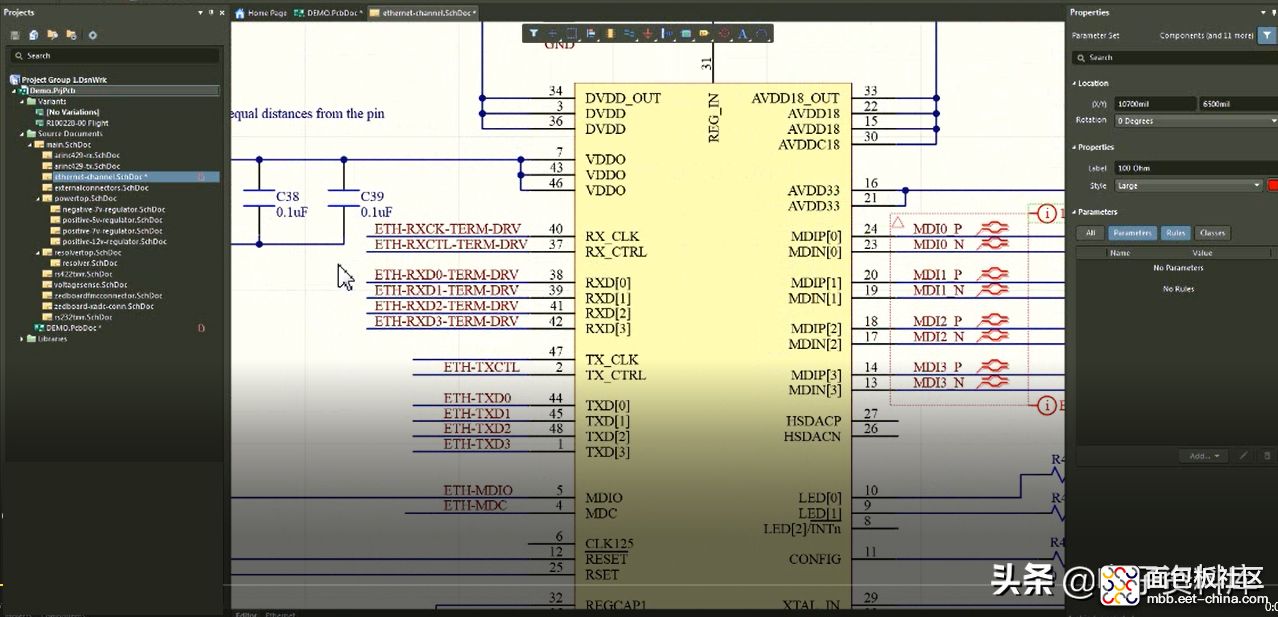

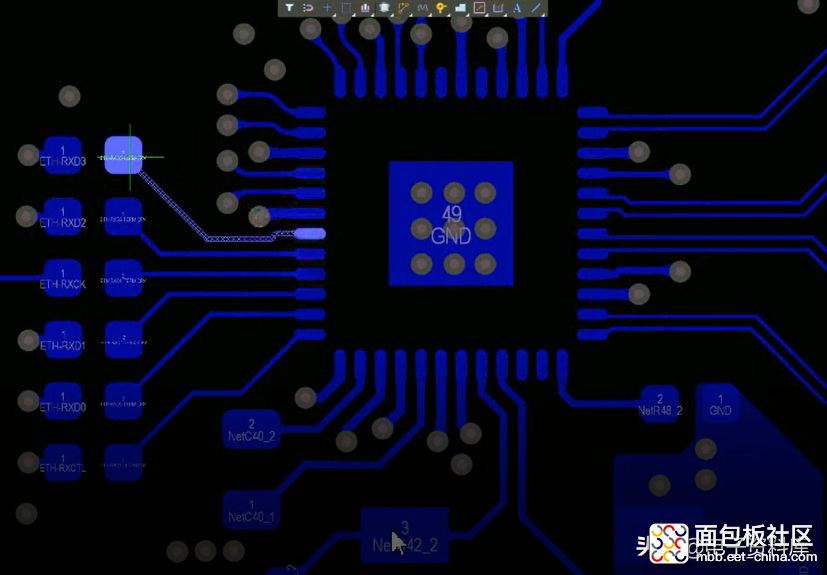

您可以看到带有接收器 (RX) 和发送器 (TX) 部分、RX 时钟、RX 控制以及 RXD0、D1、D2 和 D3 的网络。这些都是单端50 欧姆走线。

带有接收器 (RX) 和发射器 (TX) 部分的网络。

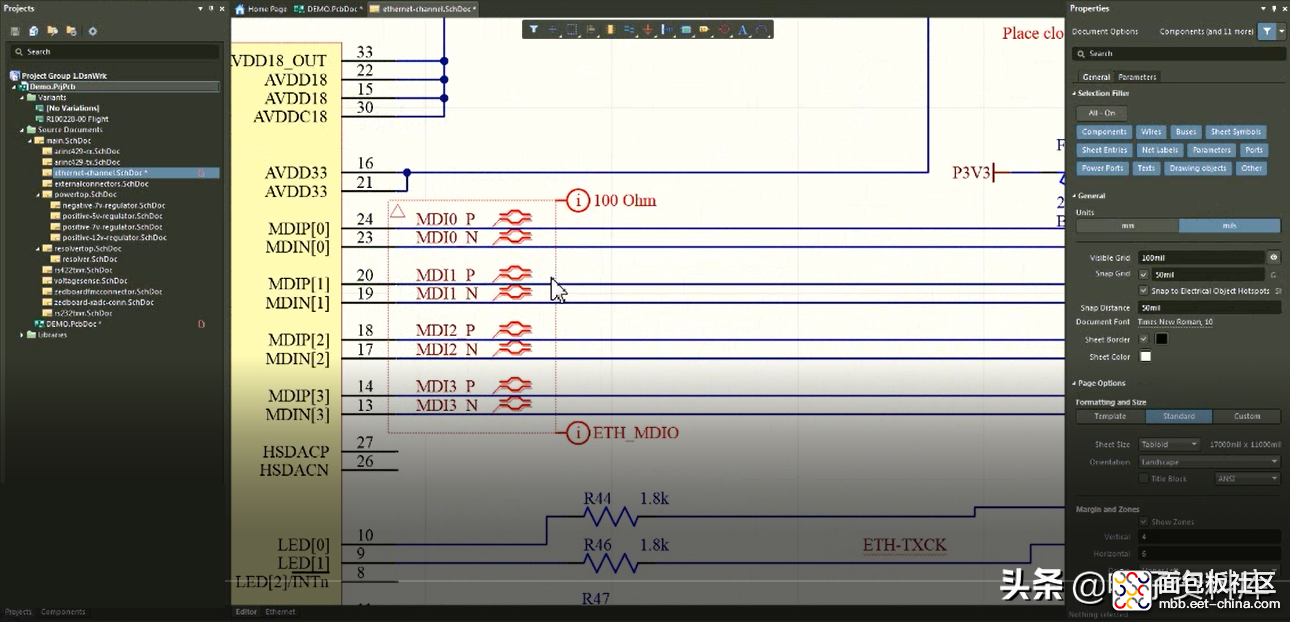

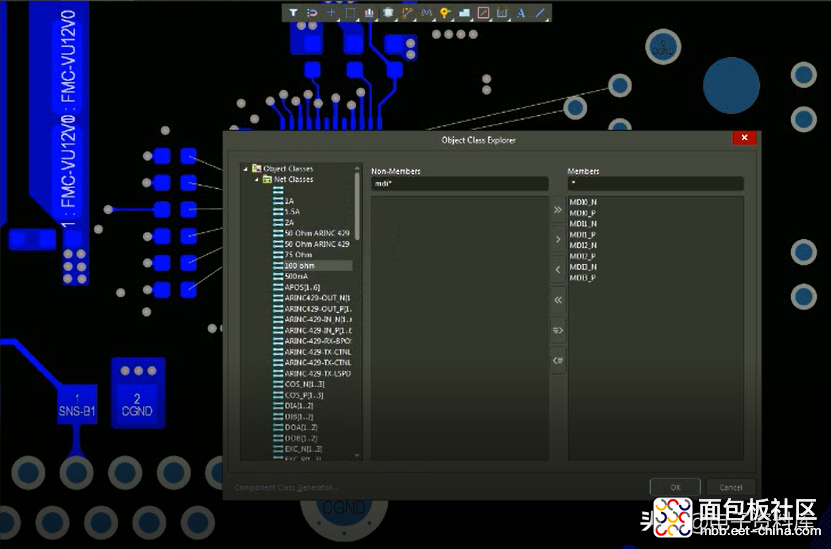

在 IC 的另一侧,您可以看到MDI0、1、2和3。所有这些连接都是100 欧姆 差分对。

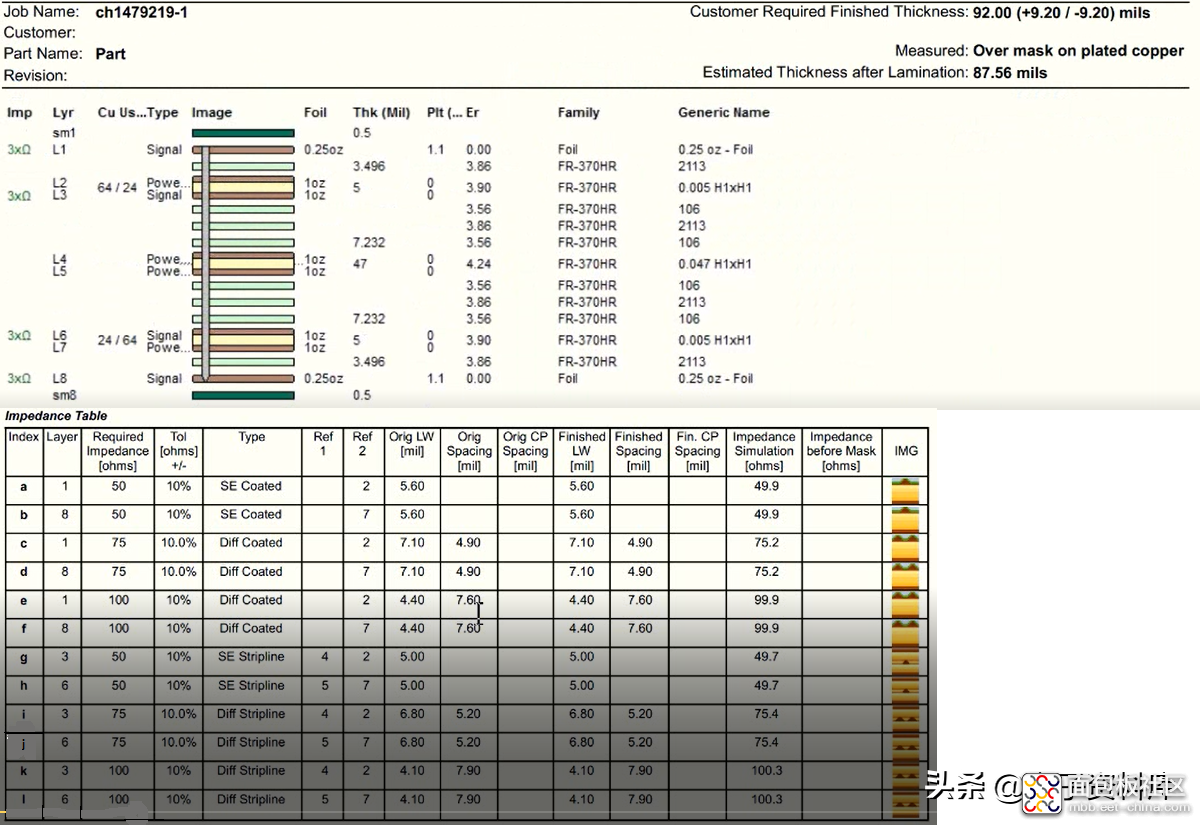

为了达到阻抗,我们需要一定的走线宽度;这些将由制造商以堆叠的形式提供。下面给出的图像描述了一个堆叠示例。在这个叠层中,给出了层数,给出了所需的阻抗,还给出了走线宽度和走线之间的间距。

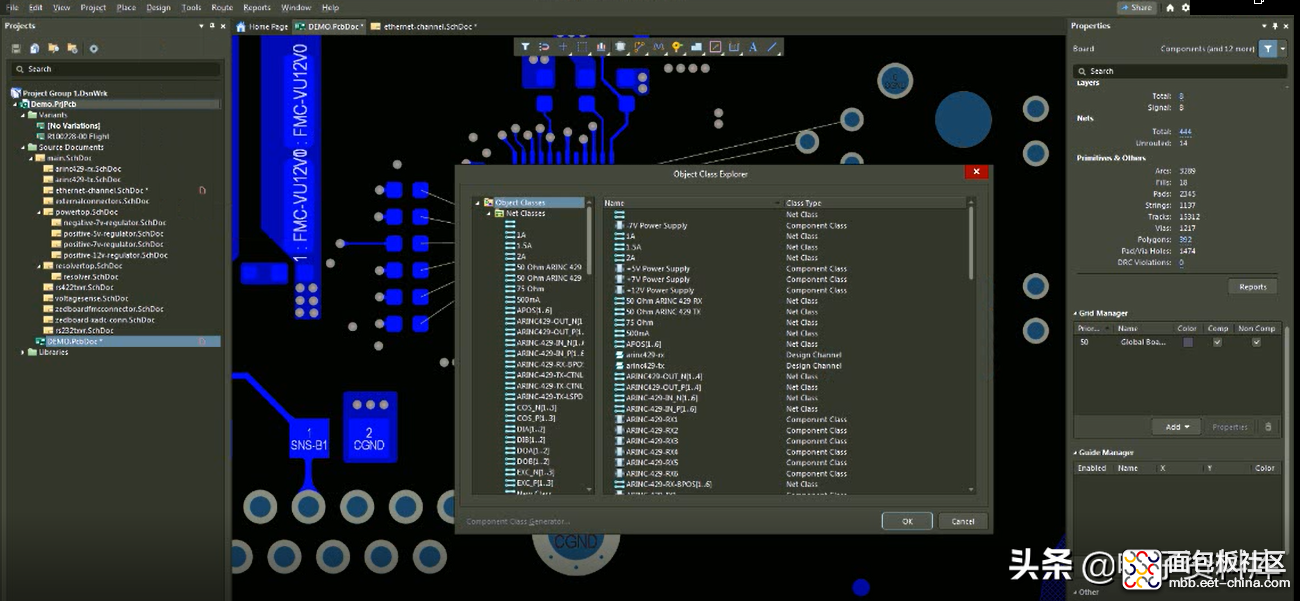

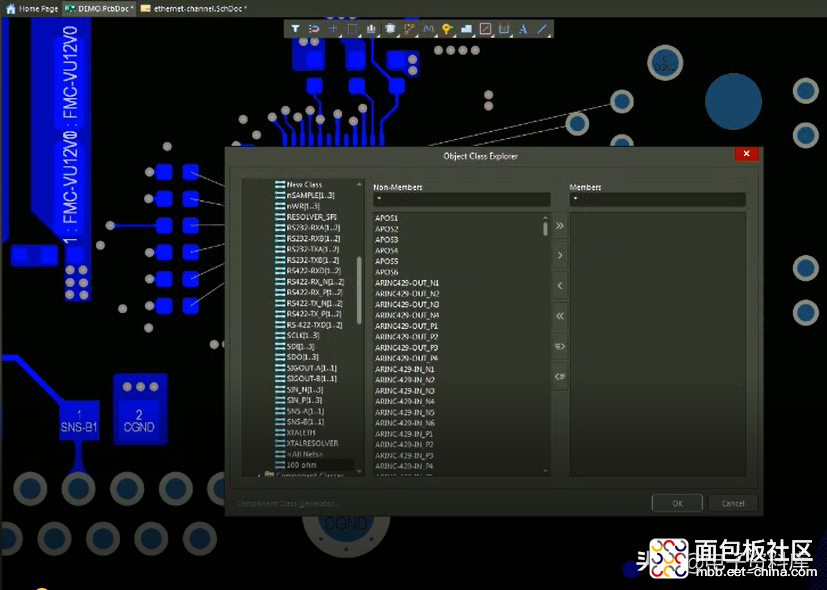

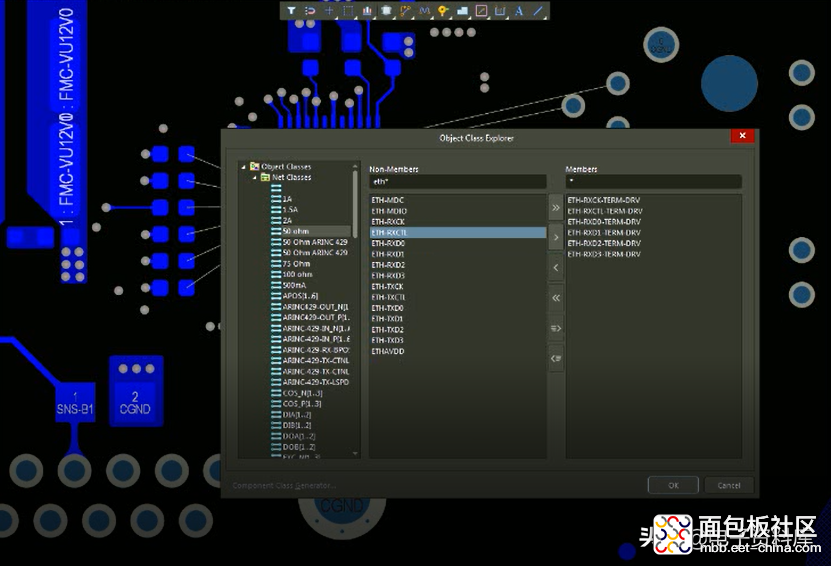

使用 Altium Designer 创建受控阻抗路由的类

50 和 100 欧姆走线的Classes。

- 转到‘Design’ >> ‘Classes’ >> ‘Net classes.’

- 右键单击‘Net classes’>>单击‘Add classes.’

- 为这个类命名(在我们的例子中为 100 欧姆)。

- 转到这个 100 欧姆等级并选择该等级中存在的网络,然后单击箭头 ( >)。

- 这样,类中的所有网络都将分配到 100 欧姆的走线。

注意:以同样的方式,我们将创建一个50 欧姆的 类。

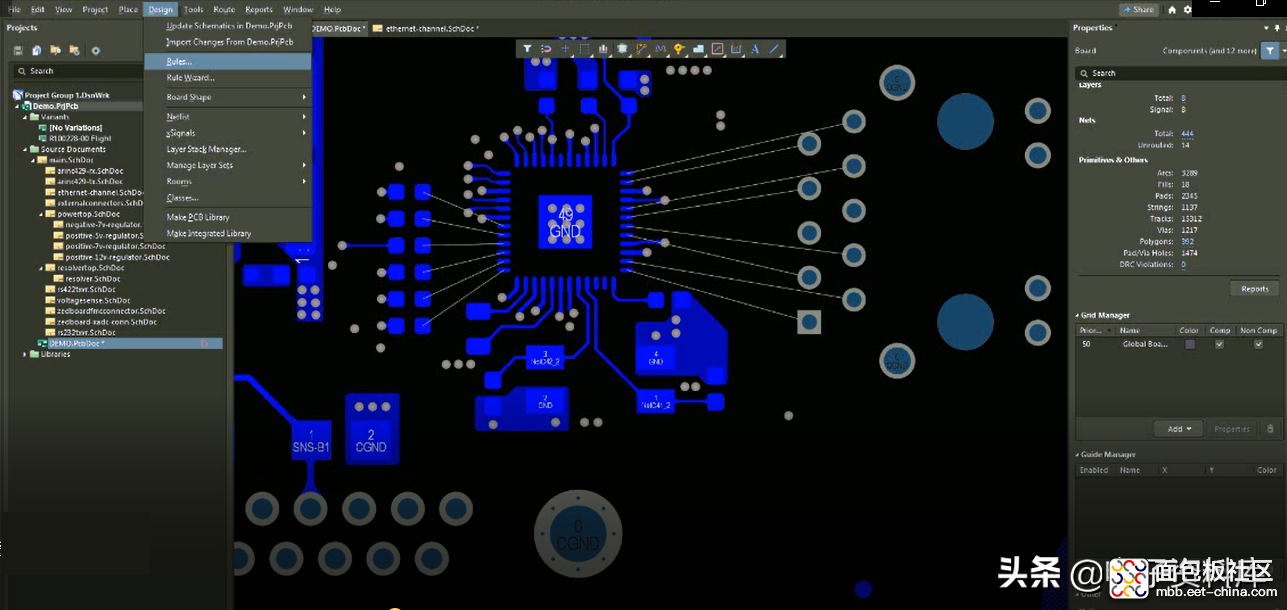

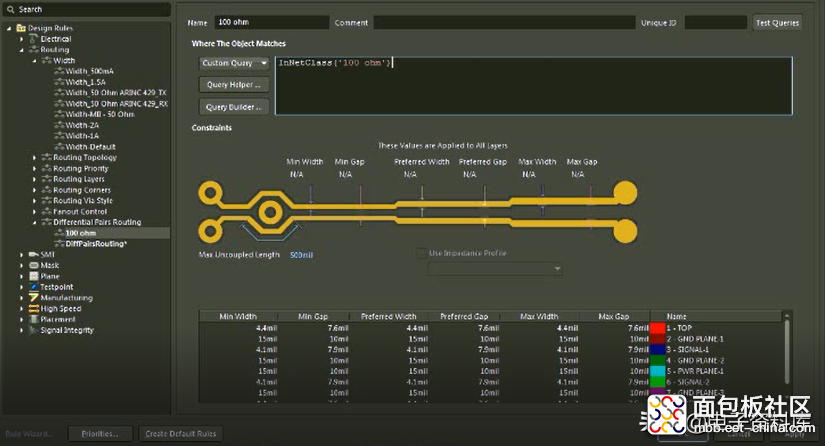

使用 Altium Designer 设置差分对(100 欧姆)布线的规则

要为我们上面创建的类设置规则,我们将按照以下步骤操作:

- 转到“设计”>>“规则”。

- 转到“差分对规则”>>“新规则”。

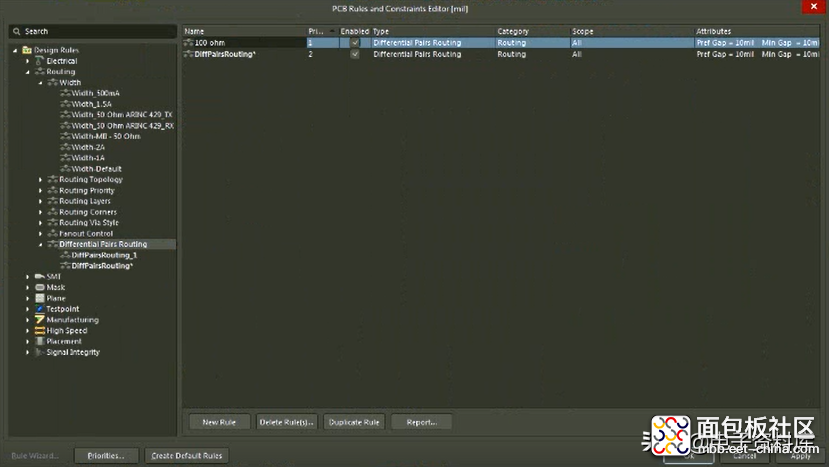

- 为此规则命名(在本例中为 100 欧姆)并双击。

- 我们现在将放置顶层、底层、信号一和信号二的值。对于我们叠层中的顶层,值为 4.4 mils 和 7.6 mils。

- 添加最小宽度、首选宽度和最大宽度。最小宽度为 4.4 密耳,最小间隙为 7.6 密耳。

- 阻抗取决于走线宽度和间距。一旦我们这样做,我们将再次进入堆栈并交叉验证信号一和信号二值。信号一和信号二值分别为 4.1 密耳和 7.9 密耳。

- 将信号一和信号二值相加。并转到下拉框并选择自定义查询。

- 在下拉框中,输入 Net Class 并选择 100ohms。

注意:顶层和底层的值将相同。不使用接地层和电源层。

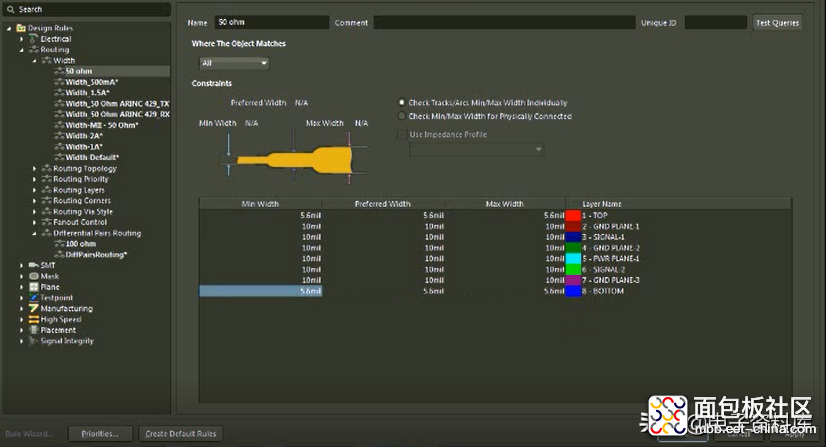

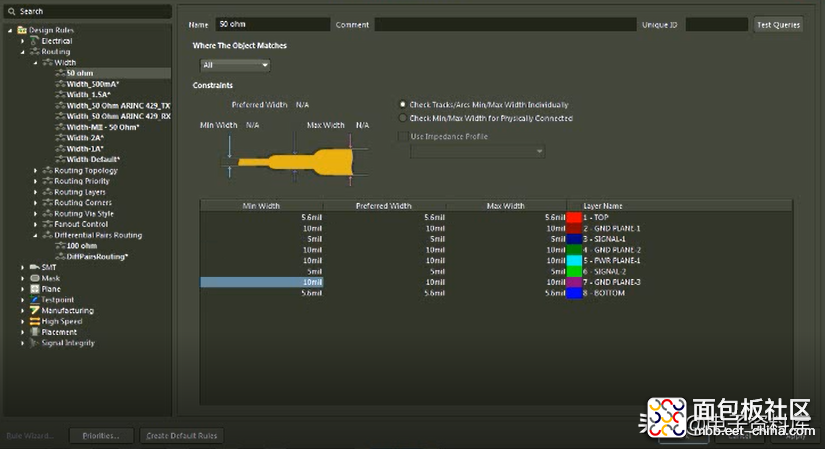

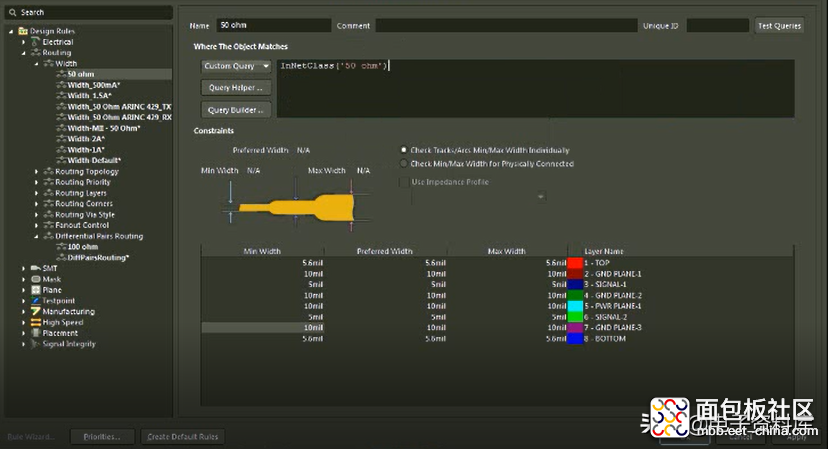

使用 Altium Designer 为单端 (50 ohms) 线路设置规则

- 转到“设计”>>“规则”。

- 转到“单端规则”>>“新规则”。

- 为此规则命名(在本例中为 50ohms)并双击。

- 我们现在将放置顶层、底层、信号一和信号二的值。对于我们叠层中的顶层,该值为 5.6 密耳。

- 添加最小宽度、首选宽度和 5.6 密耳的最大宽度。

- 转到堆栈并将信号一和信号二值相加,即 5 密耳。

- 转到下拉框并选择自定义查询。

- 在下拉框中,输入Net Class并选择50 ohms。

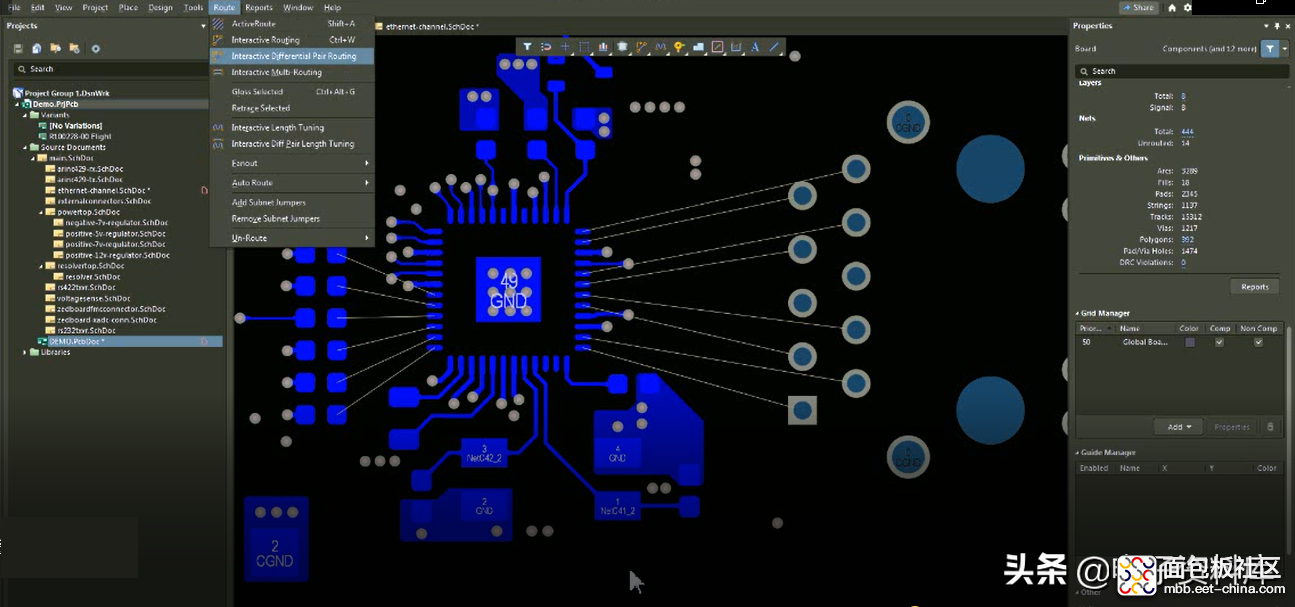

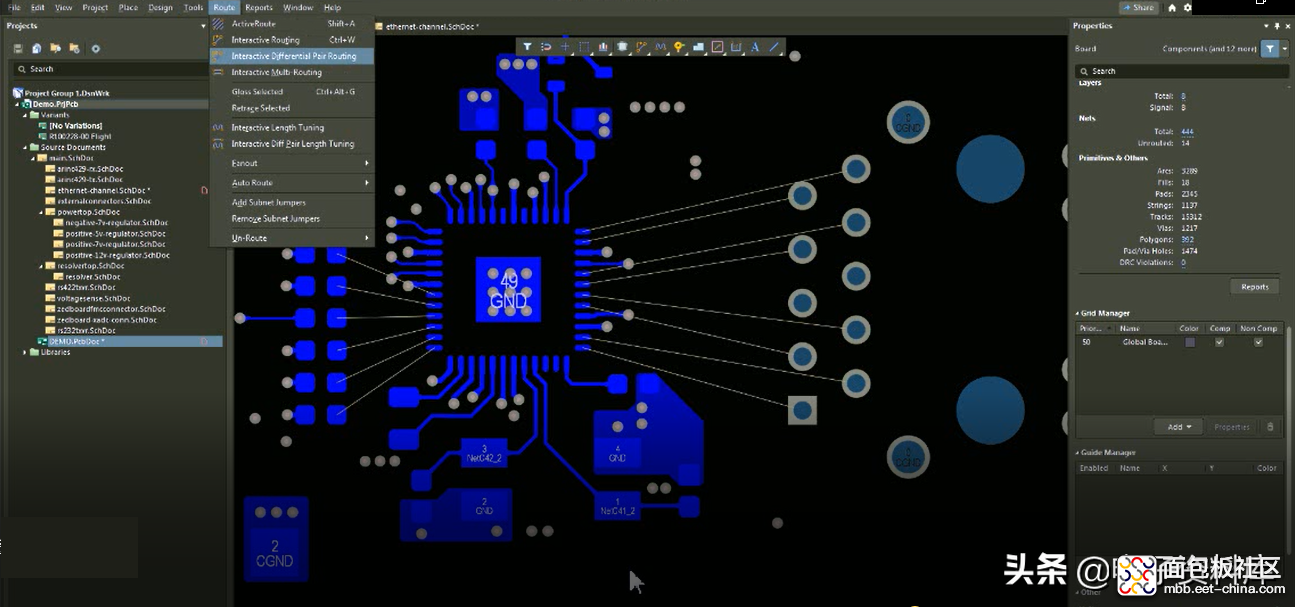

使用 Altium Designer 进行差分对布线

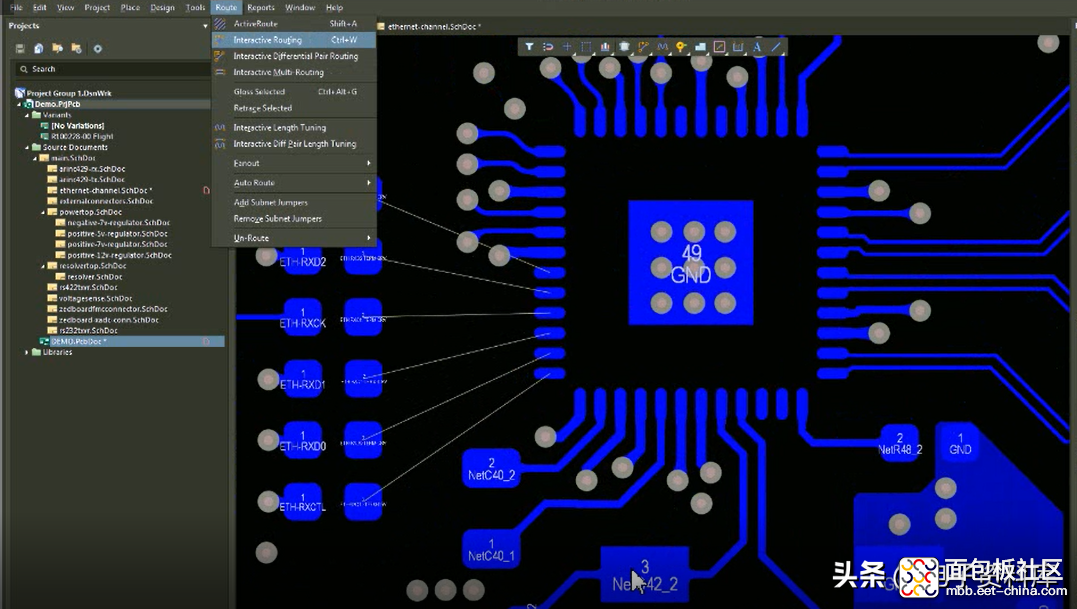

- 对于差分对路由,转到“交互式差分对走线”>>“走线”。

- 现在,选择网络并进行布线。

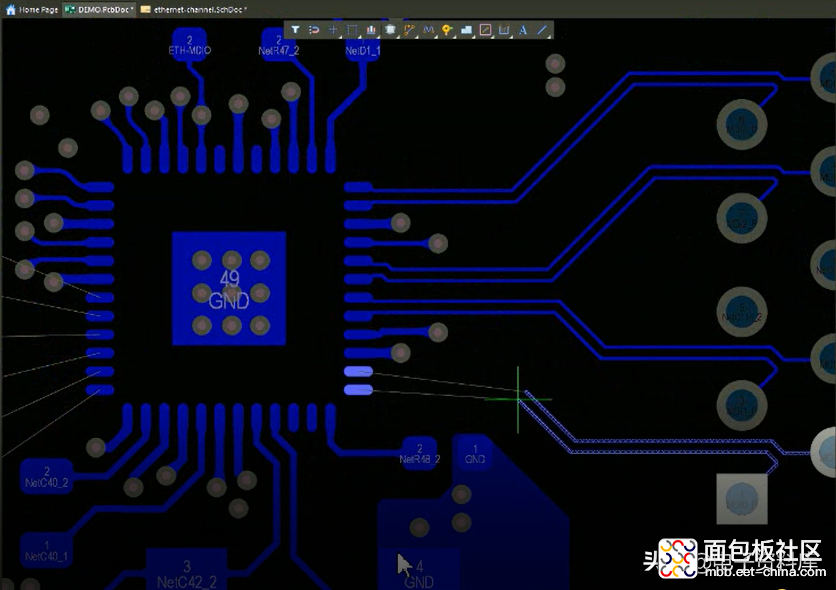

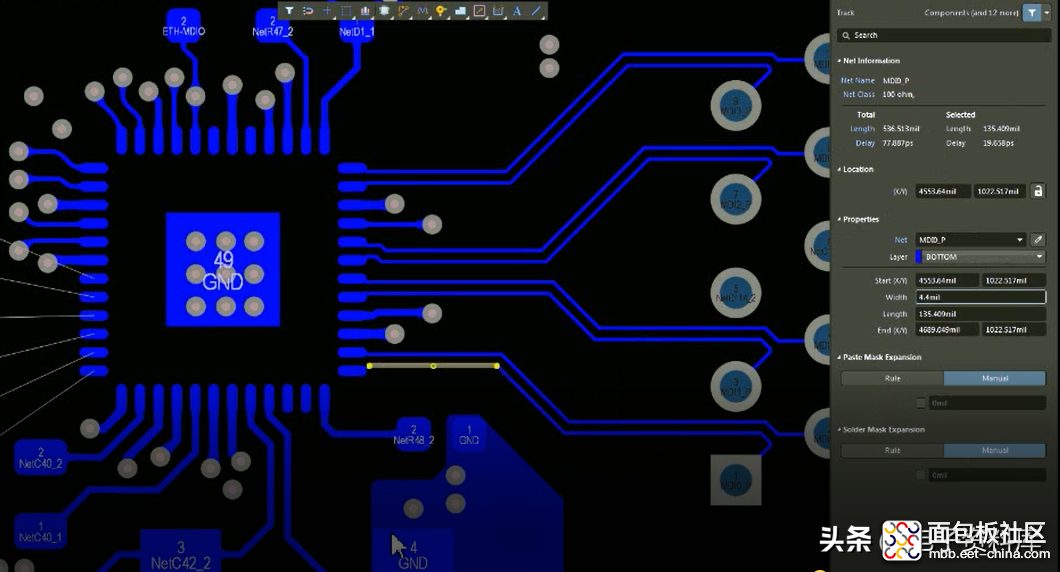

- 完成布线步骤后,检查这些特定走线的值。选择任何跟踪,转到属性,然后检查值。此处,走线宽度为 4.4 密耳,与叠层中给出的相同。

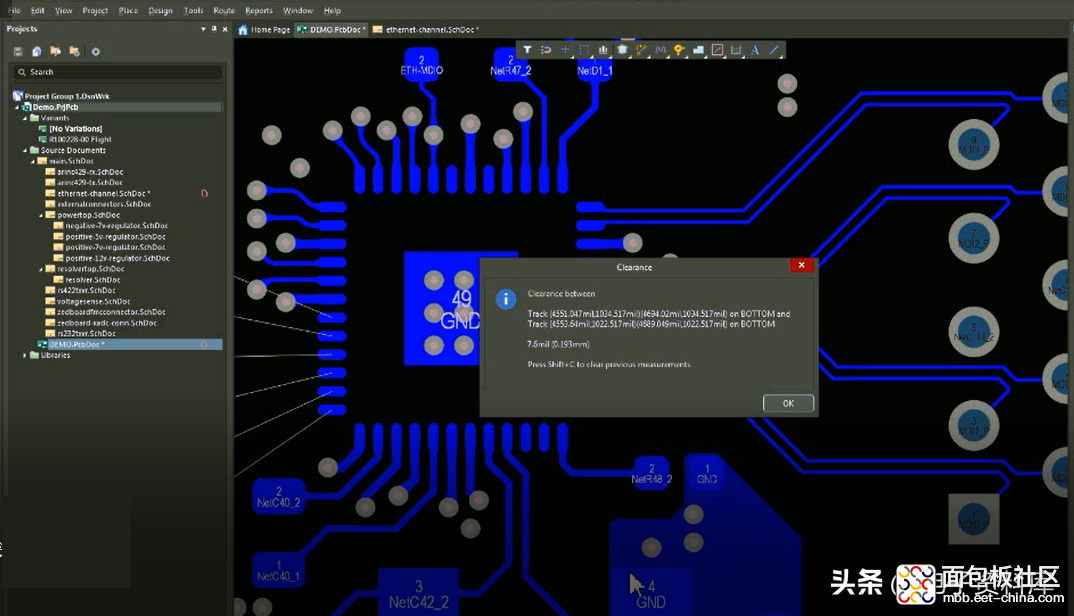

- 现在去报告和测量基元。选择两条走线,它们将为我们提供两条走线之间的气隙(7.6 密耳),这与叠加值相同。

使用 Altium Designer 的单端布线

- 对于单端路由,转到“交互式路由”>>“路由”并重复上述步骤。

- 布线完成后,检查走线宽度。

- 在属性下选择跟踪。您将看到迹线宽度为 5.6 密耳,与叠层中给出的相同。

层包含受控阻抗,这就是为什么我们需要在晶圆厂注释中指定这些阻抗,因为每层可能有多个阻抗迹线值。为受控阻抗迹线定义了单独的孔径代码。走线阻抗是在走线上不失真地传输信号的关键因素。阻抗必须与驱动器和负载相匹配。我们希望我们关于使用 Altium Designer 的受控阻抗布线的教程可以帮助设计人员在布线 PCB 时理解并遵循细微的细节。

来源:电子资料库

/1

/1