- 使用说明

操作环境:

- Windows 7/10 64bit;

- Xilinx Vivado 2017.4。

本文档以光盘"Demo\FPGA-HLS-demos"目录下的tl-hls-led-flash例程为例,演示使用TcL脚本生成Zynq PL端Vivado工程的步骤。

将光盘"Demo\FPGA-HLS-demos"文件夹复制到Windows非中文路径下,例如复制到C盘根目录。注意:Windows路径有长度限制,路径太长会导致出错。

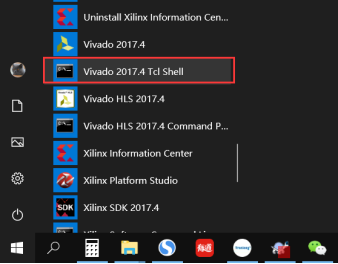

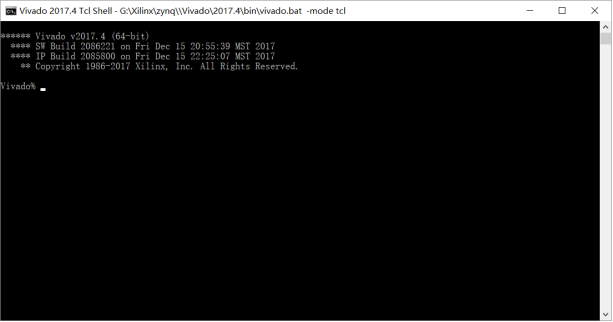

- 打开Vivado Tcl命令行终端

在Windows开始菜单打开Vivado 2017.4 Tcl Shell。

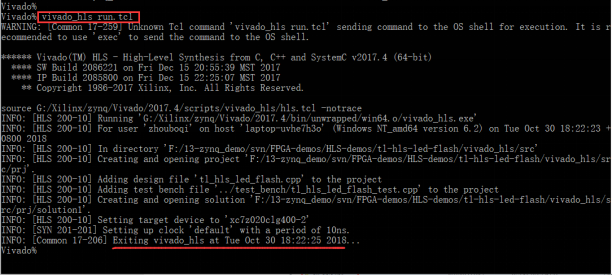

- 执行Tcl脚本生成HLS工程

(1)进入HLS脚本所在目录tl-hls-xxx/vivado_hls/src/:

Vivado%cd F:/FPGA-HLS-demos/tl-hls-led-flash/vivado_hls/src

(2)执行run.tcl脚本生成HLS工程:

Vivado%vivado_hls run.tcl

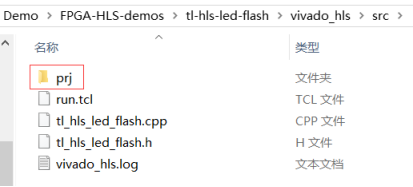

打印信息没有报errors,并提示Exiting vivado_hls则表示HLS工程生成成功。生成的工程当前目录下:

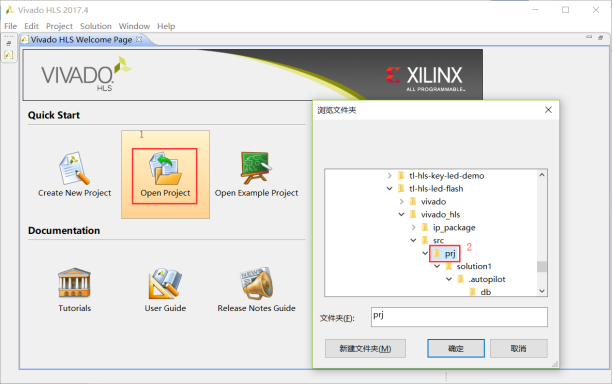

- 打开HLS工程

(2)点击Open Project打开prj工程。

打开成功:

创龙TLZ7xH-EVM是一款基于Xilinx Zynq-7000系列XC7Z035/XC7Z045/XC7Z100高性能SoC处理器设计的高端评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源,由核心板与底板组成。

ZYNQ Z-7045-C6678新伙伴

TLZ7xH-EVM评估板

芯片架构:XC7Z045/XC7Z100-2FFG900I,集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。PS端主频最高可达1GHz,单核运算能力高达2.5DMIPS/MHz。

外设资源:1x FMC(HPC)、2x CameraLink(Base/Medium/Full)、2x CAMERA、4x SFP+、1x PCIe Gen2、1x SATA、2x HDMI、2x SGMII

支持PS、PL端通信、高速AD采集与处理、CameraLink视频采集与处理

应用领域:雷达探测 目标追踪 电子对抗 定位导航 图像处理 水下探测 光电探测 深度学习

更多详情请查阅:

①官方网站

②官方商城

/4

/4